|

|

PDF M36W832TE Data sheet ( Hoja de datos )

| Número de pieza | M36W832TE | |

| Descripción | 32 Mbit 2Mb x16 / Boot Block Flash Memory and 8 Mbit 512Kb x16 SRAM / Multiple Memory Product | |

| Fabricantes | ST Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M36W832TE (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

M36W832TE

M36W832BE

32 Mbit (2Mb x16, Boot Block) Flash Memory

and 8 Mbit (512Kb x16) SRAM, Multiple Memory Product

FEATURES SUMMARY

s SUPPLY VOLTAGE

– VDDF = 2.7V to 3.3V

– VDDS = VDDQF = 2.7V to 3.3V

– VPPF = 12V for Fast Program (optional)

s ACCESS TIMES: 70ns and 85ns

s LOW POWER CONSUMPTION

s ELECTRONIC SIGNATURE

– Manufacturer Code: 20h

– Top Device Code, M36W832TE: 88BAh

– Bottom Device Code, M36W832BE: 88BBh

FLASH MEMORY

s 32 Mbit (2Mb x16) BOOT BLOCK

– 8 x 4 KWord Parameter Blocks (Top or

Bottom Location)

s PROGRAMMING TIME

– 10µs typical

– Double Word Programming Option

– Quadruple Word Programming Option

s BLOCK LOCKING

– All blocks locked at Power up

– Any combination of blocks can be locked

– WPF for Block Lock-Down

s AUTOMATIC STANDBY MODE

s PROGRAM and ERASE SUSPEND

s 100,000 PROGRAM/ERASE CYCLES per

BLOCK

s COMMON FLASH INTERFACE

s SECURITY

– 128 bit user programmable OTP cells

– 64 bit unique device identifier

Figure 1. Packages

FBGA

Stacked LFBGA66 (ZA)

12 x 8mm

SRAM

s 8 Mbit (512Kb x 16)

s ACCESS TIME: 70ns

s LOW VDDS DATA RETENTION: 1.5V

s POWER DOWN FEATURES USING TWO

CHIP ENABLE INPUTS

May 2003

1/64

1 page

M36W832TE, M36W832BE

Table 31. Device Geometry Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 32. Primary Algorithm-Specific Extended Query Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 33. Security Code Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

APPENDIX C. FLASH MEMORY FLOWCHARTS and PSEUDO CODES . . . . . . . . . . . . . . . . . . . . . 53

Figure 26. Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 27. Double Word Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 28. Quadruple Word Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 29. Program Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . 56

Figure 30. Erase Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 31. Erase Suspend & Resume Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 32. Locking Operations Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 33. Protection Register Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . 60

APPENDIX D. FLASH MEMORY COMMAND INTERFACE and PROGRAM/ERASE CONTROLLER

STATE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 34. Write State Machine Current/Next, sheet 1 of 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 35. Write State Machine Current/Next, sheet 2 of 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 36. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5/64

5 Page

M36W832TE, M36W832BE

Flash Memory Component

The Flash Memory is a 32 Mbit (2 Mbit x 16) device

that can be erased electrically at block level and

programmed in-system on a Word-by-Word basis.

These operations can be performed using a single

low voltage (2.7 to 3.6V) supply. VDDQF allows to

drive the I/O pin down to 1.65V. An optional 12V

VPPF power supply is provided to speed up cus-

tomer programming.

The device features an asymmetrical blocked ar-

chitecture with an array of 71 blocks: 8 Parameter

Blocks of 4 KWords and 63 Main Blocks of 32

KWords. The M36W832TE has the Parameter

Blocks at the top of the memory address space

while the M36W832BE locates the Parameter

Blocks starting from the bottom. The memory

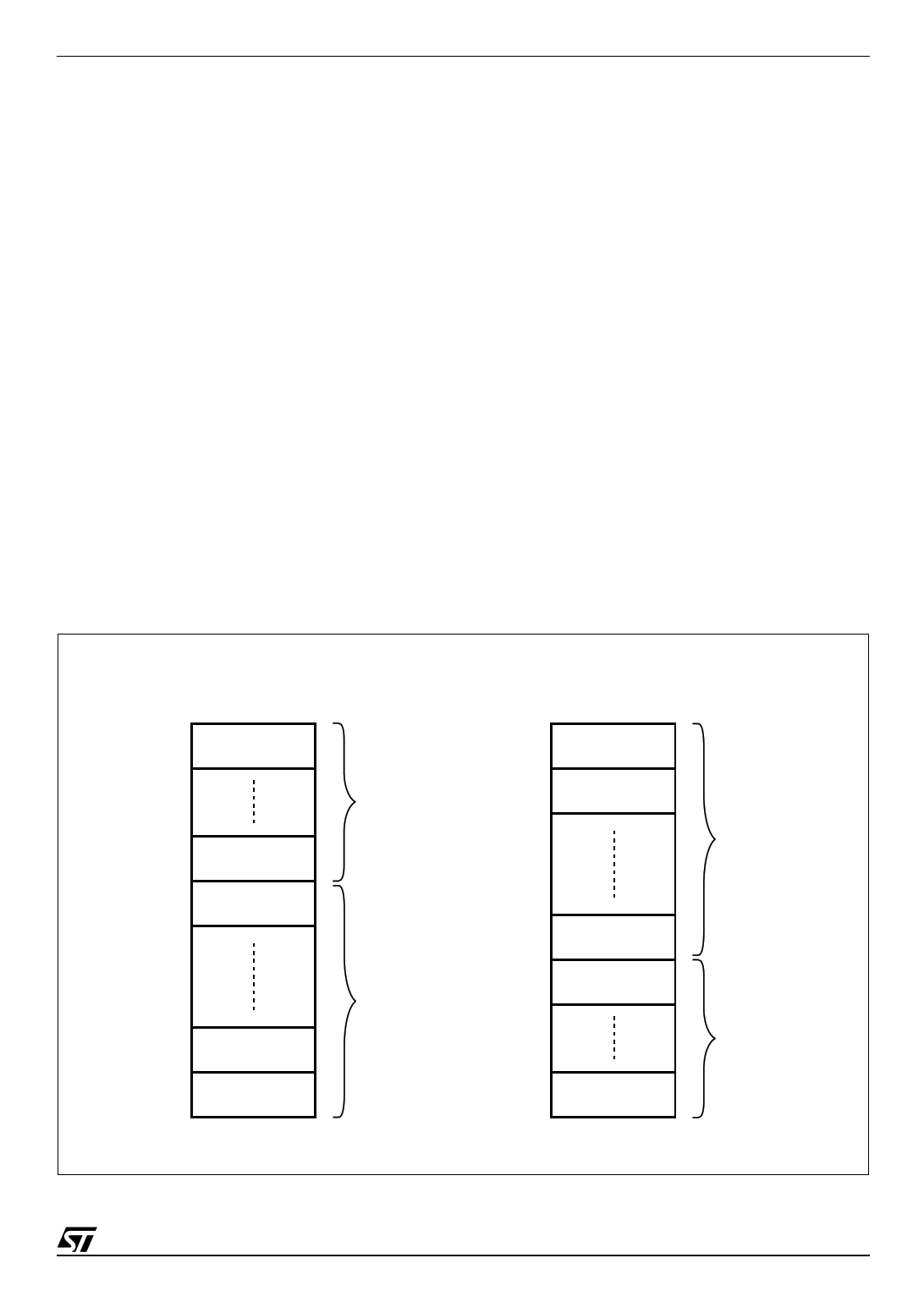

maps are shown in Figure 5, Block Addresses.

The Flash Memory features an instant, individual

block locking scheme that allows any block to be

locked or unlocked with no latency, enabling in-

stant code and data protection. All blocks have

three levels of protection. They can be locked and

locked-down individually preventing any acciden-

tal programming or erasure. There is an additional

hardware protection against program and erase.

When VPPF ≤ VPPLK all blocks are protected

Figure 5. Flash Block Addresses

against program or erase. All blocks are locked at

Power Up.

Each block can be erased separately. Erase can

be suspended in order to perform either read or

program in any other block and then resumed.

Program can be suspended to read data in any

other block and then resumed. Each block can be

programmed and erased over 100,000 cycles.

The device includes a Protection Register to in-

crease the protection of a system design. The Pro-

tection Register is divided into two segments, the

first is a 64 bit area which contains a unique device

number written by ST, while the second is a 128 bit

area, one-time-programmable by the user. The

user programmable segment can be permanently

protected. Figure 6, shows the Flash Security

Block and Protection Register Memory Map.

Program and Erase commands are written to the

Command Interface of the memory. An on-chip

Program/Erase Controller takes care of the tim-

ings necessary for program and erase operations.

The end of a program or erase operation can be

detected and any error conditions identified. The

command set required to control the memory is

consistent with JEDEC standards.

Top Boot Block Addresses

Bottom Boot Block Addresses

1FFFFF

1FF000

4 KWords

1F8FFF

1F8000

1F7FFF

1F0000

4 KWords

32 KWords

00FFFF

008000

007FFF

000000

32 KWords

32 KWords

Total of 8

4 KWord Blocks

1FFFFF

1F8000

1F7FFF

1F0000

32 KWords

32 KWords

Total of 63

32 KWord Blocks

00FFFF

008000

007FFF

007000

32 KWords

4 KWords

000FFF

000000

4 KWords

Note: Also see Appendix A, Tables 26 and 27 for a full listing of the Flash Block Addresses.

Total of 63

32 KWord Blocks

Total of 8

4 KWord Blocks

AI90164

11/64

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet M36W832TE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M36W832TE | 32 Mbit 2Mb x16 / Boot Block Flash Memory and 8 Mbit 512Kb x16 SRAM / Multiple Memory Product | ST Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |