|

|

PDF MAX100 Data sheet ( Hoja de datos )

| Número de pieza | MAX100 | |

| Descripción | 250Msps / 8-Bit ADC with Track/Hold | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX100 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

19-0282; Rev 0; 7/94

EVAALVUAAILTAIOBNLEKIT

250Msps, 8-Bit ADC with Track/Hold

_______________General Description ____________________________Features

The MAX100 ECL-compatible, 250Msps, 8-bit analog-to-

digital converter (ADC) allows accurate digitizing of ana-

log signals from DC to 125MHz (Nyquist frequency).

Designed with Maxim’s proprietary advanced bipolar

processes, the MAX100 contains a high-performance

track/hold (T/H) amplifier and a quantizer in a single

ceramic strip-line package.

The innovative design of the internal T/H assures an

exceptionally wide input bandwidth of 1.2GHz and aper-

ture delay uncertainty of less than 2ps, resulting in a high

6.8 effective bits performance. Special comparator output

design and decoding circuitry reduce out-of-sequence

code errors. The probability of erroneous codes occurring

due to metastable states is reduced to less than 1 error

per 1015 clock cycles. Unlike other ADCs, which can

have errors that result in false full-scale or zero-scale out-

puts, the MAX100 keeps the magnitude to less than 1LSB.

o 250Msps Conversion Rate

o 6.8 Effective Bits at 125MHz

o Less than ±1/2LSB INL

o 50Ω Differential or Single-Ended Inputs

o ±270mV Input Signal Range

o Reference Sense Inputs

o Ratiometric Reference Inputs

o Configurable Dual-Output Data Paths

o Latched, ECL-Compatible Outputs

o Low Error Rate, Less than 10-15 Metastable States

o Selectable On-Chip 8:16 Demultiplexer

o 84-Pin Ceramic Flat Pack

________________________Applications

The analog input is designed for either differential or single-

ended use with a ±270mV range. Sense pins for the refer-

ence input allow full-scale calibration of the input range or

facilitate ratiometric use. Midpoint tap for the reference

string is available for applications that need to modify the

output coding for a user-defined bilinear response. Use of

separate high-current and low-current ground pins pro-

vides better noise immunity and highest device accuracy.

High-Speed Digital Instrumentation

High-Speed Signal Processing

Medical Systems

Radar/Sonar

High-Energy Physics

Communications

Dual output data paths provide several data output modes ______________Ordering Information

for easy interfacing. These modes can be configured as

either one or two identical latched ECL outputs. An 8:16

demultiplexer mode that reduces the output data rates to

one-half the clock rate is also available.

PART TEMP. RANGE

PIN-PACKAGE

MAX100CFR* 0°C to +70°C 84 Ceramic Flat Pack (with heatsink)

For applications that require faster data rates, refer to

*Contact factory for 84-Pin Ceramic Flat Pack without heatsink.

Maxim’s MAX101, which allows conversion rates up to

5_00_M__sp_s_.___________________________________________________Functional Diagram

VART VARTS

AIN+

AIN- TRACK/

HOLD

CLK

CLK

VACT VACTS

FLASH CONVERTER

VARBS VARB

88

MODE

CONTROL

8

MOD DIV A=B

L

A

T

C

H

E

S

B

U

F

F

E

R

L

A

T

C

H

E

S

AData

(A0–A7)

DCLK

DCLK

BData

(B0–B7)

________________________________________________________________ Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free literature.

1 page

250Msps, 8-Bit ADC with Track/Hold

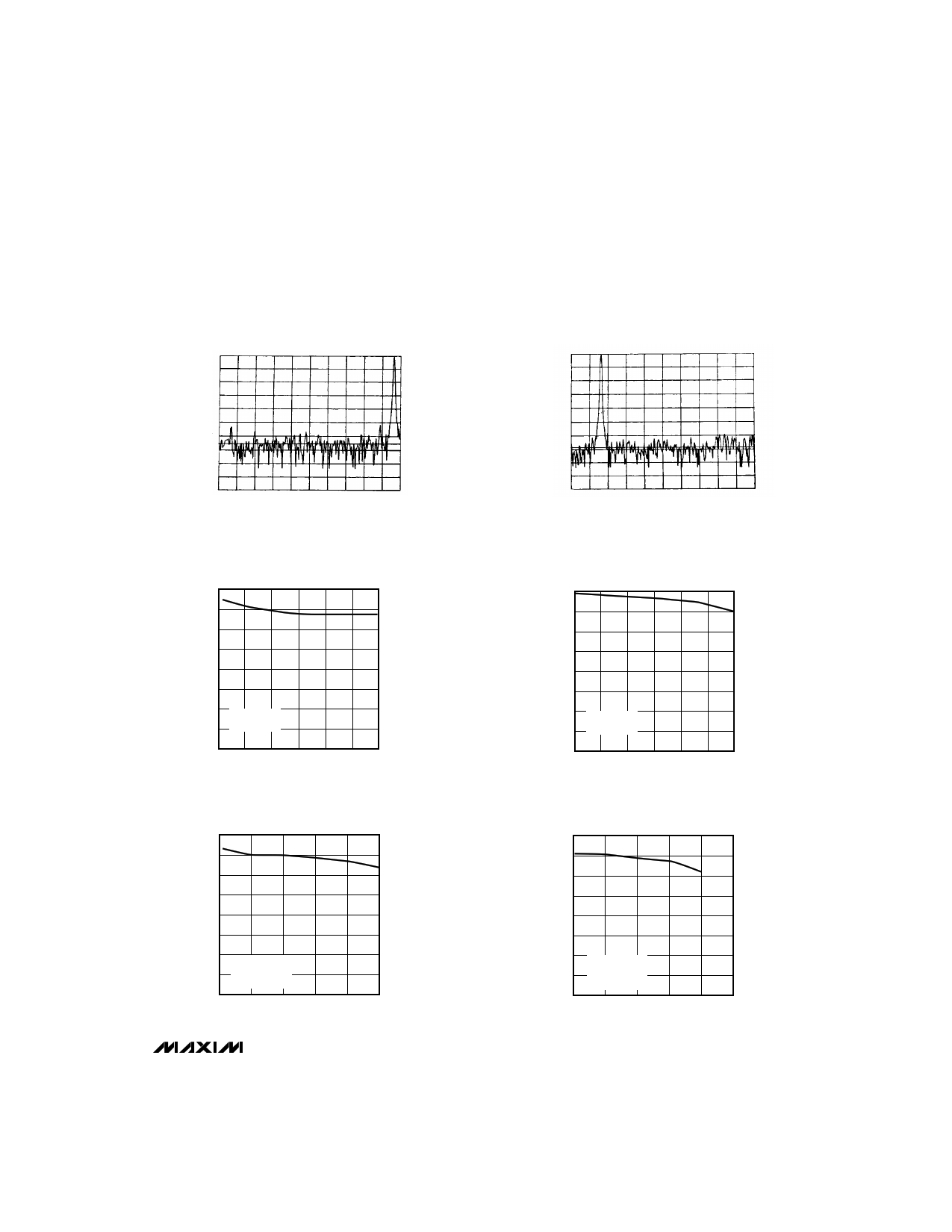

____________________________Typical Operating Characteristics (continued)

(TA = +25°C, unless otherwise noted.)

FFT PLOT (fAIN = 120.4462MHz)

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

0 12.5 25 37.5 50 62.5 75 87.5 100 112.5 125

FREQUENCY (MHz)

fCLK = 250MHz, fAIN = 120.4462MHz

SER = -42.3dB, NOISE FLOOR = -65.4dB

EFFECTIVE BITS

vs. ANALOG INPUT FREQUENCY

8

7

6

5

4

3

2 fCLK = 250MHz,

1 VIN = 95% FS

0

0 50 100 150 200

fAIN (MHz)

250 300

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

0

FFT PLOT (fAIN = 10.4462MHz)

12.5 25 37.5 50

FREQUENCY (MHz)

fCLK = 250MHz, fAIN = 10.4462MHz

SER = -45.87dB, NOISE FLOOR = -68.5dB

62.5

EFFECTIVE BITS

vs. CLOCK FREQUENCY

8

7

6

5

4

3

2 fAIN = 10.4MHz,

1 VIN = 95% FS

0

0 50 100 150 200

fCLK (MHz)

250 300

EFFECTIVE BITS

vs. ANALOG INPUT FREQUENCY

8

7

6

5

4

3

2

TCASE = +80°C,

1 fCLK = 250MHz,

VIN = 95% FS

0

0 50 100 150 200 250

fAIN (MHz)

EFFECTIVE BITS

vs. ANALOG INPUT FREQUENCY

8

7

6

5

4

3

2 TCASE = -15°C,

1

fCLK = 250MHz

VIN = 95% FS

0

0 50 100 150 200 250

fAIN (MHz)

_______________________________________________________________________________________ 5

5 Page

250Msps, 8-Bit ADC with Track/Hold

_______________Detailed Description

Converter Operation

The parallel or “flash” architecture used by the MAX100

provides the fastest multibit conversion of all common

integrated ADC designs. The basic element of a flash

(as with all other ADC architectures) is the comparator,

which has a positive input, a negative input, and an

output. If the voltage at the positive input is higher than

the negative input (connected to a reference), the out-

put will be high. If the positive input voltage is lower

than the reference, the output will be low. A typical n-

bit flash consists of 2n-1 comparators with negative

inputs evenly spaced at 1LSB increments from the bot-

tom to the top of the reference ladder. For n = 8, there

will be 255 comparators.

For any input voltage, all the comparators with negative

inputs connected to the reference ladder below the

input voltage will have outputs of 1, and all compara-

tors with negative inputs above the input voltage will

have outputs of 0. Decode logic is provided to convert

this information into a parallel n-bit digital word (the out-

put) corresponding to the number of LSBs (minus 1)

that the input voltage is above the level set at the bot-

tom of the ladder.

Finally, the comparators contain latch circuitry and are

clocked. This allows the comparators to function as

described above when, for example, clock is low.

When clock goes high (samples) the comparator will

latch and hold its state until the clock goes low again.

Track/Hold

As with all ADCs, if the input waveform is changing

rapidly during the conversion the effective bits and

SNR will decrease. The MAX100 has an internal

track/hold (T/H) that increases attainable effective-bits

performance and allows more accurate capture of ana-

log data at high conversion rates.

The internal T/H circuit provides two important circuit

functions for the MAX100:

1) Its nominal voltage gain of 4 reduces the input dri-

ving signal to ±270mV differential (assuming a

±1.02V reference).

2) It provides a differential 50Ω input that allows easy

interface to the MAX100.

Data Flow

The MAX100 contains an internal T/H amplifier that

stores the analog input voltage for the ADC to convert.

The differential inputs AIN+ and AIN- are tracked con-

tinuously between data samples. When a negative CLK

edge is applied, the T/H enters hold mode (Figure 5).

When CLK goes low, the most recent sample is pre-

sented to the ADC’s input comparators. Internal pro-

cessing of the sampled data is delayed for several

clock cycles before it is available at outputs AData or

BData. All output data is timed with respect to DCLK

and DCLK (Figures 1–4).

__________Applications Information

Analog Input Ranges

Although the normal operating range is ±270mV, the

MAX100 can be operated with up to ±500mV on each

input with respect to ground. This extended input level

includes the analog signal and any DC common-mode

voltage.

To obtain a full-scale digital output with differential input

drive, a nominal +270mV must be applied between

AIN+ and AIN-. That is, AIN+ = +135mV and AIN- =

-135mV (with no DC offset). Mid-scale digital output

code occurs when there is no voltage difference across

the analog inputs. Zero-scale digital output code, with

differential -270mV drive, occurs when AIN+ = -135mV

and AIN- = +135mV. Table 2 shows how the output of

the converter stays at all ones (full scale) when over

ranged or all zeros (zero scale) when under ranged.

For single-ended operation:

1) Apply a DC offset to one of the analog inputs, or

leave one input open. (Both AIN+ and AIN- are ter-

minated internally with 50Ω to analog ground.)

2) Drive the other input with a ±270mV + offset to

obtain either full- or zero-scale digital output. If a DC

common-mode offset is used, the total voltage swing

allowed is ±500mV (analog signal plus offset with

respect to ground).

Table 1. Input Voltage Range

INPUT

AIN+**

(mV)

Differential

Single

Ended

+135

0

-135

+270

0

-270

AIN-**

(mV)

-135

0

+135

0

0

0

OUTPUT

CODE

11111111

10000000

00000000

11111111

10000000

00000000

MSB to LSB

full scale

mid scale

zero scale

full scale

mid scale

zero scale

**An offset VIO, as specified in the DC electrical parameters, may

be present at the input. Compensate for this offset by either

adjusting the reference voltage (VART or VARB), or introducing an

offset voltage in one of the input terminals AIN + or AIN-.

______________________________________________________________________________________ 11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet MAX100.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX100 | 250Msps / 8-Bit ADC with Track/Hold | Maxim Integrated |

| MAX1002 | Low-Power / 60Msps / Dual / 6-Bit ADC | Maxim Integrated |

| MAX1003 | Low-Power / 90Msps / Dual 6-Bit ADC | Maxim Integrated |

| MAX1005 | IF Undersampler | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |