|

|

PDF MACH435Q-20JC Data sheet ( Hoja de datos )

| Número de pieza | MACH435Q-20JC | |

| Descripción | High-Density EE CMOS Programmable Logic | |

| Fabricantes | Lattice | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MACH435Q-20JC (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

FINAL

COM’L: -12/15/20, Q-20/25

MACH435-12/15/20, Q-20/25

High-Density EE CMOS Programmable Logic

Lattice Semiconductor

DISTINCTIVE CHARACTERISTICS

s 84 Pins in PLCC

s 128 Macrocells

s 12 ns tPD

s 83.3 MHz fCNT

s 70 Inputs with pull-up resistors

s 64 Outputs

s 192 Flip-flops

— 128 Macrocell flip-flops

— 64 Input flip-flops

s Up to 20 product terms per function, with XOR

GENERAL DESCRIPTION

The MACH435 is a member of our high-performance

EE CMOS MACH 4 family. This device has approxi-

mately twelve times the macrocell capability of the

popular PAL22V10, with significant density and func-

tional features that the PAL22V10 does not provide.

The MACH435 consists of eight PAL blocks intercon-

nected by a programmable central switch matrix. The

central switch matrix connects the PAL blocks to each

other and to all input pins, providing a high degree of

connectivity between the fully-connected PAL blocks.

This allows designs to be placed and routed efficiently.

Routability is further enhanced by an input switch matrix

and an output switch matrix. The input switch matrix

provides input signals with alternative paths into the

central switch matrix; the output switch matrix provides

flexibility in assigning macrocells to I/O pins.

The MACH435 has macrocells that can be configured

as synchronous or asynchronous. This allows designers

to implement both synchronous and asynchronous logic

s Flexible clocking

— Four global clock pins with selectable edges

— Asynchronous mode available for each

macrocell

s 8 “PAL33V16” blocks

s Input and output switch matrices for high

routability

s Fixed, predictable, deterministic delays

s Pin compatible with MACH130, MACH131,

MACH230, and MACH231

together on the same device. The two types of design

can be mixed in any proportion, since the selection on

each macrocell affects only that macrocell.

Up to 20 product terms per function can be assigned. It

is possible to allocate some product terms away from a

macrocell without losing the use of that macrocell for

logic generation.

The MACH435 macrocell provides either registered or

combinatorial outputs with programmable polarity. If a

registered configuration is chosen, the register can be

configured as D-type, T-type, J-K, or S-R to help reduce

the number of product terms used. The flip-flop can also

be configured as a latch. The register type decision can

be made by the designer or by the software.

All macrocells can be connected to an I/O cell through

the output switch matrix. The output switch matrix

makes it possible to make significant design changes

while minimizing the risk of pinout changes.

Publication# 17469 Rev. E Amendment /0

Issue Date: May 1995

1 page

FUNCTIONAL DESCRIPTION

The MACH435 consists of eight PAL blocks connected

by a central switch matrix. There are 64 I/O pins and 6

dedicated input pins feeding the central switch matrix.

These signals are distributed to the eight PAL blocks for

efficient design implementation. There are 4 global

clock pins that can also be used as dedicated inputs.

All inputs and I/O pins have built-in pull-up resistors.

While it is always good design practice to tie unused

pins high, the pull-up resistors provide design security

and stability in the event that unused pins are left

disconnected.

The PAL Blocks

Each PAL block in the MACH435 (Figure 1) contains a

clock generator, a 90-product-term logic array, a logic

allocator, 16 macrocells, an output switch matrix, 8 I/O

cells, and an input switch matrix. The central switch

matrix feeds each PAL block with 33 inputs. This makes

the PAL block look effectively like an independent

“PAL33V16” with 8 to 16 buried macrocells.

In addition to the logic product terms, individual output

enable product terms and two PAL block initialization

product term are provided. Each I/O pin can be

individually enabled. All flip-flops that are in the

synchronous mode within a PAL block are initialized

together by either of the PAL block initialization product

terms.

The Central Switch Matrix and Input

Switch Matrix

The MACH435 central switch matrix is fed by the input

switch matrices in each PAL block. Each PAL block

provides 16 internal feedback signals, 8 registered input

signals, and 8 I/O pin signals to the input switch matrix.

Of these 32 signals, 24 decoded signals are provided to

the central switch matrix by the input switch matrix. The

central switch matrix distributes these signals back to

the PAL blocks in a very efficient manner that provides

for high performance. The design software automati-

cally configures the input and central switch matrices

when fitting a design into the device.

The Clock Generator

Each PAL block has a clock generator that can generate

four clock signals for use throughout the PAL block.

These four signals are available to all macrocells and

I/O cells in the PAL block, whether in synchronous or

asynchronous mode. The clock generator chooses the

four signals from the eight possible signals given by the

true and complement versions of the four global clock

pin signals.

The Product-Term Array

The MACH435 product-term array consists of 80

product terms for logic use, eight product terms for

output enable use, and two product terms for global PAL

block initialization. Each macrocell has a nominal

allocation of 5 product terms for logic, although the logic

allocator allows for logic redistribution. Each I/O pin has

its own individual output enable term. The initialization

product terms provide asynchronous reset or preset to

synchronous-mode macrocells in the PAL block.

The Logic Allocator

The logic allocator in the MACH435 takes the 80 logic

product terms and allocates them to the 16 macrocells

as needed. Each macrocell can be driven by up to 20

product terms if in synchronous mode, or 18 product

terms if in asynchronous mode. When product terms are

routed away from a macrocell, it is possible to route all 5

product terms away, which precludes the use of the

macrocell for logic generation; or it is possible to route

only 4 product terms away, leaving one for simple

function generation. The design software automatically

configures the logic allocator when fitting the design into

the device.

The logic allocator also provides an exclusive-OR gate.

This gate allows generation of combinatorial exclusive-

OR logic, such as comparison or addition. It allows

registered exclusive-OR functions, such as CRC gen-

eration, to be implemented more efficiently. It also

makes in possible to emulate all flip-flop types with a

D-type flip-flop. Register type emulation is automatically

handled by the design software.

Table 1 illustrates which product term clusters are

available to each macrocell within a PAL block. Refer to

Figure 1 for cluster and macrocell numbers.

MACH435-12/15/20, Q-20/25

5

5 Page

ABSOLUTE MAXIMUM RATINGS

Storage Temperature . . . . . . . . . . . –65°C to +150°C

Ambient Temperature

with Power Applied . . . . . . . . . . . . . –55°C to +125°C

Supply Voltage with

Respect to Ground . . . . . . . . . . . . . –0.5 V to +7.0 V

DC Input Voltage . . . . . . . . . . . . –0.5 V to VCC +0.5 V

DC Output or

I/O Pin Voltage . . . . . . . . . . . . . –0.5 V to VCC +0.5 V

Static Discharge Voltage . . . . . . . . . . . . . . . . . 2001 V

Latchup Current (TA = 0°C to +70°C) . . . . . . 200 mA

Stresses above those listed under Absolute Maximum Ratings

may cause permanent device failure. Functionality at or above

these limits is not implied. Exposure to Absolute Maximum

Ratings for extended periods may affect device reliability.

Programming conditions may differ.

OPERATING RANGES

Commercial (C) Devices

Temperature (TA) Operating

in Free Air . . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

Supply Voltage (VCC) with

Respect to Ground . . . . . . . . . . . . +4.75 V to +5.25 V

Operating ranges define those limits between which the func-

tionality of the device is guaranteed.

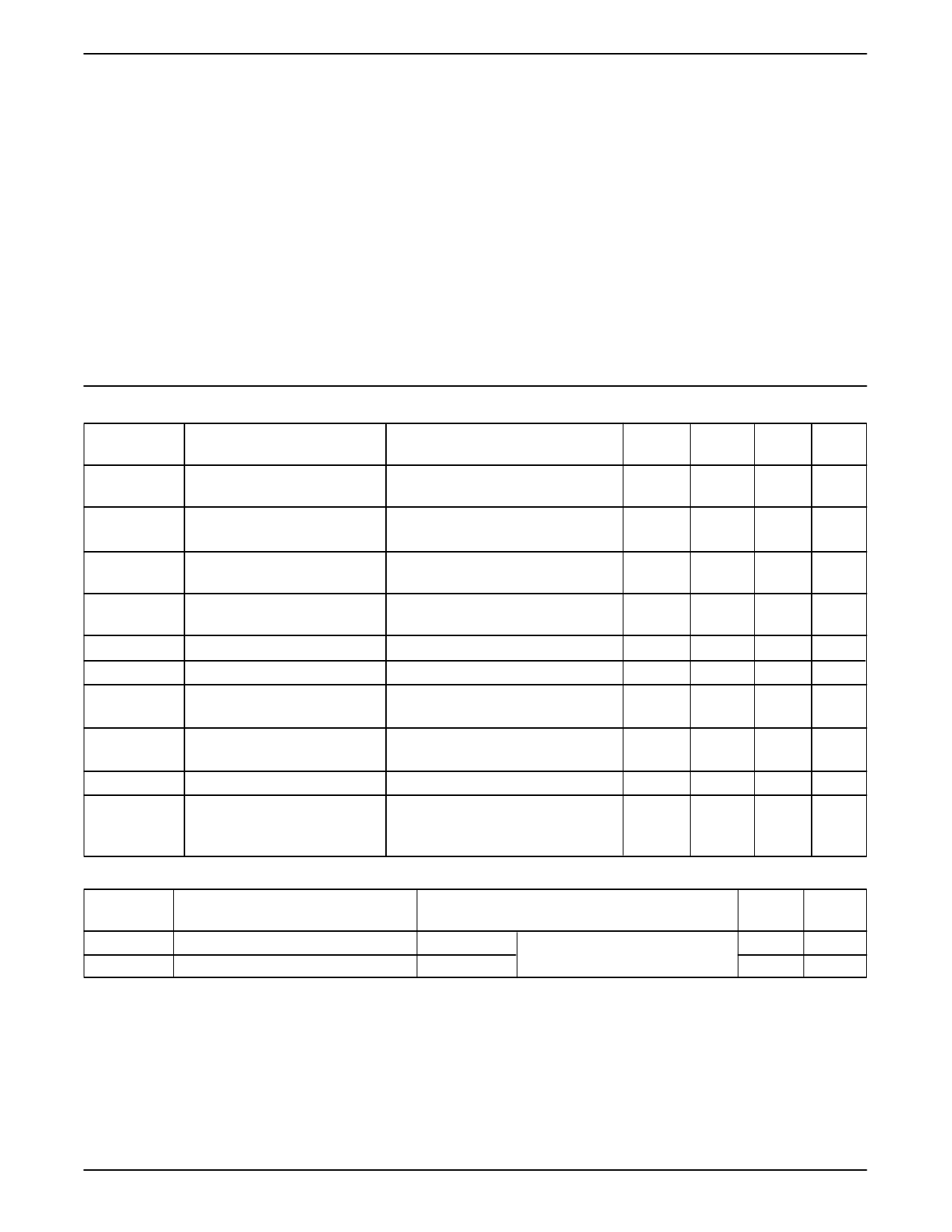

DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

Parameter

Symbol

Parameter Description

Test Conditions

Min Typ Max Unit

VOH Output HIGH Voltage

IOH = –3.2 mA, VCC = Min

VIN = VIH or VIL

2.4

V

VOL Output LOW Voltage

IOL = 24 mA, VCC = Min

VIN = VIH or VIL (Note 1)

0.5 V

VIH Input HIGH Voltage

Guaranteed Input Logical HIGH

Voltage for all Inputs (Note 2)

2.0

V

VIL Input LOW Voltage

Guaranteed Input Logical LOW

Voltage for all Inputs (Note 2)

0.8 V

IIH Input HIGH Leakage Current VIN = 5.25 V, VCC = Max (Note 3)

10 µA

IIL Input LOW Leakage Current VIN = 0 V, VCC = Max (Note 3)

–100 µA

IOZH Off-State Output Leakage VOUT = 5.25 V, VCC = Max

Current HIGH

VIN = VIH or VIL (Note 3)

10 µA

IOZL Off-State Output Leakage VOUT = 0 V, VCC = Max

Current LOW

VIN = VIH or VIL (Note 3)

–100 µA

ISC

Output Short-Circuit Current VOUT = 0.5 V, VCC = Max (Note 4)

–30

–160 mA

ICC Supply Current

VIN = 0 V, Outputs Open

(IOUT = 0 mA), VCC = 5.0 V,

f =25 MHz, TA = 25°C (Note 5)

255 mA

CAPACITANCE (Note 6)

Parameter

Symbol

Parameter Description

Test Conditions

Typ Unit

CIN Input Capacitance

VIN = 2.0 V

VCC = 5.0 V, TA = 25°C,

6 pF

COUT

Output Capacitance

VOUT = 2.0 V f = 1 MHz

8 pF

Notes:

1. Total IOL for one PAL block should not exceed 128 mA.

2. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

3. I/O pin leakage is the worst case of IIL and IOZL(or IIH and IOZH).

4. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

VOUT= 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

5. Measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL Block and capable of being loaded,

enabled, and reset. An actual ICCvalue can be calculated by using the “Typical Dynamic ICCCharacteristics” Chart towards the

end of this data sheet.

6. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified

where capacitance may be affected.

MACH435-15/20 (Com’l)

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MACH435Q-20JC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MACH435Q-20JC | High-Density EE CMOS Programmable Logic | Lattice |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |