|

|

PDF MA28151 Data sheet ( Hoja de datos )

| Número de pieza | MA28151 | |

| Descripción | Radiation hard Programmable Communication Interface | |

| Fabricantes | Dynex | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MA28151 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

Replaces Jone 1999 version, DS3574-4.0

MAM2A821815511

Radiation hard Programmable

Communication Interface

DS3574-5.0 January 2000

The MA28151 is based on the industry standard 8251A

Universal Synchronous Asynchronous Receiver/Transmitter

(USART), modified for data communications with the MAS281

microprocessor.

The MA28151 is used as a peripheral device and is

programmed by the CPU to operate using virtually any serial

data transmission technique presently in use (including IBM

“bi-sync”). The USART accepts data characters from the CPU

in parallel format and then converts them into a continuous

serial data stream for transmission.

Simultaneously, it can receive serial data streams and

convert them into parallel data characters for the CPU. The

USART signals the CPU whenever it receives a character for

transmission or whenever it receives a character for the CPU.

The CPU can read the complete status of the USART at any

time, including data transmission errors and control signals

such as SYNDET and TxEMPTY.

FEATURES

s Radiation Hard to 1MRad(Si)

s Latch Up Free, High SEU Immunity

s Silicon-on-Sapphire Technology

s Synchronous 5 - 8 Bit Characters; Internal or External

Character Synchronisation; Automatic Sync Insertion

s Asynchronous 5 - 8 Bit Characters; Clock Rate - 1, 16 or

64 Times Baud Rate; Break Character Generation, 1 1⁄2 or

2 Stop Bits

s All Inputs and Outputs are TTL Compatible

s Compatible with the MAS281 (MIL-STD-1750A)

Microprocessor

Figure 1: MA28151 Block Diagram

The MA28151 is based on the industry standard 8251A

USART, modified for use with the MAS281 processor,

incorporating the following features:

1. MA28151 has double-buffered data paths with separate l/O

registers for control status, data in and data out, which

considerably simplifies control programming and minimizes

CPU overhead.

2. In synchronous operations, the Receiver detects and

handles “break” automatically, relieving the CPU of this task.

3. A refined Rx initialisation prevents the Receiver from

starting when in the “break” state, preventing unwanted

interrupts from the disconnected USART.

4. At the conclusion of a transmission, the TxD line will always

return to the marking state unless SBRK is programmed.

5. Tx Enable logic enhancement prevents a Tx Disable

command from prematurely halting transmission of the

previously written data before completion. The logic also

prevents the transmitter from turning off in the middle of a

word.

6. When external Sync Detect is programmed, Internal Sync

Detect is disabled and an External Sync Detect status is

provided via a flip-flop, which clears itself upon a status read.

7. The possibility of a false sync detect is minimized in two

ways: by ensuring that if double character sync is

programmed, the characters will be continuously detected and

by clearing the Rx register to all 1’s whenever Enter-Hunt

command is issued in Sync mode.

8. When the MA28151 is not selected, the RDWN and DSN

lines do not affect the internal operation of the device.

9. The MA28151 Status can be read at any time but the status

update will be inhibited during status read.

10. The MA28151 is free from extraneous glitches, providing

higher speed and better operating margins.

11. Synchronous Baud rate is from DC to 64K.

12. Asynchronous Baud rate is from DC to 19.2K.

1/22

1 page

MA28151

3. PROGRAMMING THE MA28151

3.1 MODE AND COMMAND INSTRUCTIONS

Prior to starting data transmission or reception, the

MA28151 must be loaded with a set of control words

generated by the CPU. These control signals define the

complete functional definition of the MA28151 and must

immediately follow a Reset operation (internal or external).

3.3 TEST MODE

The Mode Instruction can be used to select a scan path

test facility. In this mode a test vector is read in through RxD

and read out in TxD. For further information of test mode

please contact GEC Plessey Semiconductors.

The control words are split into two formats:

1. Mode Instruction

2. Command Instruction

3.1.1 Mode Instruction

This instruction defines the general operational

characteristics of the MA28151. It must follow a Reset

operation (internal or external). Once the Mode instruction has

been written into the MA28151 by the CPU, SYNC characters

or Command Instructions may be written.

3.1.2 Command Instruction

This instruction defines a word that is used to control the

actual operation of the MA28151.

Both the Mode and Command Instruction must conform to

a specified sequence for proper device operation. The Mode

instruction must be written immediately following a Reset

operation, prior to using the MA28151 for data

communications.

All control words written into the MA28151 after the Mode

Instruction will load the Command Instruction. Command

Instructions can be written into the MA28151 at any time in the

data block during the operation of the MA28151. To return to

the Mode Instruction format, the master Reset bit in the

Command Instruction word can be set to initiate an internal

Reset operation. This automatically places the MA28151 back

into the Mode Instruction format. Command Instructions must

follow the Mode Instructions or Sync characters.

3.2 MODE INSTRUCTION DEFINITION

The MA28151 can be used for either Asynchronous or

Synchronous data communications. To understand how the

Mode Instruction defines the functional operation of the

MA28151, the designer can best view the device as two

separate components, one Asynchronous and the other

Synchronous, sharing the same package. The format

definition can be changed only after a master chip Reset. For

explanation purposes the two formats will be isolated.

NOTE: When parity is enabled it is not considered as one

of the data bits for the purpose of programming the word

length. The actual parity bit received on the Rx Data line

cannot be read on the Data Bus. In the case of a programmed

character length of less than 8 bits, the least significant data

bus bits will hold the data; unused bits are ‘don’t care’ when

writing data to the MA28151, and will be zeros when reading

the data from the MA28151.

3.4 ASYNCHRONOUS MODE (TRANSMISSION)

Whenever a data character is sent by the CPU the

MA28151 automatically adds a Start bit (low level), followed by

the data bits (least significant bit first,) and the programmed

number of Stop bits to each character. Also, an even or odd

Parity bit is inserted prior to the Stop bit(s), as defined by the

Mode Instruction. The Character is then transmitted as a serial

data stream on the TxD output. The serial data is shifted out on

the falling edge of TxC at a rate equal to 1, 1⁄16 or 1⁄64 times that

of the TxC, as defined by the Mode Instruction. BREAK

characters can be continuously sent to the TxD if commanded

to do so.

When no data characters have been loaded into the

MA28151 the TxD output remains high (marking) unless a

Break (continuously low) has been programmed.

3.5 ASYNCHRONOUS MODE (RECEIVE)

The RxD line is normally high. A falling edge on this line

triggers the beginning of a START bit. The validity of this

START bit is checked by again strobing this bit at its nominal

center (16x or 64X mode only). If a low is detected again, it is a

valid START bit, and the bit counter will start counting. The bit

counter thus locates the center of the data bits, the parity bit (if

it exists) and the stop bits. If a parity error occurs, the parity

error flag is set. Data and parity bits are sampled on the RxD

pin with the rising edge of RxC. If a low level is detected as the

STOP bit, the Framing Error flag will be set. The STOP bit

signals the end of a character. Note that the receiver requires

only one stop bit, regardless of the number of stop bits

programmed. This character is then loaded into the parallel l/O

buffer of the MA28151. The RxRDY pin is raised to signal the

CPU that a character is ready to be fetched.

If a previous character has not been fetched by the CPU,

the present character replaces it in the l/O buffer, and the

OVERRUN Error flag is raised (thus the previous character is

lost). All of the error flags can be reset by an Error Reset

Instruction. The occurrence of any of these errors will not affect

the operation of the MA28151.

5/22

5 Page

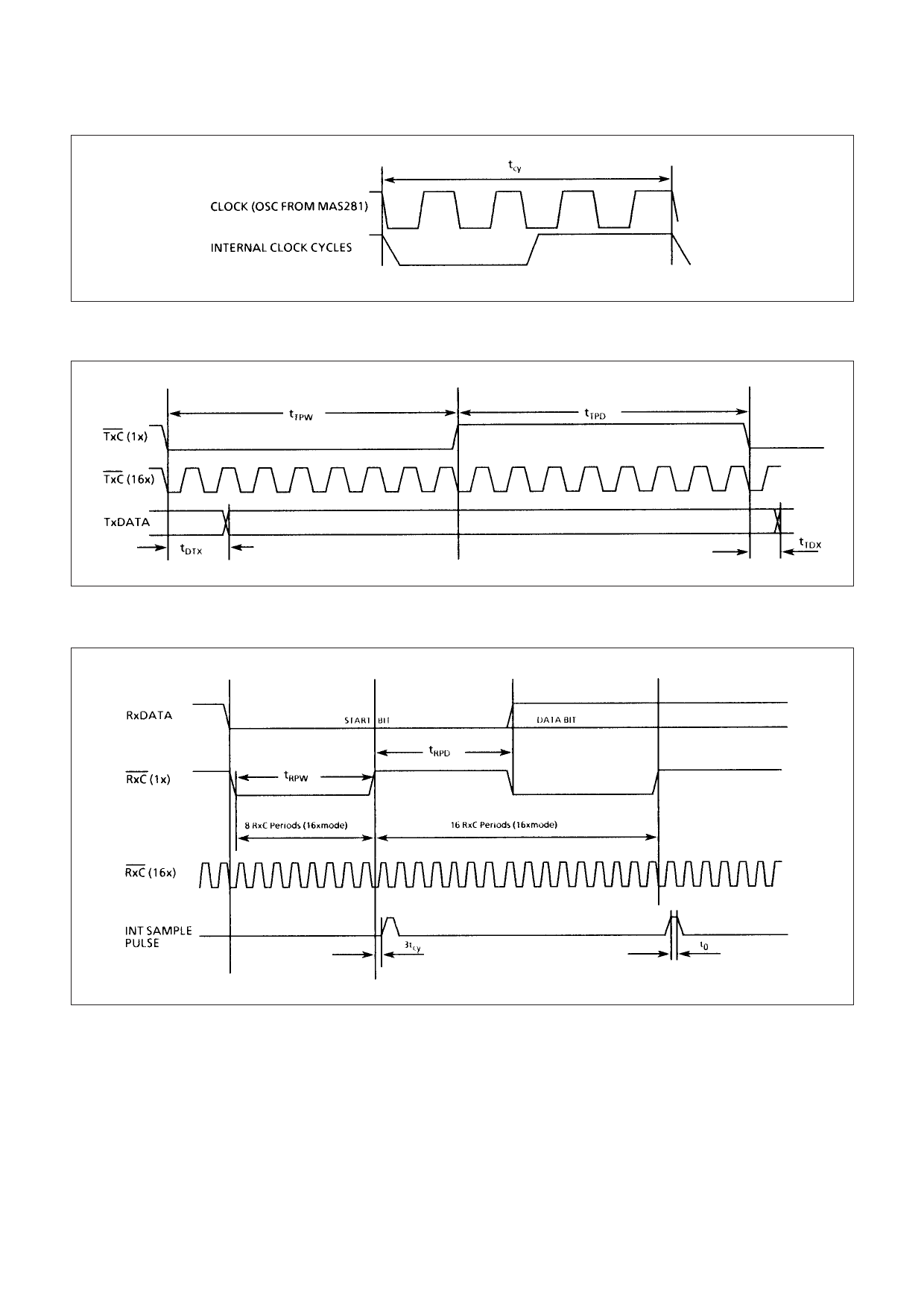

4. TIMING WAVEFORMS

Figure 14: System Clock Input

MA28151

Figure 15: Transmitter Clock and Data

Figure 16: Receive Clock and Data

11/22

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet MA28151.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MA28151 | Radiation hard Programmable Communication Interface | Dynex |

| MA28155 | Radiation Hard Programmable Peripheral Interface | Dynex |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |