|

|

PDF M5M5T5636UG-20 Data sheet ( Hoja de datos )

| Número de pieza | M5M5T5636UG-20 | |

| Descripción | 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM | |

| Fabricantes | Mitsubishi | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M5M5T5636UG-20 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

January 14, 2003 Rev.0.7

Preliminary

Notice: This is not final specification.

Some parametric limits are subject to change.

DESCRIPTION

The M5M5T5636UG is a family of 18M bit synchronous SRAMs

organized as 524288-words by 36-bit. It is designed to eliminate

dead bus cycles when turning the bus around between reads

and writes, or writes and reads. Mitsubishi's SRAMs are

fabricated with high performance, low power CMOS technology,

providing greater reliability. M5M5T5636UG operates on 2.5V

power/ 1.8V I/O supply or a single 2.5V power supply and are

2.5V CMOS compatible.

FEATURES

• Fully registered inputs and outputs for pipelined operation

• Fast clock speed: 250, 225, and 200 MHz

• Fast access time: 2.6, 2.8, 3.2 ns

• Single 2.5V -5% and +5% power supply VDD

• Separate VDDQ for 2.5V or 1.8V I/O

• Individual byte write (BWa# - BWd#) controls may be tied

LOW

• Single Read/Write control pin (W#)

• CKE# pin to enable clock and suspend operations

• Internally self-timed, registers outputs eliminate the need

to control G#

• Snooze mode (ZZ) for power down

• Linear or Interleaved Burst Modes

• Three chip enables for simple depth expansion

• JTAG boundary scan support

MITSUBISHI LSIs

M5M5T5636UG – 25,22,20

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

APPLICATION

High-end networking products that require high bandwidth, such

as switches and routers.

FUNCTION

Synchronous circuitry allows for precise cycle control

triggered by a positive edge clock transition.

Synchronous signals include : all Addresses, all Data Inputs,

all Chip Enables (E1#, E2, E3#), Address Advance/Load (ADV),

Clock Enable (CKE#), Byte Write Enables (BWa#, BWb#, BWc#,

BWd#) and Read/Write (W#). Write operations are controlled by

the four Byte Write Enables (BWa# - BWd#) and Read/Write(W#)

inputs. All writes are conducted with on-chip synchronous

self-timed write circuitry.

Asynchronous inputs include Output Enable (G#), Clock (CLK)

and Snooze Enable (ZZ). The HIGH input of ZZ pin puts the

SRAM in the power-down state.The Linear Burst order (LBO#) is

DC operated pin. LBO# pin will allow the choice of either an

interleaved burst, or a linear burst.

All read, write and deselect cycles are initiated by the ADV

LOW input. Subsequent burst address can be internally

generated as controlled by the ADV HIGH input.

Package

165(11x15) bump BGA

Body Size (13mm x 15mm)

Bump Pitch 1.0mm

PART NAME TABLE

Part Name

M5M5T5636UG - 25

Access

2.6ns

Cycle

4.0ns

Active Current

(max.)

560mA

Standby Current

(max.)

30mA

M5M5T5636UG - 22 2.8ns

4.4ns

500mA

30mA

M5M5T5636UG - 20 3.2ns

5.0ns

440mA

30mA

1/24

Preliminary

M5M5T5636UG REV.0.7

1 page

MITSUBISHI LSIs

M5M5T5636UG – 25,22,20

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

DC OPERATED TRUTH TABLE

Name

Input Status

Operation

LBO#

HIGH or NC

LOW

Interleaved Burst Sequence

Linear Burst Sequence

Note4. LBO# is DC operated pin.

Note5. NC means No Connection.

Note6. See BURST SEQUENCE TABLE about interleaved and Linear Burst Sequence.

BURST SEQUENCE TABLE

Interleaved Burst Sequence (when LBO# = HIGH or NC)

Operation

A18~A2

First access, latch external address

A18~A2

Second access(first burst address)

latched A18~A2

Third access(second burst address)

latched A18~A2

Fourth access(third burst address)

latched A18~A2

Linear Burst Sequence (when LBO# = LOW)

Operation

A18~A2

First access, latch external address

A18~A2

Second access(first burst address)

Third access(second burst address)

latched A18~A2

latched A18~A2

Fourth access(third burst address)

latched A18~A2

Note7. The burst sequence wraps around to its initial state upon completion.

0,0

0,1

1,0

1,1

A1,A0

0,1

1,0

0,0

1,1

1,1

0,0

1,0

0,1

1,1

1,0

0,1

0,0

0,0

0,1

1,0

1,1

A1,A0

0,1

1,0

1,0

1,1

1,1

0,0

0,0

0,1

1,1

0,0

0,1

1,0

TRUTH TABLE

Address

E1# E2 E3# ZZ

ADV

W#

BWx#

G#

CKE# CLK

DQ

used

Operation

H X X L L X X X L L->H High-Z None Deselect Cycle

X L X L L X X X L L->H High-Z None Deselect Cycle

X X H L L X X X L L->H High-Z None Deselect Cycle

X X X L H X X X L L->H High-Z None Continue Deselect Cycle

L H L L L H X L L L->H Q External Read Cycle, Begin Burst

X X X L H X X L L L->H Q Next Read Cycle, Continue Burst

L H L L L H X H L L->H High-Z External NOP/Dummy Read, Begin Burst

X X X L H X X H L L->H High-Z Next Dummy Read, Continue Burst

L H L L L L L X L L->H D External Write Cycle, Begin Burst

X X X L H X L X L L->H D Next Write Cycle, Continue Burst

L H L L L L H X L L->H High-Z None NOP/Write Abort, Begin Burst

X X X L H X H X L L->H High-Z Next Write Abort, Continue Burst

XX X L X X

X

X

H L->H

-

Current Ignore Clock edge, Stall

X X X H X X X X X X High-Z None Snooze Mode

Note8. “H” = input VIH; “L” = input VIL; “X” = input VIH or VIL.

Note9. BWx#=H means all Synchronous Byte Write Enables (BWa#,BWb#,BWc#,BWd#) are HIGH. BWx#=L means one or more

Synchronous Byte Write Enables are LOW.

Note10. All inputs except G# and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

5/24

Preliminary

M5M5T5636UG REV.0.7

5 Page

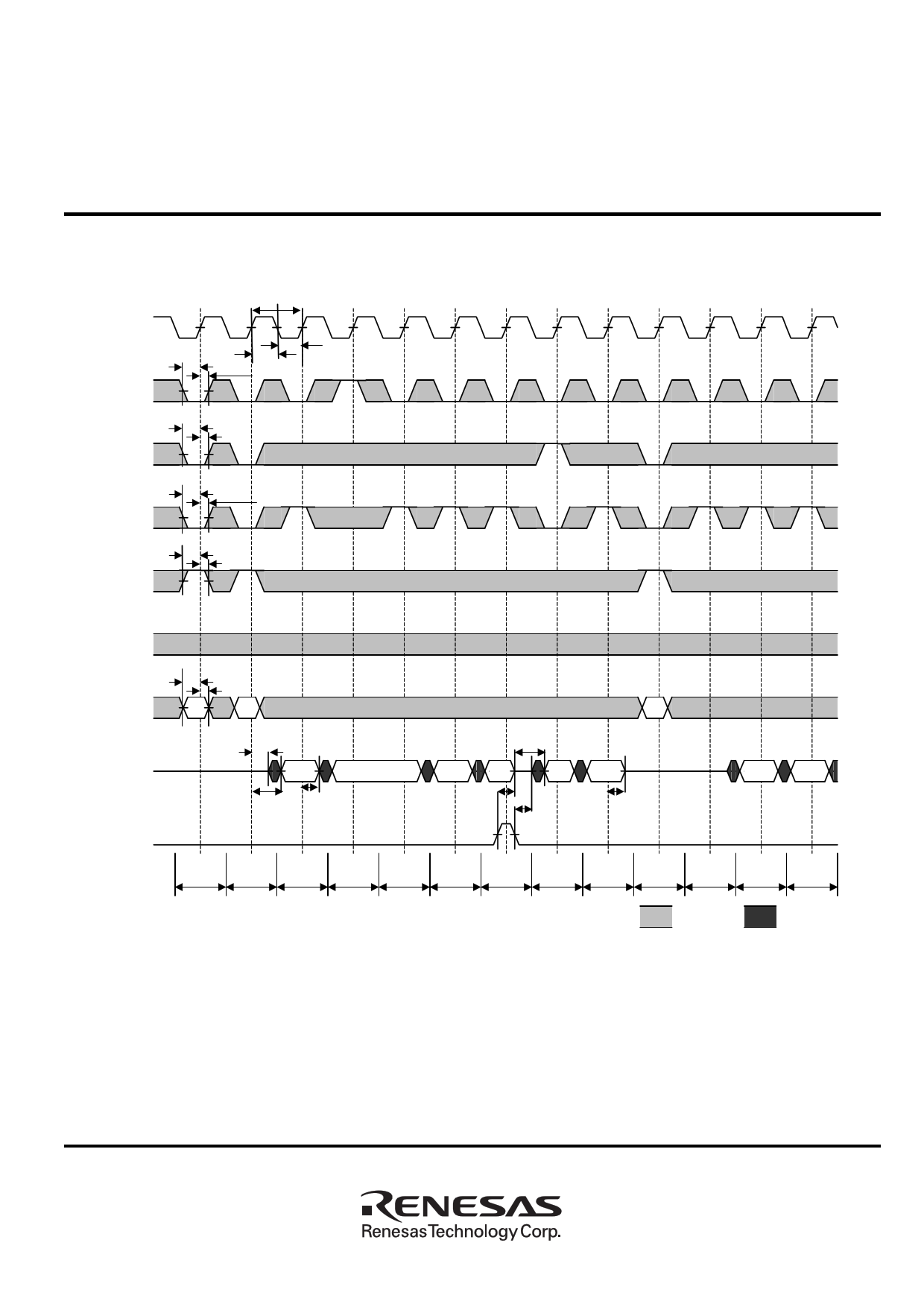

(3)READ TIMING

MITSUBISHI LSIs

M5M5T5636UG – 25,22,20

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

CLK

tckeVKH

CKE#

tEVKH

E#

tadvVKH

ADV

tWVKH

W#

tKHKH

tKHKL

tKHckeX

tKLKH

tKHEX

tKHadvX

tKHWX

BWx#

tAVKH

tKHAX

ADD A1 A2

A3

DQ

G#

tKHQX1

Q(A1)

tKHQV tKHQX

Q(A2)

tGLQV

Q(A2+1)

Q(A2+2)

tGHQZ

Q(A2+3)

tGLQX1

Q(A2)

tKHQZ

Q(A3)

Q(A3+1)

Read A1 Read A2 Burst Read Stall Burst Read Burst Read Burst Read Deselect Continue Read A3 Burst Read Burst Read Burst Read

A2+1

A2+2

A2+3

A2

Deselect

A3+1

A3+2

A3+3

DON'T CARE

UNDEFINED

Note29.Q(An) refers to output from address An. Q(An+1) refers to output from the next internal burst address following An.

Note30. E# represents three signals. When E# is LOW, it represents E1# is LOW, E2 is HIGH and E3# is LOW.

Note31.ZZ is fixed LOW.

11/24

Preliminary

M5M5T5636UG REV.0.7

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet M5M5T5636UG-20.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M5M5T5636UG-20 | 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM | Mitsubishi |

| M5M5T5636UG-22 | 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM | Mitsubishi |

| M5M5T5636UG-25 | 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM | Mitsubishi |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |