|

|

PDF M5M417400CTP-7 Data sheet ( Hoja de datos )

| Número de pieza | M5M417400CTP-7 | |

| Descripción | FAST PAGE MODE 16777216-BIT (4194304-WORD BY 4-BIT) DYNAMIC RAM | |

| Fabricantes | Mitsubishi | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M5M417400CTP-7 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

MITSUBISHI LSIs

M5M417400CJ,TP-5,-6,-7,-5S,-6S,-7S

FAST PAGE MODE 16777216-BIT (4194304-WORD BY 4-BIT) DYNAMIC RAM

DESCRIPTION

This is a family of 4194304-word by 4-bit dynamic RAMS,

fabricated with the high performance CMOS process, and is ideal

for large-capacity memory systems where high speed, low power

dissipation, and low costs are essential.

The use of double-layer metal process combined with twin-well

CMOS technology and a single-transistor dynamic storage stacked

capacitor cell provide high circuit density at reduced costs.

Multiplexed address inputs permit both a reduction in pins and an

increase in system densities.

FEATURES

Type Name

M5M417400CXX-5,-5S

M5M417400CXX-6,-6S

M5M417400CXX-7,-7S

RAS

access

time

(max.ns)

50

60

70

CAS

access

time

(max.ns)

13

15

20

Address

access

time

(max.ns)

25

30

35

OE

access

time

(max.ns)

13

15

20

C ycle

time

(min.ns)

90

110

130

Power

dissipa-

tion

(typ.mW)

655

540

475

XX=J, TP

• Standard 26 pin SOJ, 26 pin TSOP

• Single 5V ± 10% supply

• Low stand-by power dissipation

5.5mW(Max) ..................................CMOS Input level

2.2mW (Max)* ...............................CMOS Input level

• Low operating power dissipation

M5M417400Cxx-5,-5S .................... 800.0mW (Max)

M5M417400Cxx-6,-6S .................... 660.0mW (Max)

M5M417400Cxx-7,-7S .................... 580.0mW (Max)

• Self refresh capability *

self refresh current ................................ 200.0 µ A(Max)

• Fast-page mode, Read-modify-write, RAS-only refresh

• CAS before RAS refresh, Hidden refresh capabilities

Early-write mode and OE to control output buffer impedance

• All inputs, output TTL compatible and low capacitance

• 2048 refresh cycles every 32ms (A0 ~ A10)

*Applicable to self refresh version (M5M417400CJ,TP-5S,-6S,

-7S :option) only

PIN DESCRIPTION

Pin name

A0 ~ A11

DQ1 ~ DQ4

RAS

CAS

W

OE

VCC

VSS

Function

Address inputs

Data inputs / outputs

Row address strobe input

Column address strobe input

Write control input

Output enable input

Power supply (+5V)

Ground (0V)

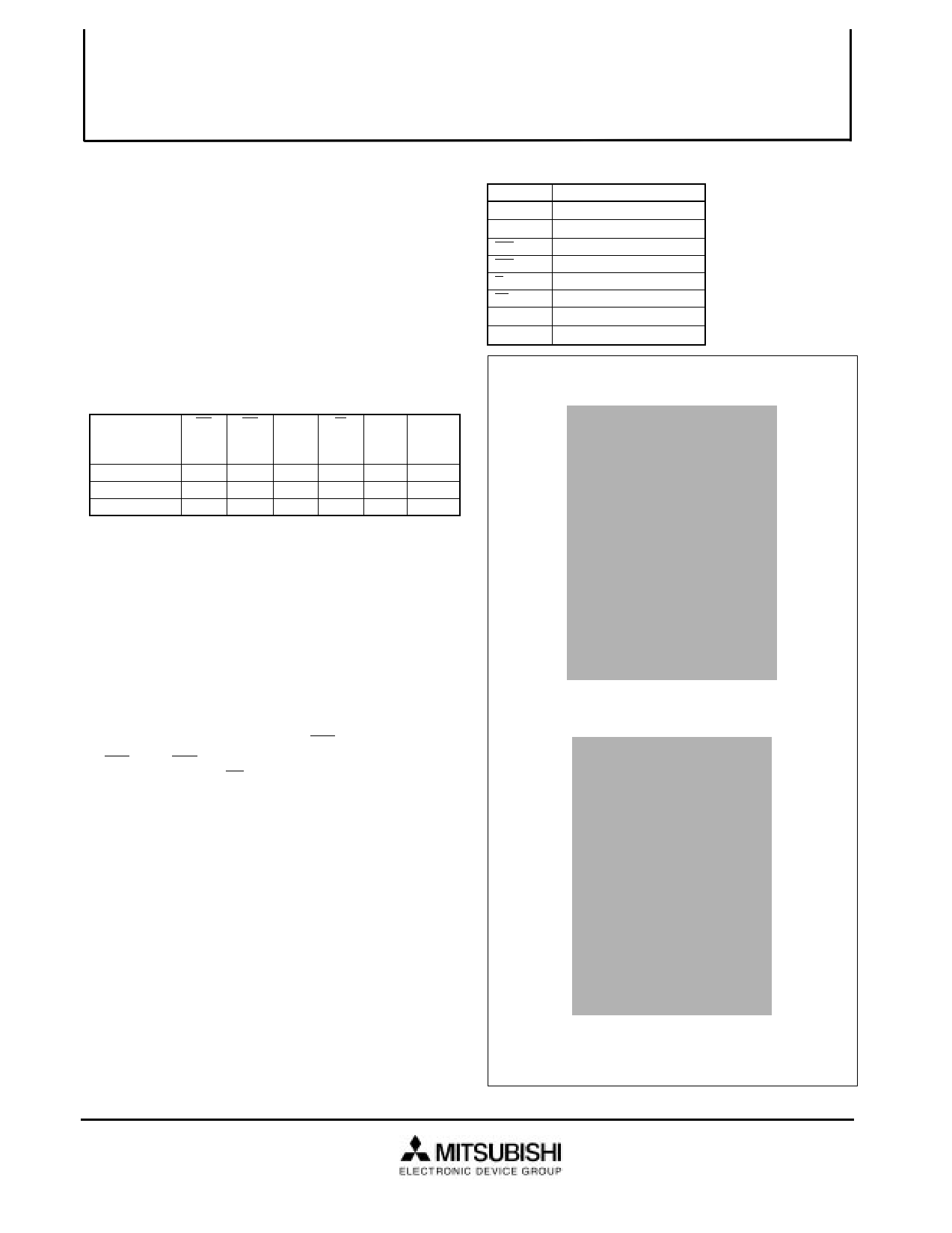

PIN CONFIGURATION (TOP VIEW)

Outline 26P0D-B (300mil SOJ)

APPLICATION

Main memory unit for computers, Microcomputer memory, Refresh

memory for CRT

Outline 26P3D-E (300mil TSOP)

NC: NO CONNECTION

1

1 page

MITSUBISHI LSIs

M5M417400CJ,TP-5,-6,-7,-5S,-6S,-7S

FAST PAGE MODE 16777216-BIT (4194304-WORD BY 4-BIT) DYNAMIC RAM

TIMING REQUIREMENTS (For Read, Write, Read-Modify-Write, Refresh, and Fast-Page Mode Cycles)

(Ta = 0 ~ 70°C, VCC = 5V ± 10%, VSS = 0V, unless otherwise noted. See notes 12, 13)

Limits

Symbol

Parameter

M5M417400C-5,-5S

M5M417400C-6,-6S

M5M417400C-7,-7S

Unit

Min Max Min Max Min Max

tREF

Refresh cycle time

32 32 32 ms

tRP RAS high pulse width

30 40 50 ns

tRCD

Delay time, RAS low to CAS low

(Note 14)

18

37

20

45

20

50 ns

tCRP

Delay time, CAS high to RAS low

10 10 10 ns

tRPC

Delay time, RAS high to CAS low

0 0 0 ns

tCPN

CAS high pulse width

10 10 10 ns

tRAD

Column address delay time from RAS low

(Note 15)

13

25

15

30

15

35 ns

tASR Row address setup time before RAS low

0

0

0 ns

tASC

Column address setup time before CAS low

(Note 16)

0

10

0

10

0

10 ns

tRAH

Row address hold time after RAS low

8 10 10 ns

tCAH

Column address hold time after CAS low

13

15

15 ns

tDZC

Delay time, data to CAS low

(Note 17)

0

0

0 ns

tDZO

Delay time, data to OE low

(Note 17)

0

0

0 ns

tCDD

Delay time, CAS high to data

(Note 18)

13

15

15 ns

tODD

Delay time, OE high to data

(Note 18)

13

15

15 ns

tT Transition time

(Note 19)

1

50

1

50

1

50 ns

Note 12:

13:

14:

15:

16:

17:

18:

19:

The timing requirements are assumed tT = 5ns.

VIH(min) and VIL(max) are reference levels for measuring timing of input signals.

tRCD(max) is specified as a reference point only. If tRCD is less than tRCD(max), access time is tRAC. If tRCD is greater than tRCD(max), access time is controlled exclusively by

tCAC or tAA. tRCD(min) is specified as tRCD(min) = tRAH(min) + 2tH + tASC(min).

tRAD(max) is specified as a reference point only. If tRAD ≥ tRAD(max) and tASC ≤ tASC(max), access time is controlled exclusively by tAA.

tASC(max) is specified as a reference point only. If tRCD ≥ tRCD(max) and tASC ≥ tASC(max), access time is controlled exclusively by tCAC.

Either tDZC or tDZO must be satisfied.

Either tCDD or tODD must be satisfied.

tT is measured between VIH(min) and VIL(max).

Read and Refresh Cycles

Symbol

Parameter

tRC

tRAS

Read cycle time

RAS low pulse width

tCAS

tCSH

tRSH

tRCS

tRCH

tRRH

tRAL

CAS low pulse width

CAS hold time after RAS low

RAS hold time after CAS low

Read setup time after CAS high

Read hold time after CAS low

Read hold time after RAS low

Column address to RAS hold time

(Note 20)

(Note 20)

tOCH

tORH

CAS hold time after OE low

RAS hold time after OE low

Note 20: Either tRCH or tRRH must be satisfied for a read cycle.

M5M417400C-5,-5S

Min Max

90

50 10000

13 10000

50

13

0

0

10

25

13

13

Limits

M5M417400C-6,-6S

Min Max

110

60 10000

15 10000

60

15

0

0

10

30

15

15

M5M417400C-7,-7S

Min Max

130

70 10000

20 10000

70

20

0

0

10

35

20

20

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

5

5 Page

Write Cycle (Early Write)

MITSUBISHI LSIs

M5M417400CJ,TP-5,-6,-7,-5S,-6S,-7S

FAST PAGE MODE 16777216-BIT (4194304-WORD BY 4-BIT) DYNAMIC RAM

11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet M5M417400CTP-7.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M5M417400CTP-5 | FAST PAGE MODE 16777216-BIT (4194304-WORD BY 4-BIT) DYNAMIC RAM | Mitsubishi |

| M5M417400CTP-5S | FAST PAGE MODE 16777216-BIT (4194304-WORD BY 4-BIT) DYNAMIC RAM | Mitsubishi |

| M5M417400CTP-6 | FAST PAGE MODE 16777216-BIT (4194304-WORD BY 4-BIT) DYNAMIC RAM | Mitsubishi |

| M5M417400CTP-6S | FAST PAGE MODE 16777216-BIT (4194304-WORD BY 4-BIT) DYNAMIC RAM | Mitsubishi |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |