|

|

PDF LC89201 Data sheet ( Hoja de datos )

| Número de pieza | LC89201 | |

| Descripción | 9600-bps Facsimile Modem | |

| Fabricantes | Sanyo | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LC89201 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

Ordering number : EN*4974

CMOS LSI

LC89201

9600-bps Facsimile Modem

Preliminary

Overview

The LC89201 is a CMOS single-chip, synchronous, half-

duplex, 9600-bps fax modem designed for use with public

telephone networks. Built in are such essential features for

Group III facsimile systems as modulator, demodulator,

transmission filters, and V.24 interface.

The LSI supports the V.29, V.27ter, V.21ch2, T.30, and

T.4 telecommunications standards promulgated by the

ITU-T (formerly the CCITT) for transmission at 9600,

7200, 4800, 2400 and 300 bps. Advanced signal

processing provides reliable data transmissions even under

adverse circuit conditions. Built-in High-level Data Link

Control (HDLC) support permits the construction of Error

Correction Mode (ECM) facsimile machines.

• Built-in eye pattern generator.

• Adaptive differential pulse-code modulation (ADPCM).

• Caller ID detection.

• Built-in diagnostics.

• Energy-saving CMOS design (typ. 250 mW).

• Single 5 V power supply.

• 80-pin flat package (QIP-80E).

Package Dimensions

unit: mm

3174-QFP80E

[LC89201]

Features

• Support for the following ITU-T standards: V.29 (9600,

7200 and 4800 bps), V.27ter (4800 and 2400 bps),

V.21ch2 (300 bps), T.30, and T.4.

• Half-duplex operation.

• Group III facsimile support.

• Automatic switching between high- (V.29 and V.27ter)

and low-speed (V.21ch2) incoming facsimiles.

• Short training (for ITU-T V.27ter only).

• HDLC framing and deframing (V.29, V.27ter, and

V.21ch2).

• Tone generation and detection.

• Dual-tone multifrequency (DTMF) generation and

detection.

• Call progress tone detection.

• Pseudo link back tone generation.

• Built-in automatic adaptive equalizer.

• Built-in fixed-amplitude amplifier.

— Link amplitude equalizer

— Cable amplitude equalizer

• Built-in transmission filters (digital filters).

• Programmable transmission level adjustment.

• Dynamic range for reception of 0 to –47 dBm.

• Programmable reception sensitivity adjustment.

• DTE interface.

— Serial interface (ITU-T V.24)

— Parallel interface (4 words × 8 bits, with built-in

FIFO)

• Programmable interrupt generator.

SANYO: QIP80E

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

92995HA (OT) No. 4974-1/8

1 page

LC89201

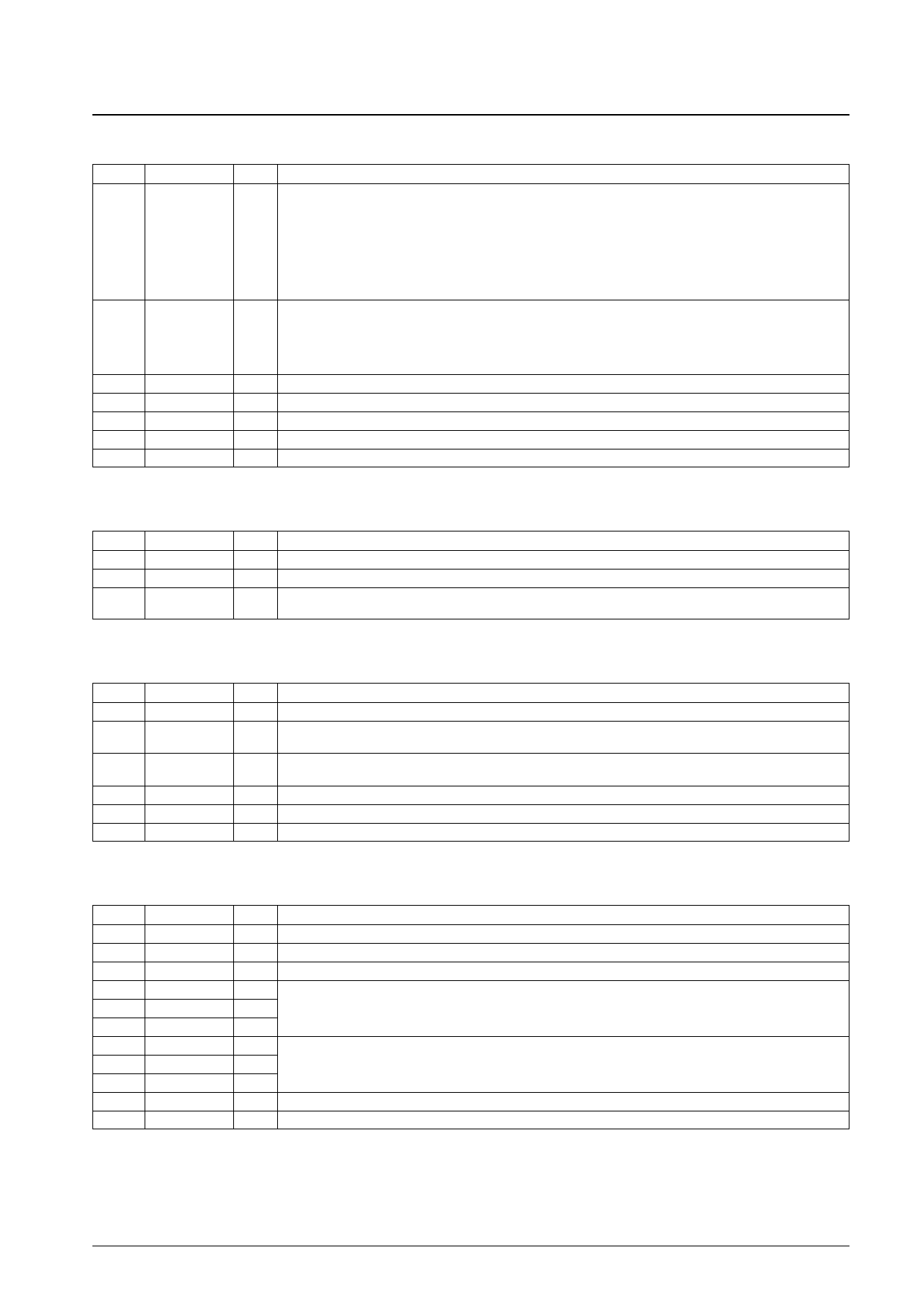

2. DTE Interface Pins

Pin No.

29

28

27

26

25

23

22

21

20

19

18

17

16

30

32

33

34

15

Symbol

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

CSB

READB

WRITEB

IREQB

RESETB

I/O

B Data bus to host CPU

I Address bus to host CPU

I Chip select signal

I Interface memory read signal

I Interface memory write signal

O Interrupt request to host CPU

I System reset signal

Function

3. Eye Pattern Interface Pins

Pin No.

67

68

66

65

Symbol

EYECLK

EYESYNC

EYEX

EYEY

I/O Function

O Timing clock for generating eye pattern data. This may be used as the shift clock for an external shift register.

O Eye pattern synchronization signal

O Eye pattern data serial outputs (8 bits, MSB first)

4. V.24 (RS-232C) Interface Pins

Pin No.

57

59

58

61

60

62

Symbol

RTSB

CTSB

RLSDB

TXD

RXD

DCLK

I/O Function

I Request to send signal. The low level at this pin starts transmission; the high level suspends it.

Clear to send signal. The low level at this pin signals the availability of data for transmission; the high level indicates

O that the data is invalid.

Received line signal data signal. The low level at this pin gives the timing for transferring the data received to the

O terminal.

I Transmit data input

O Receive data output

O Transmission data clock output

5. Analog Signal Pins

Pin No.

39

44

43

40

41

42

47

46

45

49

48

Symbol

TXA

RXA

AUXIN

OPA2P

OPA2M

OPA2O

OPA1P

OPA1M

OPA1O

PGCI

PGCO

I/O Function

O Transmitter analog output

I Receiver analog input

I Auxiliary analog input

I

I Transmission buffer input/output pins. (For details, see circuit diagram.)

O

I

I Reception buffer input/output pins (For details, see circuit diagram.)

O

I Reception gain adjustment circuit input. (For details, seecircuit diagram.)

O Reception gain adjustment circuit output.

No. 4974-5/8

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet LC89201.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LC8920 | FAX Modem | Sanyo |

| LC89201 | 9600-bps Facsimile Modem | Sanyo |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |