|

|

PDF LC6529L Data sheet ( Hoja de datos )

| Número de pieza | LC6529L | |

| Descripción | 4-Bit Microcomputer for Small-Scale Control Applications | |

| Fabricantes | Sanyo | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LC6529L (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Ordering number : EN*5117

Preliminary

CMOS LSI

LC6529N, LC6529F, LC6529L

4-Bit Microcomputer

for Small-Scale Control Applications

Overview

The LC6529N/F/L provides the basic architecture and

instruction set of the Sanyo LC6500 Series of 4-bit single-

chip microcomputers in a version specially for small-scale

control applications involving circuits built with standard

logic elements, applications using simple, comparator-

based voltage or phase detectors, or other applications

controlling a limited number of controls. The LC6529F is

a replacement for the former LC6529H. (Certain functions

differ, however.) The N (medium-speed) and L (power-

saving) versions are new additions to the lineup.

Features

• Power-saving CMOS design (Standby mode accessed

with HALT instruction included.)

• Memory: 1 kilobyte of 8-bit ROM and 64 words of 4-bit

RAM

• Instruction set: 51-member subset of LC6500 standard

complement of 80 instructions

• (L version) Wide range of operating voltages:

2.2 to 6.0 V

• (F version) 0.92 µs/3.0 V instruction cycle time

• Flexible I/O ports

Four ports with up to 16 lines

— Bidirectional I/O ports: 12

Dedicated input ports: 4 (These double as

comparator inputs.)

— I/O voltage limit: max. +15 V (open-drain

configuration)

— Output current: max. 20 mA sink current (capable of

directly driving an LED)

Choice of options to match system specifications

— Choice of open-drain or pull-up resistor output

configurations at the bit level for all ports

— Choice of reset output levels for Ports C and D in

groups of 4 bits each

Port E configurable as four comparator inputs

• Stack: Four levels

• Timers: 4-bit prescaler plus 8-bit programmable counter

• Comparators: 4 channels (2 reference levels)

Separator reference level for each channel pair

— Feedback resistor option for choice of input with or

without hysteresis

• Choice of clock oscillator options to match system

specifications

— Oscillator circuit options: 2-pin RC oscillator circuit

(N and L versions) or 2-pin ceramic oscillator circuit

(N, F, and L versions)

— Frequency divider options: Built-in 1/3 and 1/4

frequency dividers that eliminate the need for

external frequency dividers

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

92995HA (OT) No. 5117-1/39

1 page

LC6529N, LC6529F, LC6529L

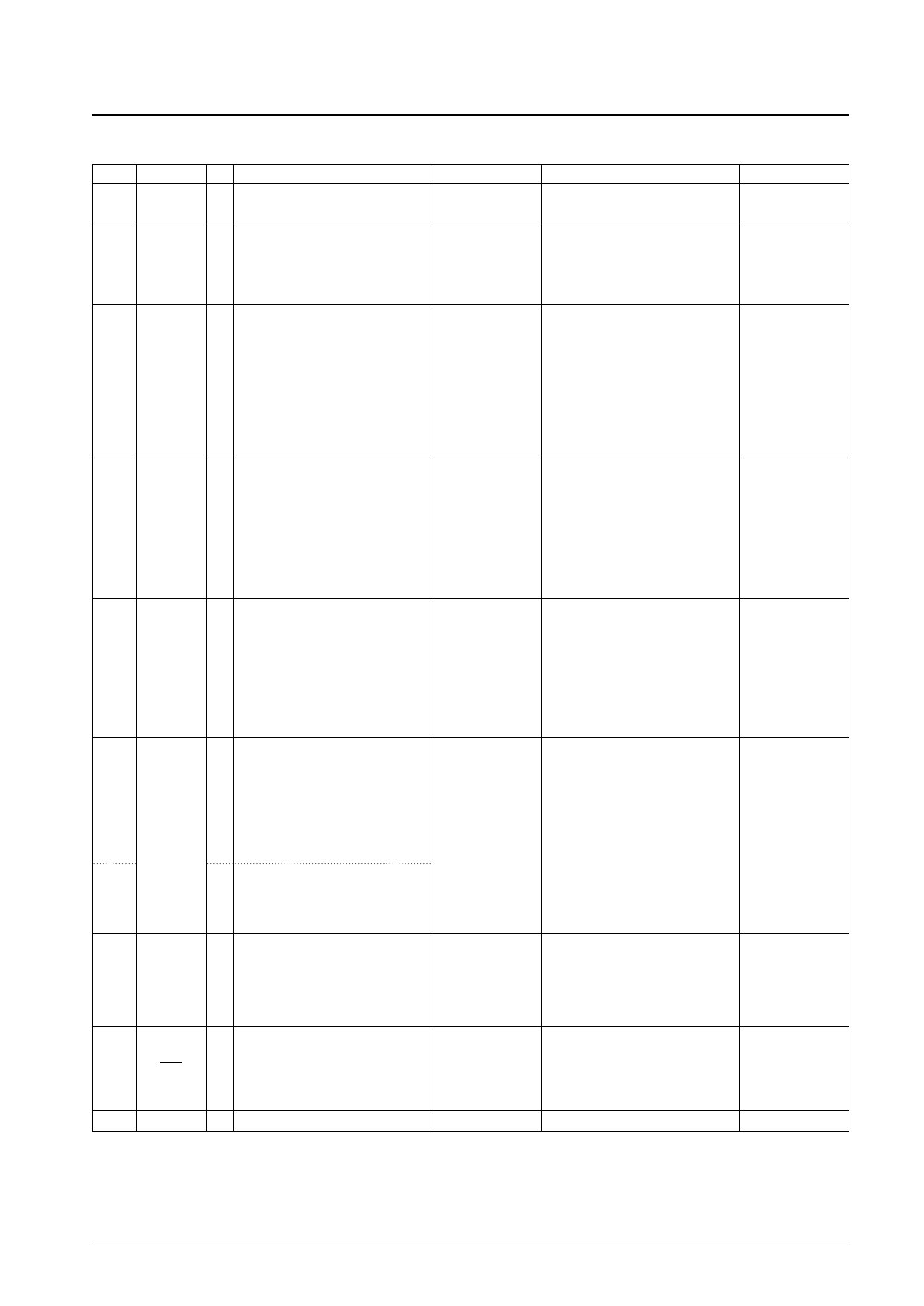

Pin Functions

Pin No.

1

1

Symbol

VDD

VSS

1 OSC1

1 OSC2

PA0

PA1

4

PA2

PA3

PC0

PC1

4

PC2

PC3

PD0

PD1

4

PD2

PD3

4 PE0/CMP0

PE1/CMP1

PE2/CMP2

PE3/CMP3

4

VREF0

2

VREF1

1 RES

1 TEST

I/O Function

Output driver type

Options

— Power supply. Normally +5 V.

—

— Power supply. 0 V.

—

I Pins for attaching external system

O clock oscillator circuit (RC or ceramic)

1. 2-pin RC oscillator circuit

(1-pin external clock)

2. 2-pin ceramic oscillator circuit

3. Frequency divider options:

1/1, 1/3, 1/4

• Bidirectional I/O port A0 to A3: 4-bit

input (IP instruction), 4-bit output (OP

instruction), 1-bit conditionals (BP

• N channel: sink

current type

and BNP instructions), 1-bit set and • I/O voltage limit for

1. Open-drain output

reset (SPB and RPB instructions)

open-drain

2. Pull-up resistor

I/O • PA3 also doubles as standby

operation control.

configuration: max.

+15 V

• Choice of configuration 1. or 2. at

bit level

• Block chattering from entering PA3

during the HALT instruction

execution cycle.

• P channel: high-

impedance pull-up

type

• Bidirectional I/O port C0 to C3.

Functions the same as PA0 to PA3

except that there is no the standby

I/O operation control.

• Option controls whether output is

high or low after reset.

• N channel: sink

current type

• I/O voltage limit for

open-drain

configuration: max.

+15 V

• P channel: low-

impedance pull-up

type

1. Open-drain output

2. Pull-up resistor

3. High output after reset

4. Low output after reset

• Choice of configuration 1. or 2. at

bit level

• Choice of configuration 3. or 4. at

port (4-bit) level

Bidirectional I/O port D0 to D3.

I/O Functions and options the same as

PC0 to PC3.

• N channel: sink

current type

• I/O voltage limit for

open-drain

configuration: max.

+15 V

• P channel: high-

impedance pull-up

type

1. Open-drain output

2. Pull-up resistor

3. High output after reset

4. Low output after reset

• Choice of configuration 1. or 2. at

bit level

• Choice of configuration 3. or 4. at

port (4-bit) level

• When configured for comparator

input: CMP0 and CMP1 use

reference voltage VREF0; CMP2 and

CMP3 use reference voltage VREF1.

I • 4-bit (CMP0 to 3) input (IP

instruction)

• 1-bit conditionals (BP and BNP

instructions)

• When configured for port E input:

I • 4-bit (E0-3) input (IP instruction)

• 1-bit conditionals (BP and BNP

instructions)

1. Comparator input

2. Port E input

3. Without feedback resistor

4. With feedback resistor

• Choice of configuration 1. or 2. at

port (4-bit) level

• Options 3. and 4. only available

with 1.

• Comparator reference level inputs:

CMP0 and CMP1 use reference

I

voltage VREF0; CMP2 and CMP3

use reference voltage VREF1.

• Connect to VSS when PE0/CMP0 to

PE3/CMP3 configured as port E.

• System reset input

• Connect external capacitor for power

I up reset.

• Low level input for a minimum of four

clock cycles triggers a reset.

I Chip test pin. Normally connect to VSS.

State after reset

—

—

High output (output

N channel transistor

off)

High or low (option)

High or low (option)

No. 5117-5/39

5 Page

LC6529N, LC6529F, LC6529L

Parameter

Symbol

Conditions

[Current drain]

RC oscillator

Ceramic oscillator

External clock

IDD OP1

IDD OP2

IDD OP3

IDD OP4

IDD OP5

IDD OP6

IDD OP7

IDD OP8

IDD OP9

IDD OP10

VDD: Figure 2, 850 kHz (typ)

VDD: Figure 2, 400 kHz (typ)

VDD: Figure 3, 4 MHz, 1/3 frequency divider

VDD: Figure 3, 4 MHz, 1/4 frequency divider

VDD: Figure 3, 2 MHz, 1/3 frequency divider

VDD: Figure 3, 2 MHz, 1/4 frequency divider

VDD: Figure 3, 800 kHz

VDD: Figure 3, 400 kHz

VDD: 200 to 667 kHz, 1/1 frequency divider,

600 to 2000 kHz, 1/3 frequency divider,

800 to 2667 kHz, 1/4 frequency divider

VDD: 200 to 1444 kHz, 1/1 frequency divider,

600 to 4330 kHz, 1/3 frequency divider,

800 to 4330 kHz, 1/4 frequency divider

Standby operation

IDD st1

IDD st2

[Oscillator characteristics] (RC oscillator)

VDD: With output N-channel transistor off and

port level = VDD, VDD = 6 V

VDD: With output N-channel transistor off and

port level = VDD, VDD = 3 V

Oscillator frequency

fMOSC

[Oscillator characteristics] (Ceramic oscillator)

OSC1, OSC2: Figure 2, Cext = 220 pF ± 5%,

Rext = 12.0 kΩ ± 1%

OSC1, OSC2: Figure 2, Cext = 220 pF ± 5%,

Rext = 4.7 kΩ ± 1%, VDD = 4 to 6 V

Oscillator frequency

fCFOSC*

Oscillator stabilization interval tCFS

OSC1, OSC2: Figure 3, fO = 400 kHz

OSC1, OSC2: Figure 3, fO = 800 kHz

OSC1, OSC2: Figure 3, fO = 2 MHz

OSC1, OSC2: Figure 3, fO = 4 MHz

Figure 4, fO = 400 kHz

Figure 4, fO = 800 kHz, fO = 2 MHz, fO = 4 MHz,

1/3, 1/4 frequency divider

[Pull-up resistors]

I/O ports

Reset port

External reset characteristic:

Reset time

RPP1

RPP2

Ru

tRST

Pull-up (PU) resistor configuration for port A or D:

With output N-channel transistor off and VIN = VSS,

VDD = 5 V

Pull-up (PU) resistor configuration for port C:

With output N-channel transistor off and VIN = VSS,

VDD = 5 V

RES: VIN = VSS, VDD = 5 V

Pin capacitance

CP

f = 1 MHz, VIN = VSS for pins other than one

being measured

Note: * fCFOSC is the allowable oscillator frequency.

min typ max Unit

0.8 2.0

mA

0.4 1.0

1.6 4.0

1.6 4.0

1.3 3.0

mA

1.3 3.0

1.1 2.6

0.9 2.4

1.0 2.5

mA

1.6 4.2

0.05

0.025

10

µA

5

309

660

384

768

1920

3840

400

850

400

800

2000

4000

577

1229

kHz

416

832

2080

4160

10

10

kHz

ms

30 70 130

kΩ

1.0 2.3 3.9

200 500

See

Figure 6.

725

10 pF

Comparator Characteristics for Comparator Option at Ta = –40 to +85°C, VSS = 0 V, VDD = 3.0 to 6.0 V

Parameter

Reference input voltage range

Inphase input voltage range

Offset voltage

Response speed

Input high level current

Input low level current

Feedback resistor

Symbol

VRFIN

VCMIN

VOFF

TRS1

TRS2

IIH1

IIH2

IIL1

IIL2

RCMFB

Conditions

VREF0 and VREF1

CMP0 to CMP3

VCMIN = VSS to VDD – 1.5 V

Figure 5: VDD = 4 to 6 V

Figure 5

VREF0 and VREF1

CMP0 to CMP3: Without feedback resistor option

VREF0 and VREF1

CMP0 to CMP3: Without feedback resistor option

CMP0 to CMP3: With feedback resistor option

min typ max Unit

VSS + 0.3

VDD – 1.5

V

VSS

VDD – 1.5

V

±50 ±300 mV

1.0 5.0

µs

1.0 200

1.0

µA

1.0

–1.0

µA

–1.0

460 kΩ

No. 5117-11/39

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet LC6529L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LC6529F | 4-Bit Microcomputer for Small-Scale Control Applications | Sanyo |

| LC6529F | One-Time Programmable 4-Bit Single-Chip Microcontroller | Sanyo |

| LC6529L | 4-Bit Microcomputer for Small-Scale Control Applications | Sanyo |

| LC6529L | One-Time Programmable 4-Bit Single-Chip Microcontroller | Sanyo |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |