|

|

PDF K4D551638F-TC Data sheet ( Hoja de datos )

| Número de pieza | K4D551638F-TC | |

| Descripción | 256Mbit GDDR SDRAM | |

| Fabricantes | Samsung | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de K4D551638F-TC (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

K4D551638F-TC

Target Spec

256M GDDR SDRAM

256Mbit GDDR SDRAM

4M x 16Bit x 4 Banks

Graphic Double Data Rate

Synchronous DRAM

Revision 1.7

June 2004

Samsung Electronics reserves the right to change products or specification without notice.

-1-

Rev 1.7 (June 2004)

1 page

K4D551638F-TC

Target Spec

256M GDDR SDRAM

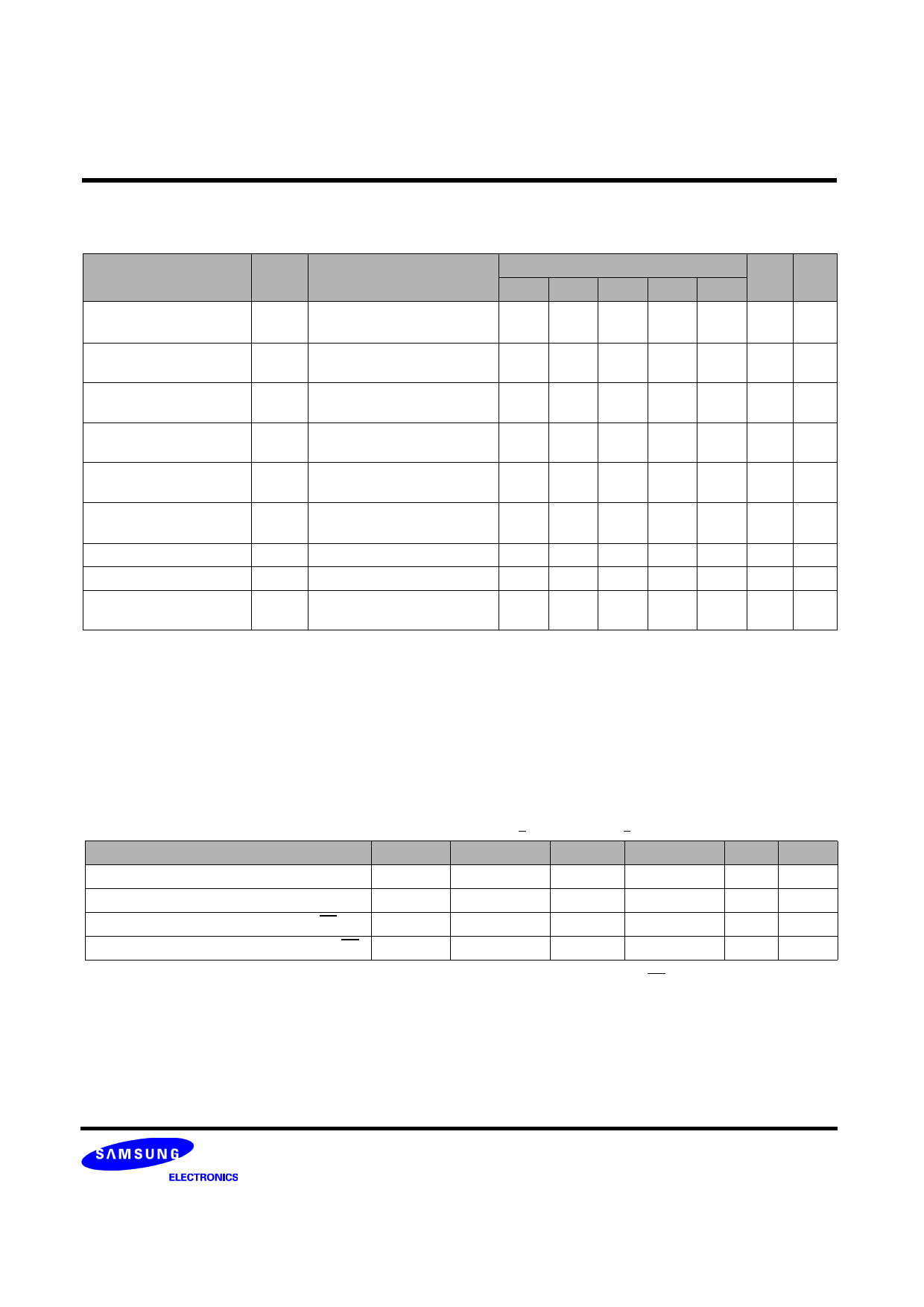

INPUT/OUTPUT FUNCTIONAL DESCRIPTION

Symbol

CK, CK*1

CKE

CS

RAS

CAS

WE

LDQS,UDQS

LDM,UDM

DQ0 ~ DQ15

BA0, BA1

A0 ~ A12

VDD/VSS

VDDQ/VSSQ

VREF

NC/RFU

Type

Input

Input

Input

Input

Input

Input

Input/Output

Input

Input/Output

Input

Input

Power Supply

Power Supply

Power Supply

No connection/

Reserved for future use

Function

The differential system clock Input.

All of the inputs are sampled on the rising edge of the clock except

DQ’s and DM’s that are sampled on both edges of the DQS.

Activates the CK signal when high and deactivates the CK signal

when low. By deactivating the clock, CKE low indicates the Power

down mode or Self refresh mode.

CS enables the command decoder when low and disabled the com-

mand decoder when high. When the command decoder is disabled,

new commands are ignored but previous operations continue.

Latches row addresses on the positive going edge of the CK with

RAS low. Enables row access & precharge.

Latches column addresses on the positive going edge of the CK with

CAS low. Enables column access.

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

Data input and output are synchronized with both edge of DQS.

For the x16, LDQS corresponds to the data on DQ0-DQ7 ; UDQS

corresponds to the data on DQ8-DQ15.

Data in Mask. Data In is masked by DM Latency=0 when DM is

high in burst write. For the x16, LDM corresponds to the data on

DQ0-DQ7 ; UDM correspons to the data on DQ8-DQ15.

Data inputs/Outputs are multiplexed on the same pins.

Selects which bank is to be active.

Row/Column addresses are multiplexed on the same pins.

Row addresses : RA0 ~ RA12, Column addresses : CA0 ~ CA8.

Power and ground for the input buffers and core logic.

Isolated power supply and ground for the output buffers to provide

improved noise immunity.

Reference voltage for inputs, used for SSTL interface.

This pin is recommended to be left "No connection" on the device

*1 : The timing reference point for the differential clocking is the cross point of CK and CK.

For any applications using the single ended clocking, apply VREF to CK pin.

-5-

Rev 1.7 (June 2004)

5 Page

K4D551638F-TC

DC CHARACTERISTICS

Recommended operating conditions Unless Otherwise Noted, TA=0 to 65°C)

Target Spec

256M GDDR SDRAM

Parameter

Symbol

Test Condition

Operating Current

(One Bank Active)

ICC1

Burst Lenth=2 tRC ≥ tRC(min)

IOL=0mA, tCC= tCC(min)

Precharge Standby Current

in Power-down mode

ICC2P

CKE ≤ VIL(max), tCC= tCC(min)

Precharge Standby Current

in Non Power-down mode

ICC2N

CKE ≥ VIH(min), CS ≥ VIH(min),

tCC= tCC(min)

Active Standby Current

power-down mode

ICC3P CKE ≤ VIL(max), tCC= tCC(min)

Active Standby Current in

in Non Power-down mode

ICC3N

CKE ≥ VIH(min), CS ≥ VIH(min),

tCC= tCC(min)

Operating Current

(Burst Mode)

ICC4

tRC ≥ tRFC(min)tRC ≥ tRFC(min)

Page Burst, All Banks activated.

Refresh Current

ICC5

tRC ≥ tRFC(min)

Self Refresh Current

ICC6

CKE ≤ 0.2V

Operating Current

(4Bank Interleaving)

ICC7

Burst Length=4, tRC ≥ tRFC(min)

IOL=0mA, tCC = tCC(min)

Note : 1. Measured with outputs open.

2. Refresh period is 64ms

-33

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

Version

-36 -40 -50

TBD TBD 150

TBD TBD

4

TBD TBD 25

TBD TBD 55

TBD TBD 75

TBD TBD

TBD

TBD

TBD

TBD

TBD TBD

250

200

3

380

Unit Note

-60

125 mA 1

3 mA

20 mA

35 mA

56 mA

200 mA

180 mA

3 mA

350 mA

2

AC INPUT OPERATING CONDITIONS

Recommended operating conditions(Voltage referenced to VSS=0V, VDD=2.6V+ 0.1V, VDDQ=2.6V+ 0.1V ,TA=0 to 65°C)

Parameter

Input High (Logic 1) Voltage; DQ

Symbol

VIH

Min

VREF+0.35

Typ

-

Max

-

Unit

V

Input Low (Logic 0) Voltage; DQ

Clock Input Differential Voltage; CK and CK

VIL

VID

-

0.7

-

VREF-0.35

V

-

VDDQ+0.6

V

Clock Input Crossing Point Voltage; CK and CK VIX 0.5*VDDQ-0.2

-

0.5*VDDQ+0.2

V

Note

1

2

Note : 1. VID is the magnitude of the difference between the input level on CK and the input level on CK

2. The value of VIX is expected to equal 0.5*VDDQ of the transmitting device and must track variations in the DC level of the same

- 11 -

Rev 1.7 (June 2004)

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet K4D551638F-TC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4D551638F-TC | 256Mbit GDDR SDRAM | Samsung |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |