|

|

PDF PDSP16350 Data sheet ( Hoja de datos )

| Número de pieza | PDSP16350 | |

| Descripción | I/Q Splitter/NCO | |

| Fabricantes | Mitel Networks Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PDSP16350 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

Supersedes version in December 1993 Digital Video & DSP IC Handbook, HB3923-1

PDSPPD1S6P13653500

I/Q Splitter/NCO

DS3711 - 2.3 September 1996

The PDSP16350 provides an integrated solution to the

need for very accurate, digitised, sine and cosine waveforms.

Both these waveforms are produced simultaneously, with 16

bit amplitude accuracy, and are synthesised using a 34 bit

phase accumulator. The more significant bits of this provide

16 bits of phase accuracy for the sine and cosine look up

tables.

With a 20 MHz system clock, waveforms up to 10 MHz can

be produced, with 0.001 Hz resolution. If frequency modula-

tion is required with no discontinuities, the phase increment

value can be changed linearly on every clock cycle. Alterna-

tively absolute phase jumps can be made to any phase value.

The provision of two output multipliers allows the sine and

cosine waveforms to be amplitude modulated with a 16 bit

value present on the input port. This option can also be used

to generate the in-phase and quadrature components from an

incoming signal. This I/Q split function is required by systems

which employ complex signal processing.

FEATURES

s Direct Digital Synthesiser producing simultaneous sine

and cosine values

s 16 bit phase and amplitude accuracy, giving spur levels

down to - 90 dB

s Synthesised outputs from DC to 10 MHz with accuracies

better than 0.001 Hz

s Amplitude and Phase modulation modes

s 84 pin PGA or 132 pin QFP

APPLICATIONS

s Numerically controlled oscillator (NCO)

s Quadrature signal generator

s FM, PM, or AM signal modulator

s Sweep Oscillator

s High density signal constellation applications with simul-

taneous amplitude and phase modulation

s VHF reference for UHF generators

s Signal demodulator

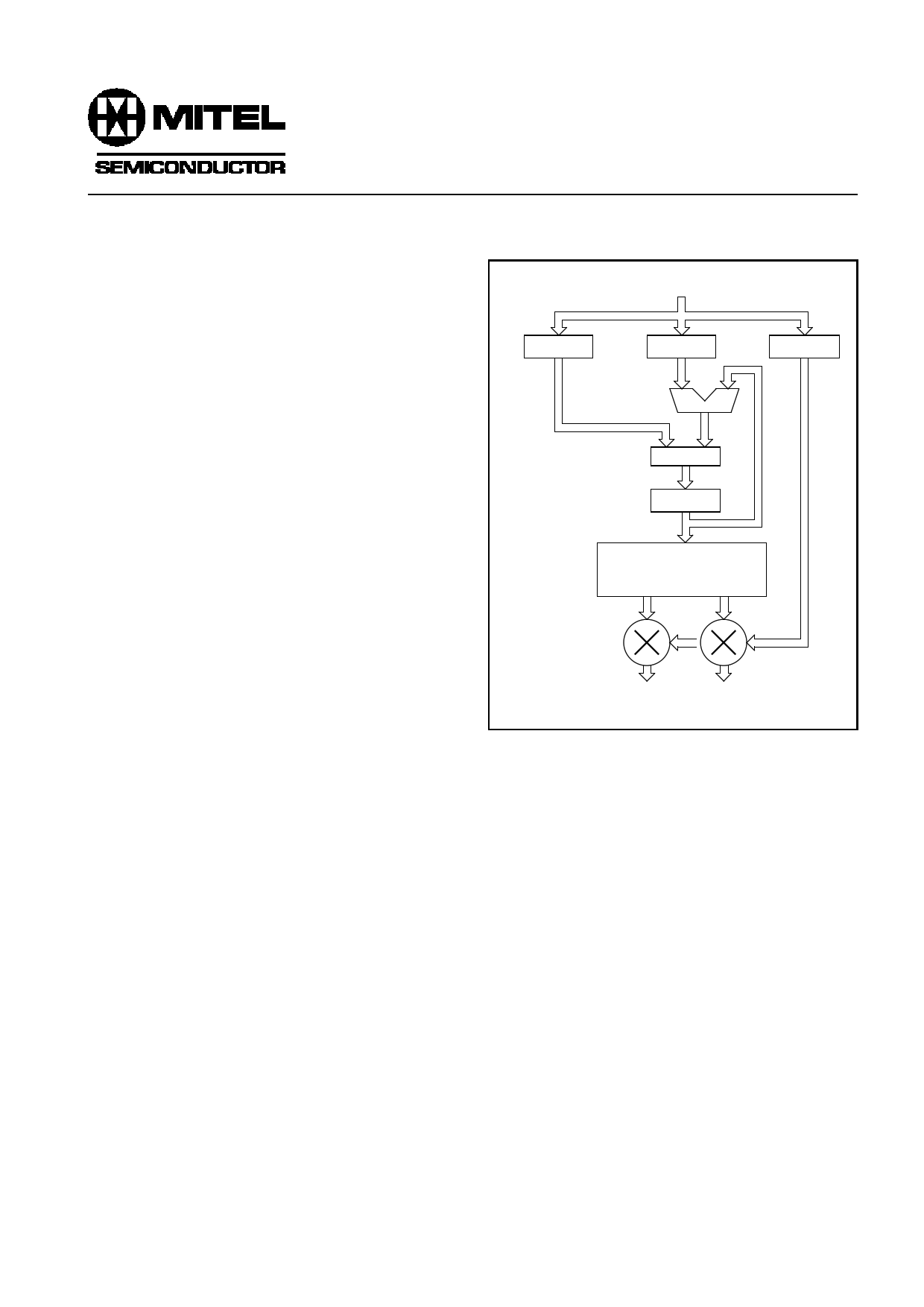

PHASE OFFSET

REGISTER

DIN

PHASE INCR

REGISTER

ACCUM

MUX

PHASE ACCUM

REGISTER

CORDIC PROCESSOR ARRAY

SIN COS

Fig. 1 Block Diagram

ASSOCIATED PRODUCTS

PDSP16256/A Programmable FIR Filter

PDSP16510A FFT Processor

PDSP16488A 2D Convolver

SCALING

REGISTER

1

1 page

DEVICE OPERATION

Sine and cosine are simultaneously produced by the

Cordic processor, which is addressed by the upper 16 bits of

the output from a 34 bit phase accumulator. The accumulator

divides the digital phase circle into a number of steps, one step

for each state of the accumulator. When the accumulator

reaches its maximum value it overflows back to zero and the

sequence is repeated.

The accumulator is incremented once per incoming clock

cycle, by an amount which defines the frequency which is to

be generated. The increment required is defined by :

Desired O/P Frequency

Increment =

x 2N

Incoming Clock Frequency

where N is the number of bits in the accumulator. Since the

Nyquist criteria for proper waveform reconstruction must still

be obeyed, the maximum output frequency is half the incom-

ing frequency. In practice, when a return is made to the analog

world, just meeting the minimum Nyquist requirement would

require a ‘brick wall’ low pass filter to remove the alias signals.

A more useful ‘rule of thumb’ is to limit the generated wave-

forms to less than 40% of the clock frequency.

The resolution, or tuning sensitivity, of the waveform

generator is given by :

Incoming Clock Frequency

Resolution =

Hz

2N

These equations illustrate some very important features of

direct digital synthesisers :-

1) Tuning sensitivity is defined by both the number of bits in

the accumulator and the incoming time base frequency.

2) The oscillator tunes linearly over its entire range.

3) The frequency accuracy matches the accuracy of the

incoming increment value.

PDSP16350

4) DC can be generated since the increment value can be

zero.

5) Frequency stability will match the stability of the incoming

frequency when the increment is fixed.

The residual noise characteristics of an oscillator are very

important in modern communication systems. This parameter

defines how well the device maintains its set frequency for

very short periods (nanoseconds to seconds) of time. Poor

figures will significantly affect the system signal to noise ratio

and limit the dynamic range.

The PDSP16350 will, of course, inherit the residual noise

characteristics of the source of the incoming frequency. The

output frequency is, however, always less than half the

incoming frequency in order to satisfy the Nyquist criterion.

This is in contrast to a phase locked loop synthesiser, when a

small input frequency controls a high output frequency.

The commonly used 20 log N rule states that the phase

noise at the output of a synthesiser will be no better than

twenty times the log of the ratio of the output frequency to the

input frequency. In a phase locked loop synthesiser N is large,

in the PDSP16350 it is less than half. Log N is thus less than

zero and phase noise improvement is obtained.

The output waveforms are produced after a pipeline delay

with respect to the DIN inputs. The effects of the JUMP or RES

commands are delayed such that all data in the internal pipe

will be processed before the discontinuity occurs. New data

may be presented to the device on the cycle following the

JUMP or RES and a valid result will be obtained after 31 clock

cycles.

CLK

MODE

RESET

JUMP

CEN

DATA IN

RESULT

12345

PI PI

30 31 32 33 34 35

ABCD

Device Reset Apply phase increment

Fig. 3 Fixed Frequency Timing Diagram

First Result Available

5

5 Page

ORDERING INFORMATION

Industrial (-40°C to +85°C)

PDSP16350 / B0 / AC

(20MHz - PGA)

PDSP16350 / B0/ GC

(20MHz - QFP)

Military (-55°C to +125°C)

PDSP16350 / A0 / AC

(20MHz - PGA)

PDSP16350 / A0/ GC

(20MHz - QFP)

PDSP16350

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet PDSP16350.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PDSP16350 | I/Q Splitter/NCO | Mitel Networks Corporation |

| PDSP16350 | I/Q Splitter/NCO | Zarlink Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |