|

|

PDF PDI1394L11BA Data sheet ( Hoja de datos )

| Número de pieza | PDI1394L11BA | |

| Descripción | 1394 AV link layer controller | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PDI1394L11BA (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

PDI1394L11

1394 AV link layer controller

Product specification

1997 Oct 21

Philips

Semiconductors

1 page

Philips Semiconductors

1394 AV link layer controller

Product specification

PDI1394L11

9.2 AV Interface

PIN No.

PIN SYMBOL

77, 76, 75, 74,

71, 70, 69, 68

AV D[7:0]

58 AVCLK

57 AVSYNC

59 AVFSYNCIN

60 AVFSYNCOUT

56 AVENDPCK

61 AVVALID

53 AVERR0

52 AVERR1

9.3 Phy Interface

PIN No.

PIN SYMBOL

34, 35, 36, 37,

40, 41, 42, 43

PHY D[0:7]

46, 47

PHY CTL[0:1]

48 ISO_N

54 LREQ

55 SCLK

9.4 Other Pins

PIN No.

PIN SYMBOL

65, 66, 67

RESERVED

51, 62, 80

N/C

30 CYCLEIN

33 CYCLEOUT

11 CLK 25

I/O NAME AND FUNCTION

I/O Audio/Video Data 7 (MSB) through 0. Byte-wide interface to the AV layer.

I External application clock. Rising edge active.

I/O Start of packet indicator; should only be used when AVVALID is active.

I

Frame sync input. Used for Digital Video (DV). The signal is time stamped and transmitted in

the SYT field of ITXHQ2.

O Frame sync output. Signal is derived from SYT field of IRXHQ2.

I

End of application packet indication from data source. Required only if input packet is not

multiple of 4 bytes. It can be tied LOW for data packets that are 4*N in size.

I/O Indicates data on AV D [7:0] is valid

O

CRC error, indicates bus packet containing AV D [7:0] had a CRC error, the current AV packet

is unreliable.

O Sequence Error. Indicates at least one source packet was lost before the current AV D [7:0]

I/O NAME AND FUNCTION

Data 0 (MSB) through 7 (NOTE: To preserve compatibility to the specified Link-Phy interface

I/O

of the IEEE 1394–1995 standard, Annex J, bit 0 is the most significant bit). Data is expected

on AV D[0:1] for 100Mb/s, AV D[0:3] for 200Mb/s, and AV D[0:7] for 400Mb/s. See IEEE

1394–1995 standard, Annex J for more information.

I/O Control Lines between Link and Phy. See 1394 Specification for more information.

Isolation barrier. This terminal is asserted (LOW) when an isolation barrier is present. See

I IEEE 1394–1995 standard, Annex J for more information (used to request arbitration or

read/write PHY registers).

O

Link Request. Bus request to access the PHY. See IEEE 1394–1995 standard, Annex J for

more information.

I

System clock. 49.152MHz input from the PHY (the PHY-LINK interface operates at this

frequency).

I/O NAME AND FUNCTION

NA

These pins are reserved for factory testing. For normal operation they should be connected to

ground.

NA These are test mode pins and should not be connected or terminated.

I

Provides the capability to supply an external cycle timer signal for the beginning of 1394 bus

cycles.

O Reproduces the 8kHz cycle clock of the cycle master.

O Auxiliary clock, value is SCLK/2 (usually 24.576 MHz)

1997 Oct 21

5

5 Page

Philips Semiconductors

1394 AV link layer controller

Product specification

PDI1394L11

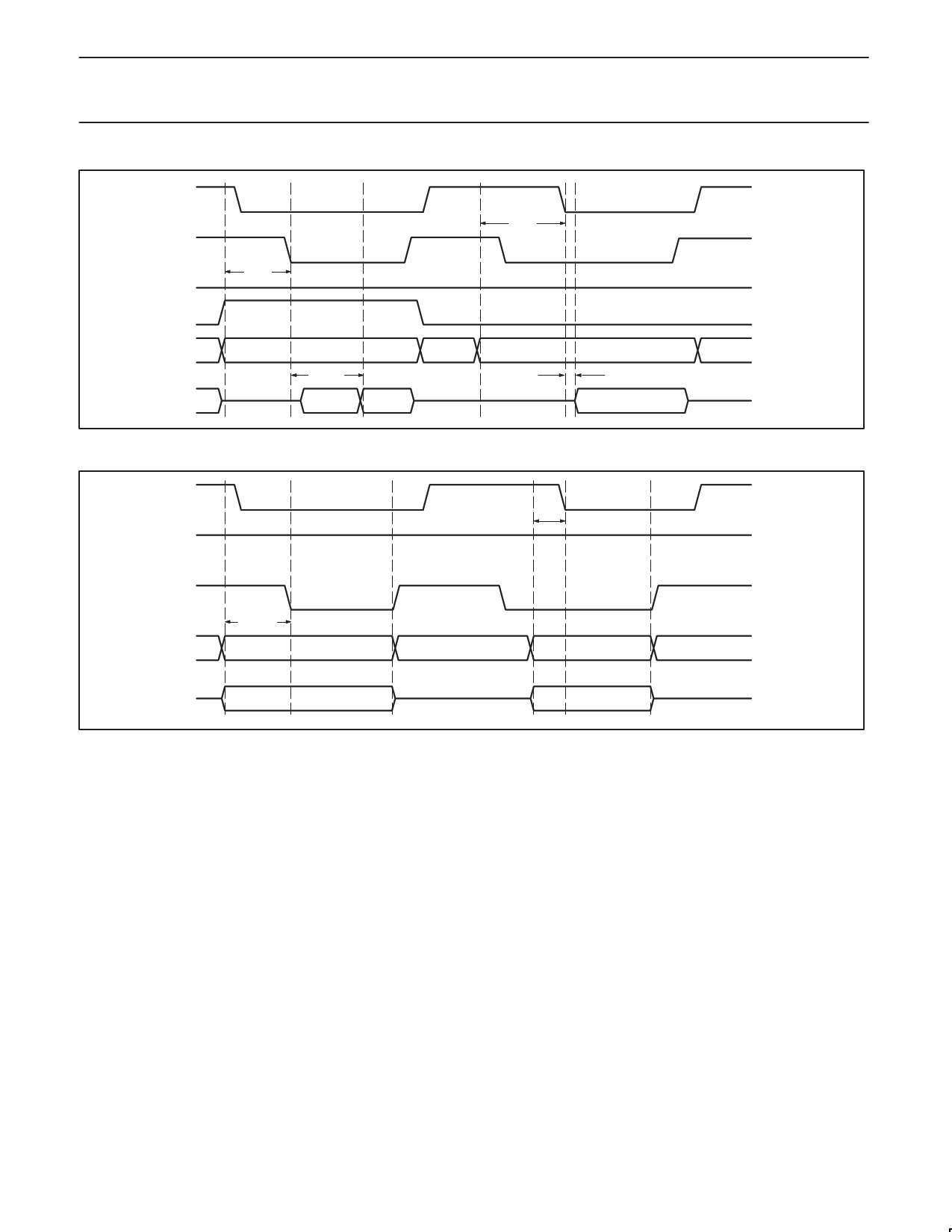

HIF CS_N

HIF RD_N

HIF WR_N

HIF A8

HIF A0..HIF A7

HIF D0..HIF D7

HIF CS_N

HIF RD_N

TAS

TAS

TACC

RSRO

RSRn

TACC

RSRn

Figure 2. Read cycle signal timing (2 independent read cycles)

TAS

SV00686

HIF WR_N

HIF A0..HIF A8

TAS

<VALID ADDRESS>

<VALID ADDRESS>

HIF D0..HIF D7

<WRITE DATA>

<WRITE DATA>

Figure 3. Write cycle signal timing (2 independent write cycles)

SV00687

12.4 The Asynchronous Packet Interface

The PDI1394L11 provides an interface to asynchronous data

packets through the registers in the host interface. The format of the

asynchronous packets is specified in the following sections.

12.4.1 Reading an Asynchronous Packet

Upon reception of a packet, the packet data is stored in the

appropriate receive FIFO, either the Request or Response FIFO.

The location of the packet is indicated by either the RREQQQAV or

RRSPQAV status bit being set in the Asynchronous Interrupt

Acknowledge (ASYINTACK) register. The packet is transferred out

of the FIFO by successive reads of the Asynchronous Receive

Request (RREQ) or Asynchronous Receive Response (RRSP)

register. The end of the packet (the last quadlet) is indicated by

either the RREQQLASTQ or RRSPQLASTQ bit set in ASYINTACK.

Attempting to read the FIFO when either RREQQQAV bit or

RRSPQQAV bit is set to 0 (in the Asynchronous RX/TX interrupt

acknowledge (ASYINTACK) register) will result in a queue read

error.

12.4.2 Writing an Asynchronous Packet

An asynchronous packet intended for transmission is first stored in

the appropriate Transmitter FIFO. Once writing to the FIFO is

complete, the link layer controller arbitrates for the bus to transmit

the packet.

To generate an asynchronous packet, the first and next to last

quadlets of the packet must be written to the Asynchronous

Transmit Request Next (TX_RQ_NEXT) register, for request type

packets, or the Asynchronous Transmit Response Next

(TX_RP_NEXT) register, for response type packets. The last

quadlet of the packet is written to the Asynchronous Transmit

Request Last (TX_RQ_LAST) register, for request type packets, or

the Asynchronous Transmit Response Last (TX_RP_LAST)

register, for response type packets. After writing the last quadlet,

the packet is automatically queued by the AVlink layer controller for

transmission over the bus.

1997 Oct 21

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PDI1394L11BA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PDI1394L11BA | 1394 AV link layer controller | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |