|

|

PDF TDA7300D Data sheet ( Hoja de datos )

| Número de pieza | TDA7300D | |

| Descripción | DIGITAL CONTROLLED STEREO AUDIO PROCESSOR | |

| Fabricantes | ST Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TDA7300D (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

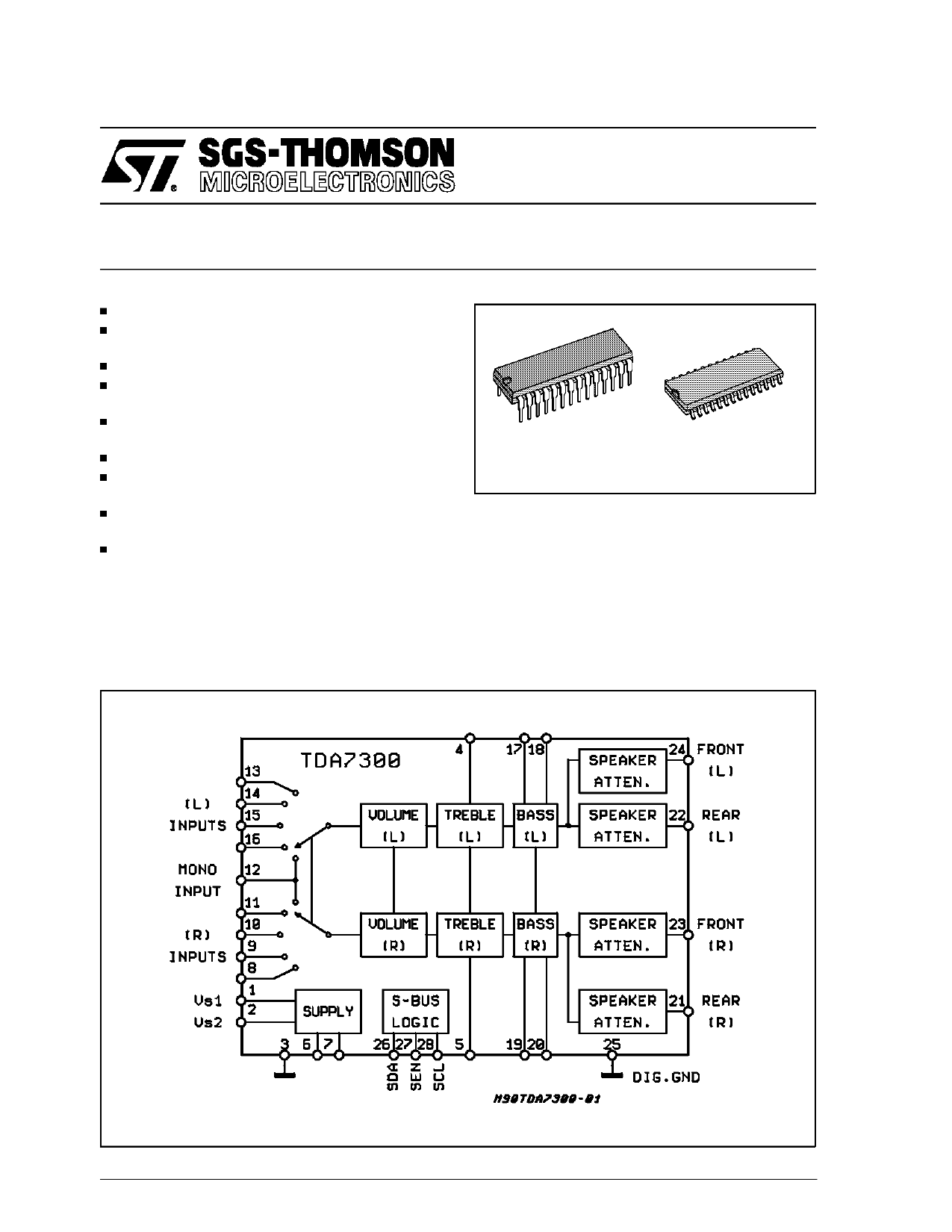

TDA7300

DIGITAL CONTROLLED STEREO AUDIO PROCESSOR

SINGLE SUPPLY OPERATION

FOUR STEREO INPUT SOURCE SELEC-

TION

MONO INPUT

TREBLE, BASS, VOLUME, AND BALANCE

CONTROL

FOUR INDEPENDENT SPEAKER CONTROL

(FRONT/REAR)

SINGLE SUPPLY OPERATION

ALL FUNCTIONS PROGRAMMABLE VIA SE-

RIAL BUS

VERY LOW NOISE AND VERY LOW DIS-

TORTION

POP FREE SWITCHING

DESCRIPTION

The TDA7300 is a volume, tone (bass and treble),

balance (left/right) and fader (front/rear) proces-

BLOCK DIAGRAM

DIP28

SO28

ORDERING NUMBERS:

TDA7300

TDA7300D

sor for high quality audio applications in car radio

and Hi-Fi systems.

Control is accomplished by serial bus microproc-

essor interface.

The AC signal setting is obtained by resistor net-

works and analog switches combined with opera-

tional amplifiers.

The results are: low noise, low distortion and high

dynamic range.

May 1991

1/16

This is advanced information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

1 page

Figure 2: P.C. Board and Components Layout of the Fig.1 (1:1 scale)

TDA7300

5/16

5 Page

APPLICATION INFORMATION (continued)

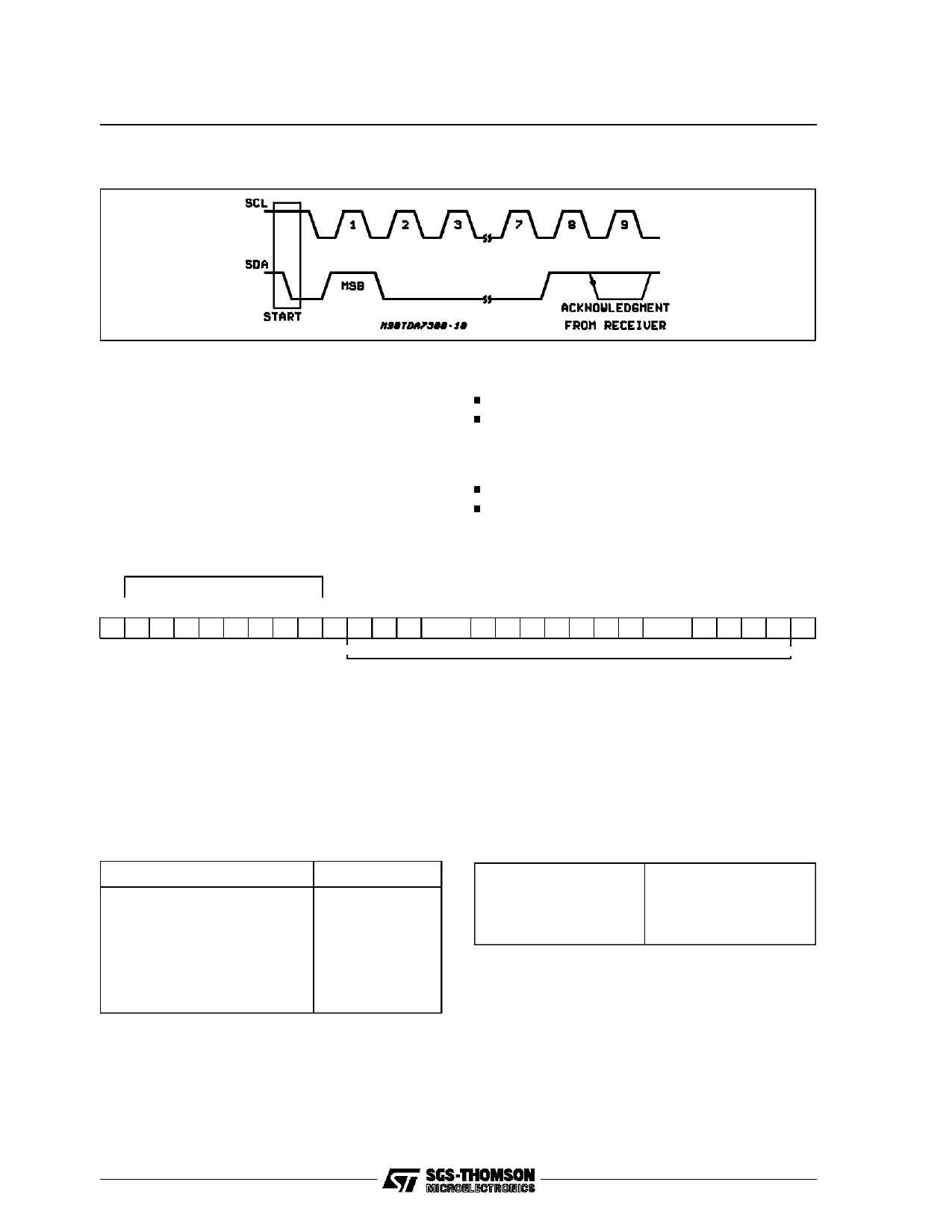

Figure 23: Acknowledge on the I2CBUS

TDA7300

Transmission without Acknowledge

Avoiding to detect the acknowledge of the audio-

processor, the µP can use a simplier transmission:

simply it waits one clock without checking the slave

acknowledging, and sends the new data.

This approach of course is less protected from

misworking and decreases the noise immunity.

Interface Protocol

The interface protocol comprises:

A start condition (S)

A chip address byte, containing the TDA7300

address (the 8th bit of the byte must be 0). The

TDA7300 must always acknowledge at the end

of each transmitted byte.

A sequence of data (N-bytes + acknowledge)

A stop condition (P)

TDA7300 ADDRESS

MSB first byte

LSB MSB

S 1 0 0 0 1 0 0 0 ACK

DATA

LSB MSB

ACK

DATA

LSB

ACK P

ACK = Acknowledge

S = Start

P = Stop

MAX CLOCK SPEED 100kbits/s

Data Transferred (N-bytes + Acknowledge)

SOFTWARE SPECIFICATION

Chip address (TDA7300 address)

100010

MSB

00

IIII I LSB

DATA BYTES

MSB

00

11

11

10

10

01

01

01

LSB

B2 B1 B0 A2 A1 A0

0 B1 B0 A2 A1 A0

1 B1 B0 A2 A1 A0

0 B1 B0 A2 A1 A0

1 B1 B0 A2 A1 A0

0 X X S2 S1 S0

1 0 C3 C2 C1 C0

1 1 C3 C2 C1 C0

Function

Volume Control

Speaker ATT LR

Speaker ATT RR

Speaker ATT LF

Speaker ATT RF

Audio switch

Bass control

Treble control

X = don’t care

Ax = 2dB steps

Bx = 10dB steps

Cx = 2.5dB steps

Status after power-on reset

Volume

Speaker

Audio Switch

Bass

Treble

–68dB

–38dB

Mono

+2.5dB

+2.5dB

11/16

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet TDA7300D.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA7300 | DIGITAL CONTROLLED STEREO AUDIO PROCESSOR | ST Microelectronics |

| TDA7300D | DIGITAL CONTROLLED STEREO AUDIO PROCESSOR | ST Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |