|

|

PDF TDA4886 Data sheet ( Hoja de datos )

| Número de pieza | TDA4886 | |

| Descripción | 140 MHz video controller with I2C-bus | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TDA4886 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

TDA4886

140 MHz video controller with

I2C-bus

Product specification

Supersedes data of 1998 Nov 04

File under Integrated Circuits, IC02

1998 Nov 11

1 page

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

LIM 24

SDA SCL

REGISTER

6

PEDST

DISO

DISV

FPOL

BLH1

BLH2

12 13

I2C-BUS

6

6-BIT

DAC

SUBCONTRAST

CONTRAST MODULATION

LIMITING

4

4-BIT

DAC

6 666

6-BIT

DAC

6-BIT

DAC

6-BIT

DAC

6-BIT

DAC

BRIGHTNESS

BLANKING

8

8

8

TDA4886

8-BIT

DAC

8-BIT

DAC

8-BIT

DAC

VI1 6

INPUT

CLAMPING

BLANKING

CONTRAST

OSD

CONTRAST

GAIN

BRIGHTNESS

PEDESTAL

BLANKING

FPOL

VI2 8

INPUT

CLAMPING

BLANKING

CONTRAST

OSD

CONTRAST

GAIN

BRIGHTNESS

VI3 10

INPUT

CLAMPING

BLANKING

CONTRAST

OSD

CONTRAST

GAIN

BRIGHTNESS

fast

blanking

input clamping

DISO

OSD INPUT

1234

FBL OSD1 OSD2 OSD3

vertical

blanking

INPUT CLAMPING

VERTICAL BLANKING

5

CLI

PEDST

PEDESTAL

BLANKING

FPOL

FPOL

PEDST

PEDESTAL

BLANKING

FPOL

FPOL

PEDST

FPOL

blanking

output

clamping

BLANKING

OUTPUT CLAMPING

DISV

11

HFB

CHANNEL 1 FPOL

REFERENCE

CHANNEL 2 FPOL

REFERENCE

CHANNEL 3 FPOL

REFERENCE

21

VP1

22

VO1

23

FB/R1

18 VP2

19 VO2

20

FB/R2

15 VP3

16 VO3

BLH2

BLH1

SUPPLY

17

FB/R3

14

GNDX

79

MHB185

VP GND

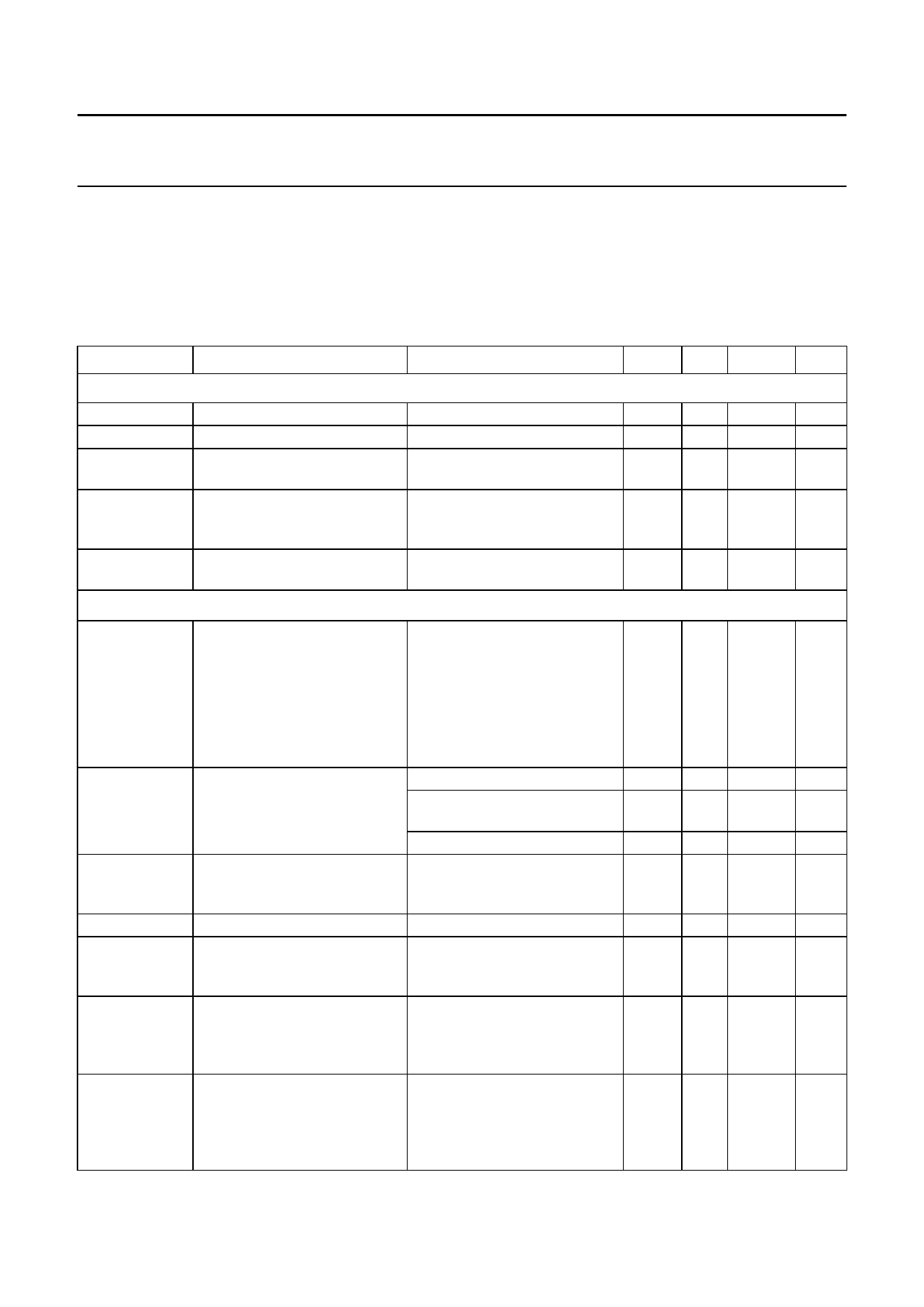

Fig.1 Block diagram.

5 Page

Philips Semiconductors

140 MHz video controller with I2C-bus

Product specification

TDA4886

10 CHARACTERISTICS

All voltages and currents are measured in a dedicated test circuit which is optimized for best high frequency

performance; all voltages are measured with respect to GND (pins 9 and 14); VP = VP1, 2, 3 = 8 V (pins 7, 21,

18 and 15); Tamb = 25 °C; nominal input signals [0.7 V (p-p) at pins 6, 8 and 10]; nominal colour signals at signal

outputs (pins 22, 19 and 16); reference black level (Vrbl) approximately 0.77 V; nominal settings for brightness and

contrast; maximum settings for OSD contrast and gain; no subcontrast, modulation of contrast or limiting (V24 ≥ 5 V); no

OSD fast blanking (pin 1 connected to ground); notes 1 to 3; unless otherwise specified.

SYMBOL

PARAMETER

CONDITIONS

MIN. TYP. MAX. UNIT

Supplies

VP

IP

VP1,2,3

IP1,2,3

VPSO

supply voltage (pin 7)

7.6 8.0 8.8

supply current (pin 7)

note 4

− 21 25

channel supply voltage

(pins 21, 18 and 15)

7.6 8.0 8.8

channel supply current

(pins 21, 18 and 15)

supply voltage for signal switch

off (threshold at pin 7)

signal outputs (pins 22,

19 and 16) open-circuit;

Vrbl ≈ 0.77 V; notes 4 and 5

signal outputs switched to

switch-off voltage

−

−

21 25

− 7.2

V

mA

V

mA

V

Input clamping and vertical blanking input, validation of buffered I2C-bus data (pin 5)

V5

input clamping and vertical

notes 6 and 7

blanking input signal

no vertical blanking,

−0.1 −

+1.2

no input clamping

vertical blanking,

no input clamping

1.6 − 2.6

input clamping,

no vertical blanking

3.5 − VP

I5 input current

V5 = 1 V

pin 5 connected to ground;

note 8

− −0.2 −

−80 −60 −30

V5 = −0.1 V; note 8

−250 −200 −100

tr/f5 rise/fall time for input clamping note 6; see Fig.7

pulse, disable for vertical

− − 75

blanking

tW5

tW5I2C

tI2Cvalid

tI2Cdead

width of input clamping pulse

0.6 − −

width of vertical blanking pulse leading and trailing edge

for validation of buffered

I2C-bus data

threshold V5 = 1.4 V; note 7

10

−−

delay between leading edge of I2C-bus transmission in

vertical blanking pulse and

buffered mode completed;

validation of buffered I2C-bus leading edge threshold

−

−2

data

dead time of I2C-bus receiver

after synchronizing vertical

blanking pulse in case of a

completed I2C-bus

V5 = 1.4 V; note 7

leading edge threshold

V5 = 1.4 V; note 7

15 − −

transmission in buffered mode

V

V

V

µA

µA

µA

ns/V

µs

µs

µs

µs

1998 Nov 11

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TDA4886.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA4881 | Advanced monitor video controller | NXP Semiconductors |

| TDA4882 | Advanced monitor video controller for OSD | NXP Semiconductors |

| TDA4884 | Advanced monitor video controller for OSD | NXP Semiconductors |

| TDA4885 | 150 MHz video controller with I2C-bus | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |