|

|

PDF TDA4852 Data sheet ( Hoja de datos )

| Número de pieza | TDA4852 | |

| Descripción | Horizontal and vertical deflection controller for autosync monitors | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TDA4852 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

TDA4852

Horizontal and vertical deflection

controller for autosync monitors

Preliminary specification

File under Integrated Circuits, IC02

December 1992

1 page

Philips Semiconductors

Horizontal and vertical deflection controller

for autosync monitors

Preliminary specification

TDA4852

FUNCTIONAL DESCRIPTION

Horizontal sync separator and

polarity correction

An AC-coupled video signal or a

DC-coupled TTL sync signal (H only

or composite sync) is input on pin 9.

Video signals are clamped with top

sync on 1.28 V, and are sliced at

1.4 V. This results in a fixed absolute

slicing level of 120 mV related to top

sync. DC-coupled TTL sync signals

are also sliced at 1.4 V, however with

the clamping circuit in current

limitation. The polarity of the

separated sync is detected by internal

integration of the signal, then the

polarity is corrected. The corrected

sync is input signal for the vertical

sync integrator and the PLL1 stage.

Vertical sync separator, polarity

correction and vertical sync

integrator

DC-coupled vertical TTL sync signals

may be applied to pin 10. They are

sliced at 1.4 V. The polarity of the

separated sync is detected by internal

integration, then the polarity is

corrected. If pin 10 is not used, it must

be connected to ground. The

separated Vi sync signal from pin 10, or

the integrated composite sync signal

from pin 9 (TTL or video) triggers

directly the vertical oscillator.

Clamping and V-blanking

generator

A combined clamping and V-blanking

pulse is available on pin 8 (suitable for

the video pre-amplifier TDA4881).

The lower level of 1.9 V is the

blanking signal derived from the

vertical blanking pulse from the

internal vertical oscillator.

Vertical blanking starts with vertical

sync and stops at the begin of vertical

scan. By this, an optimum blanking is

achieved. The upper level of 5.4 V is

the horizontal clamping pulse with an

internally fixed pulse width of 0.8 µs.

A monoflop, which is triggered by the

trailing edge of the horizontal sync

pulse, generates this pulse. If

composite sync is applied, one

clamping pulse per H-period is

generated during V-sync. The phase

of the clamping pulse may change

during V-sync (see Fig.8).

PLL1 phase detector

The phase detector is a standard type

using switched current sources. The

middle of the sync is compared with a

fixed point of the oscillator sawtooth

voltage. The PLL filter is connected to

pin 17. If composite sync is applied,

the disturbed control voltage is

corrected during V-sync (see Fig.8).

Horizontal oscillator

This oscillator is of the relaxation type

and requires a fixed capacitor of

10 nF at pin 19. By changing the

current into pin 18 the whole

frequency range from 13 to 100 kHz

can be covered. The current can be

generated either by a frequency to

voltage converter or by a resistor.

A frequency adjustment may also be

added if necessary.

The PLL1 control voltage at pin 17

modulates via a buffer stage the

oscillator thresholds. A high DC-loop

gain ensures a stable phase

relationship between horizontal sync

and line flyback pulses.

PLL2 phase detector

This phase detector is similar to the

PLL1 phase detector. Line flyback

signals (pin 2) are compared with a

fixed point of the oscillator sawtooth

voltage. Delays in the horizontal

deflection circuit are compensated by

adjusting the phase relationship

between horizontal sync and

horizontal output pulses. A certain

amount of phase adjustment is

possible by injecting a DC current

from an external source into the PLL2

filter capacitor at pin 20.

Horizontal driver

This open-collector output stage

(pin 3) can directly drive an external

driver transistor. The saturation

voltage is less than 300 mV at 20 mA.

To protect the line deflection

transistor, the horizontal output stage

does not conduct for

VP < 6.4 V (pin 1).

Vertical oscillator and amplitude

control

This stage is designed for fast

stabilization of the vertical amplitude

after changes in sync conditions. The

free-running frequency f0 is

determined by the values of RVOS and

CVOS. The recommended values

should be altered marginally only to

preserve the excellent linearity and

noise performance. The vertical drive

currents I5 and I6 are in relation to the

value of RVOS. Therefore, the

oscillator frequency must be

determined only by CVOS on pin 16.

f0 = -1---0---.--8-----×-----R----V---1O----S-----×-----C----V----O---S--

To achieve a stabilized amplitude the

free-running frequency f0 (without

adjustment) must be lower than the

lowest occurring sync frequency. The

following contributions can be

assumed:

minimum frequency

offset between f0 and the

lowest trigger frequency

spread of IC

spread of R (22 kΩ)

spread of C (0.1 µF)

10%

±3%

±1%

±5%

19%

Result: f0 = 1---5-.--10---9-- Hz = 42 Hz

(for 50 to 110 Hz application)

December 1992

5

5 Page

Philips Semiconductors

Horizontal and vertical deflection controller

for autosync monitors

Preliminary specification

TDA4852

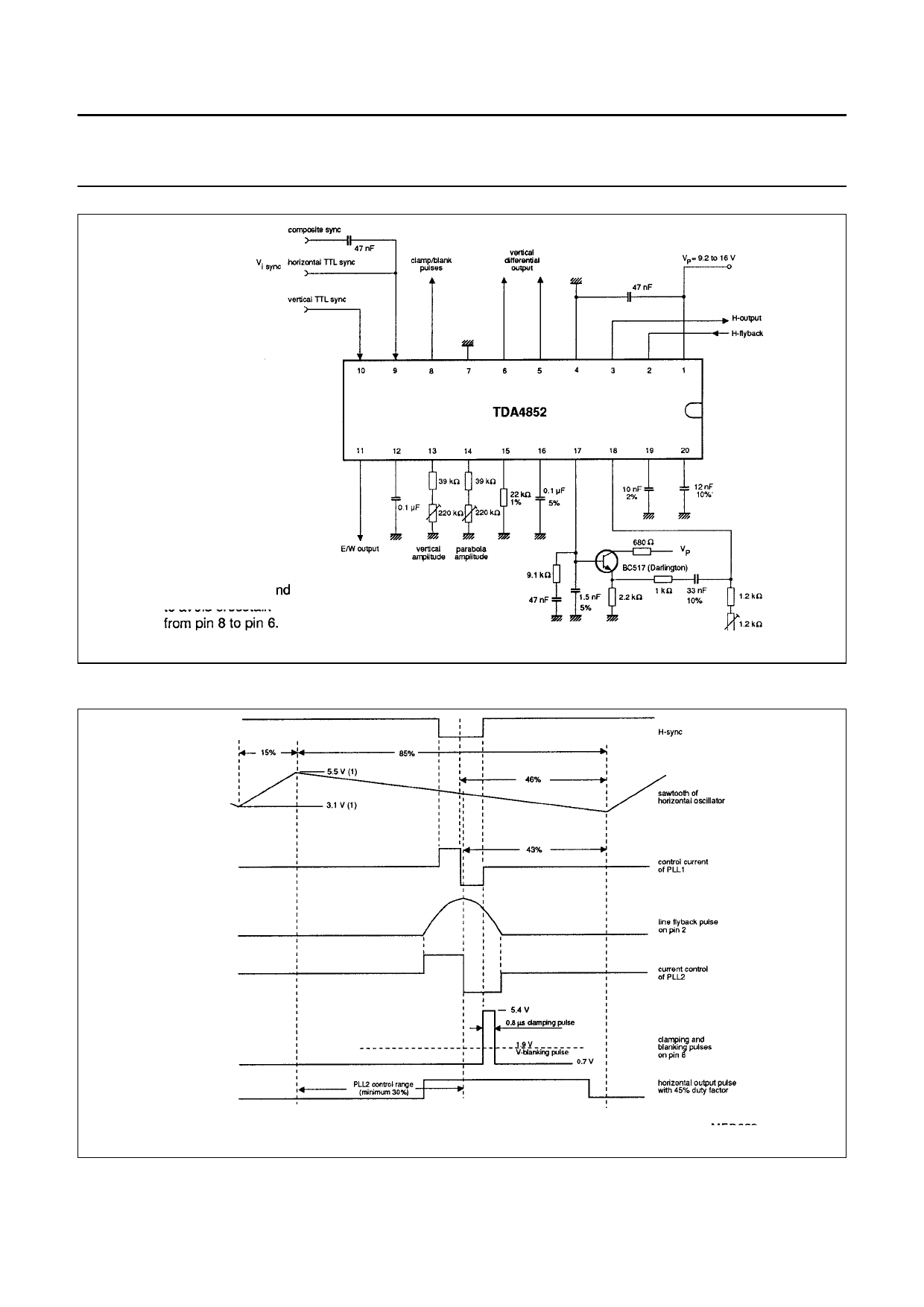

Note:

pin 7 has to be

connected to ground

to avoid crosstalk

from pin 8 to pin 6.

Fig.5 Application circuit for 31 to 64 kHz.

(1) tracks with PLL1 control voltage at pin 17

Fig.6 Horizontal timing diagram.

December 1992

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet TDA4852.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA4850 | Horizontal and vertical deflection controller for VGA/XGA and multi-frequency monitors | NXP Semiconductors |

| TDA4851 | Horizontal and vertical deflection controller for VGA/XGA and autosync monitors | NXP Semiconductors |

| TDA4852 | Horizontal and vertical deflection controller for autosync monitors | NXP Semiconductors |

| TDA4853 | I2C-bus autosync deflection controllers for PC/TV monitors | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |