|

|

PDF TDA4691 Data sheet ( Hoja de datos )

| Número de pieza | TDA4691 | |

| Descripción | Sync Processor with Clock SPC | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TDA4691 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

TDA4691

Sync Processor with Clock (SPC)

Preliminary specification

File under Integrated Circuits, IC02

September 1993

1 page

Philips Semiconductors

Sync Processor with Clock (SPC)

Preliminary specification

TDA4691

FUNCTIONAL DESCRIPTION

(See block diagram Fig.1 and timing

Figs 12 to 16)

Sync separator

Top-sync and blacklevel are stored

and H and V sync pulses are sliced in

the middle of both levels (50%).

Sync-output buffer

This circuit turns the current pulse

from the sync separator into a TTL

signal.

Sync processing

This circuit assures that phase

comparison can operate correctly

during V-pulses. Phase jumps

initiated by alternating headpulses of

VCR recorders are quickly recovered.

The sync processing contains the

functions H/2 suppression, sync

extension and sync interruption.

These three functions are only active

if successive pulses have a minimum

distance of 1.6 µs.

The H/2 suppression operates with a

gate −15 µs up to +14 µs around the

PHI1-reference and is necessary for

suppression of the equalizing pulses.

For sync interruption this gate is

closed earlier if the detected sync is

longer than 4.8 µs.

Only during V-pulses will the duration

of the applied pulses be tested. If they

are longer than 1.6 µs they will be

recognized as sync pulses and

enlarged up to 4.6 µs.

Phase detector (PHI1)

The phase detector has separate

filters for the fast time constant T1 (pin

17) and normal time constant T2 (pins

17 and 16). The slow time constant T3

uses the normal time constant T2 with

reduced control current. For reduction

of H-pulse modulation the filter at pin

16 is switched off during sync time if

normal time constant T2 is on. Thus

no frequency shifting of the oscillator

is possible during sync.

Time-constant switching

This block contains a switch and an

impedance converter (buffer). The

switch connects the filters at pin 16

and 17 in parallel (normal time

constant T2 or slow time constant T3).

The buffer transfers the control

voltage at pin 17 to pin 16 (fast time

constant T1). Which of the 2 functions

is active is determined by the blocks

noise detector, V-logic or signal

identification.

VCO 13.5 MHz

The adjustment of the nominal

frequency (13.5 MHz) is achieved at

pin 15. The VCO control voltage is

applied (from the phase detector) at

pin 16.

The control range can be adjusted by

the current at pin 18.

Pin 15 can be used to feed in an

external frequency. Under these

circumstances the internal VCO is

switched off by application.

The control voltage at pin 16 can be

used to control the external VCO.

VCO-buffer

The VCO-buffer delivers a TTL

compatible signal of 13.5 MHz to pin

13.

ECL-prescaler

This block consists of a :16

asynchronous prescaler.

H-divider

This is a divider by 54. It is split into a

prescaler :2 and a divider by 27. Out

of this block several signals are taken

for generation of H-frequently pulses

in the H-logic block. These signals

must have good timing. This is

achieved by special synchronization.

H-logic

This block creates all pulses

necessary for the SSC generator, the

signal identification, the phase

detector, the sync preparation and the

V-divider.

V-divider

The V-divider consists of an

asynchronous 10-bit divider and a

decoder logic. The divider is clocked

with twice the line frequency. The

decoder circuit delivers the pulses

necessary for the V-logic.

V-logic

In the V-logic the V-syncs from the

sync separator are evaluated and

noise reduced. Also certain operation

states are switched ON and OFF.

Additionally the reset pulse for the

V-divider and the 50/60 Hz

information is generated.

H-pulse former

The H-pulse starting point can be

shifted in this stage, also the gate

pulse of ∼2.4 µs is generated for use

in the digital noise identification block.

H-pulse buffer

In this circuit the line signal will be

pre-synchronized by output signal of

the :16 divider and synchronized by

the 13.5 MHz clock. The buffer

delivers TTL output signals.

V-pulse buffer

The signal out of the V-divider is

synchronized with 13.5 MHz clock

and converted to a TTL output level.

Gap reference

This circuit operates with the

gap-principle and is stable with regard

to temperature and supply voltage

changes.

September 1993

5

5 Page

Philips Semiconductors

Sync Processor with Clock (SPC)

Preliminary specification

TDA4691

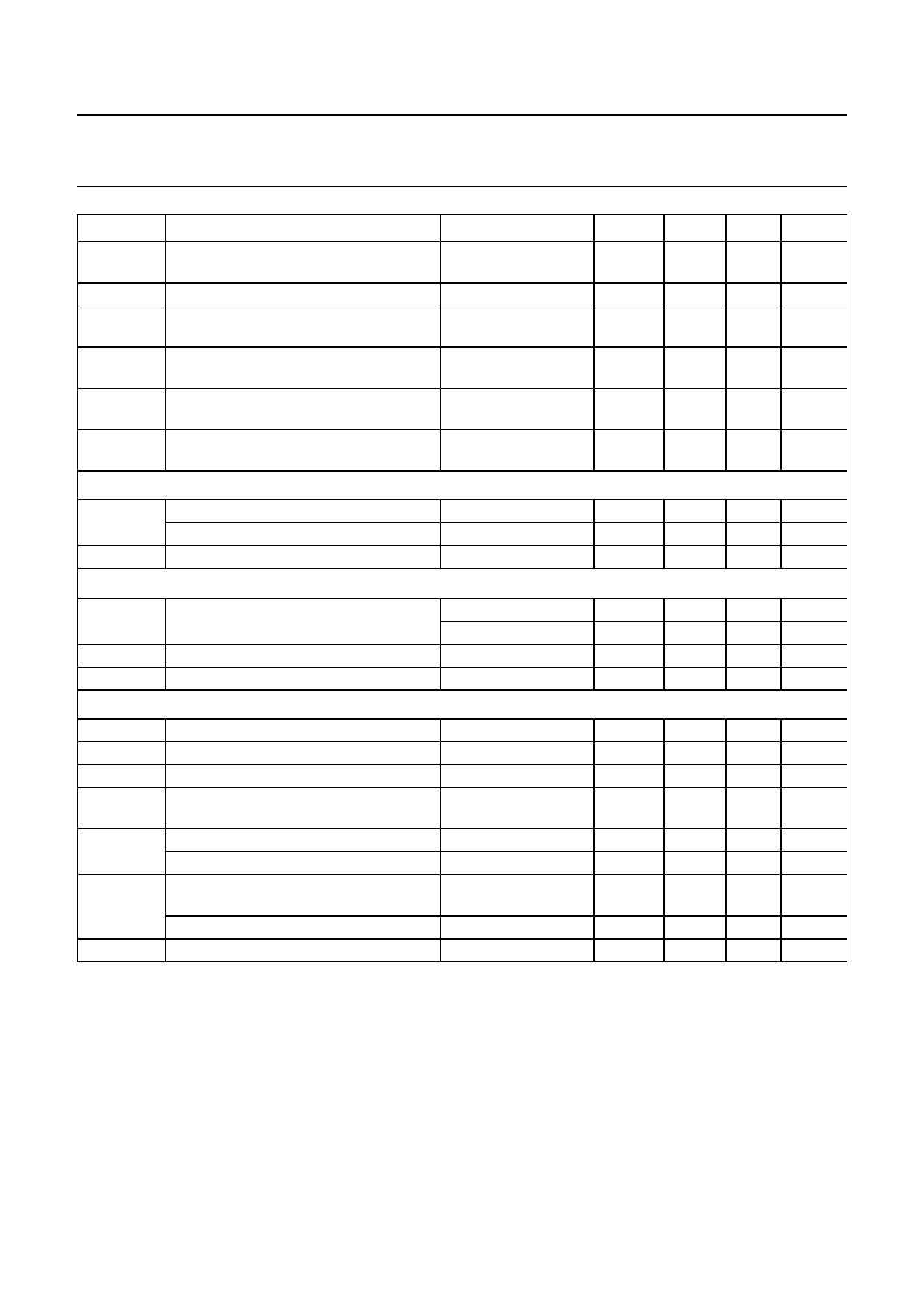

SYMBOL

t3

t4

t5

t5

t6

PARAMETER

time relation between pin 20 and

blanking

H-blanking time

start time H-pulse pin 20 to stop time

burstkey pin 6; 50 Hz

start time H-pulse pin 20 to stop time

burstkey pin 6; 60 Hz

V-blanking pulse; 50 Hz

t6 V-blanking pulse; 60 Hz

CONDITIONS

see Fig.9

see Fig.9

H-sync = 4.7 µs;

see Fig.9

see Fig.9

Integration (pin 5)

V5 no TV signal

TV signal

see Fig.16

see Fig.16

V5 slow time constant on

Signal identification (pin 4; open collector via R4 to V19 or V12)

V4 voltage pin 4, if no signal is identified I4 = 1 mA

I4 = 5 mA

V4 voltage pin 4, if signal is identified

I4 leakage current

Integration (pin 2; see Fig.15)

V2 no signal at pin 20

V2 noise at input pin 20

V2 switching T3 to T1 (delay 7 fields)

V2 switching T3 to T1

(noise and signal at input pin 20)

V2 release V-divider

hysteresis

V2 release time constant normal (T2)

signal identification at pin 4

hysteresis

V2 release noise detector

MIN.

3.5

TYP. MAX. UNIT

4.0 4.5 µs

−

11.8 −

µs

8.0 9.0 9.7 µs

7.5 8.6 9.2 µs

−

−2.5 to −

lines

+22.5

−

−3.0 to −

lines

+17

0 − 2V

4 − −V

5 − 6.2 V

0 − 0.3 V

0 0.2 0.8 V

− − V19 V

− − 50 µA

−

1.5 −

V

− 3 −V

−

2.5 −

V

−

2.5 −

V

− 4 −V

−

−0.2 −

V

− 5 −V

−

−0.2 −

V

−

6.5 −

V

September 1993

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet TDA4691.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA4691 | Sync Processor with Clock SPC | NXP Semiconductors |

| TDA4691T | Sync Processor with Clock SPC | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |