|

|

PDF X1286 Data sheet ( Hoja de datos )

| Número de pieza | X1286 | |

| Descripción | Intersil Real Time Clock/Calendar/CPU Supervisor with EEPROM X1286 | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de X1286 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

New Features

Repetitive Alarms &

Temperature Compensation

2-Wire™ RTC, 256K (32K x 8)

®

Intersil Real Time Clock/Calendar/CPU Supervisor with EEPROM X1286

FEATURES

• Real Time Clock/Calendar

— Tracks time in Hours, Minutes, Seconds and Hun-

dredths of a Second

— Day of the Week, Day, Month, and Year

• 2 Polled Alarms (Non-volatile)

— Settable on the Second, Minute, Hour, Day of the

Week, Day, or Month

— Repeat Mode (periodic interrupts)

• Oscillator Compensation on chip

— Internal feedback resistor and compensation

capacitors

— 64 position Digitally Controlled Trim Capacitor

— 6 digital frequency adjustment settings to

±30ppm

• Battery Switch or Super Cap Input

• 32K x 8 Bits of EEPROM

— 128-Byte Page Write Mode

— 8 modes of Block Lock™ Protection

— Single Byte Write Capability

• High Reliability

— Data Retention: 100 years

— Endurance: 100,000 cycles per byte

• 2-Wire™ Interface interoperable with I2C*

— 400kHz data transfer rate

• Frequency Output (SW Selectable: Off, 1Hz, 100Hz,

or 32.768kHz)

• Low Power CMOS

— 1.25µA Operating Current (Typical)

• Small Package Options

— 8-Lead EIAJ SOIC and 14-Lead TSSOP

APPLICATIONS

• Utility Meters

• HVAC Equipment

• Audio / Video Components

• Set Top Box / Television

• Modems

• Network Routers, Hubs, Switches, Bridges

• Cellular Infrastructure Equipment

• Fixed Broadband Wireless Equipment

• Pagers / PDA

• POS Equipment

• Test Meters / Fixtures

• Office Automation (Copiers, Fax)

• Home Appliances

• Computer Products

• Other Industrial / Medical / Automotive

BLOCK DIAGRAM

32.768kHz

X1

X2

PHZ/IRQ

Select

SCL

SDA

Serial

Interface

Decoder

Control

Decode

Logic

8

OSC

Compensation

Oscillator

Frequency 1Hz

Divider

Timer

Calendar

Logic

Control/

Registers

(EEPROM)

Status

Registers

(SRAM)

Alarm

Time

Keeping

Registers

(SRAM)

Compare

Alarm Regs

(EEPROM)

256K

EEPROM

ARRAY

*I2C is a Trademark of Philips.

REV 1.1 7/8/04

www.intersil.com

Battery

Switch

Circuitry

VCC

VBACK

1 of 26

1 page

X1286

Notes: (1) The device enters the Active state after any start, and remains active: for 9 clock cycles if the Device Select Bits in the Slave

Address Byte are incorrect or until 200nS after a stop ending a read or write operation.

(2) The device enters the Program state 200nS after a stop ending a write operation and continues for tWC.

(3) The device goes into the Timekeeping state 200nS after any stop, except those that initiate a nonvolatile write cycle; tWC after a

stop that initiates a nonvolatile write cycle; or 9 clock cycles after any start that is not followed by the correct Device Select Bits in the

Slave Address Byte.

(4) For reference only and not tested.

(5) VIL = VCC x 0.1, VIH = VCC x 0.9, fSCL = 400KHz

(6) VCC = 0V

(7) VBACK = 0V

(8) VSDA = VSCL=VCC, Others = GND or VCC

(9) VSDA =VSCL=VBACK, Others = GND or VBACK

(10)VSDA = GND or VCC, VSCL = GND or VCC, VRESET = GND or VCC

(11)IOL = 3.0mA at 5.5V, 1.5mA at 2.7V

(12) IOH = -1.0mA at 5.5V, -0.4mA at 2.7V

(13)Threshold voltages based on the higher of Vcc or Vback.

(14)Using recommended crystal and oscillator network applied to X1 and X2 (25°C).

(15)Typical values are for TA = 25°C

Capacitance TA = 25°C, f = 1.0 MHz, VCC = 5V

Symbol

Parameter

Max.

Units

Test Conditions

COUT(1)

CIN(1)

Output Capacitance (SDA, PHZ/IRQ)

Input Capacitance (SCL)

10 pF

10 pF

VOUT = 0V

VIN = 0V

Notes: (1) This parameter is not 100% tested.

(2) The input capacitance between x1 and x2 pins can be varied between 5pF and 19.75pF by using analog trimming registers

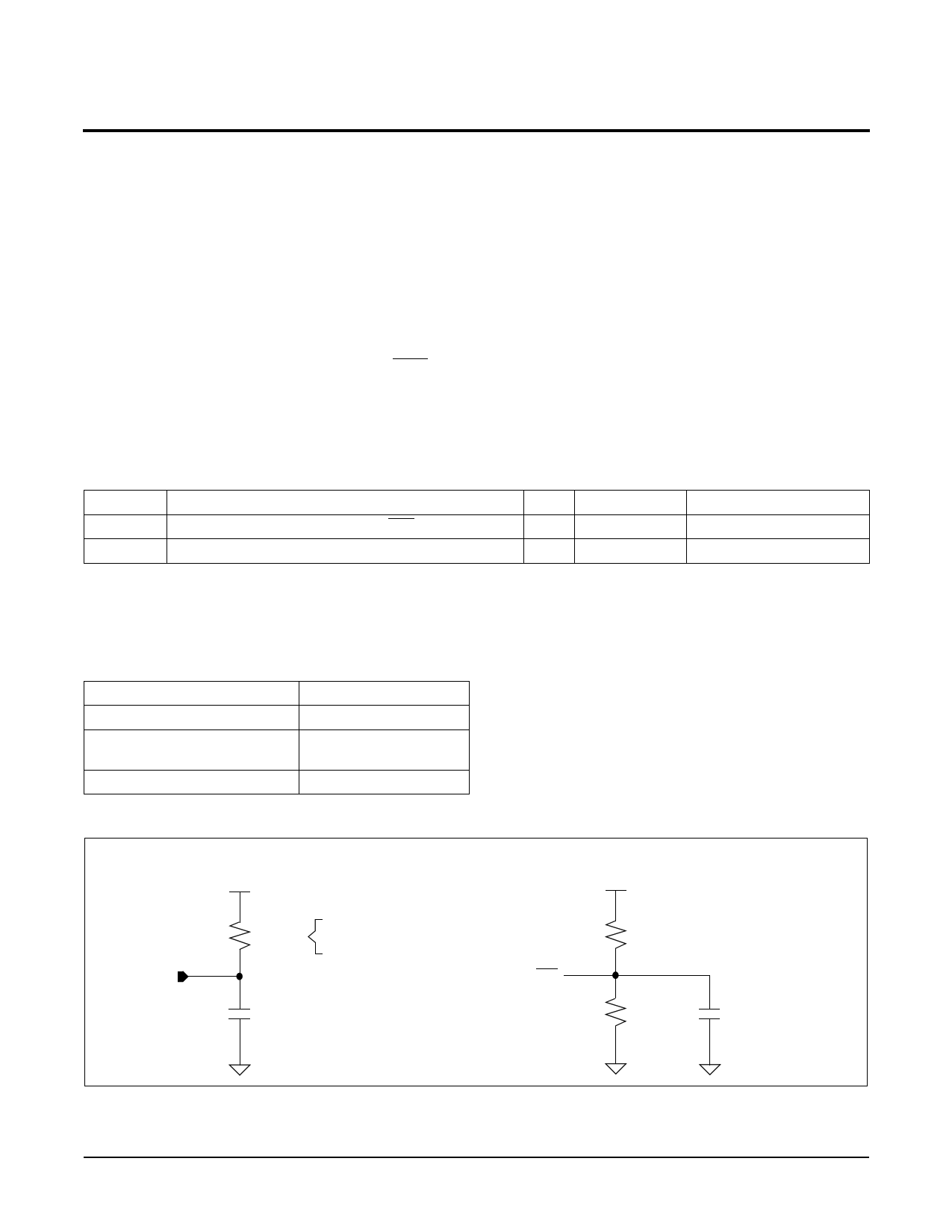

AC CHARACTERISTICS

AC Test Conditions

Input Pulse Levels

Input Rise and Fall Times

Input and Output Timing

Levels

Output Load

VCC x 0.1 to VCC x 0.9

10ns

VCC x 0.5

Standard Output Load

Figure 1. Standard Output Load for testing the device with VCC = 5.0V

Equivalent AC Output Load Circuit for VCC = 5V

5.0V

5.0V

SDA

1533Ω

For VOL= 0.4V

and IOL = 3 mA

100pF

PHZ/IRQ

1316Ω

806Ω

100pF

REV 1.1 7/8/04

www.intersil.com

5 of 26

5 Page

X1286

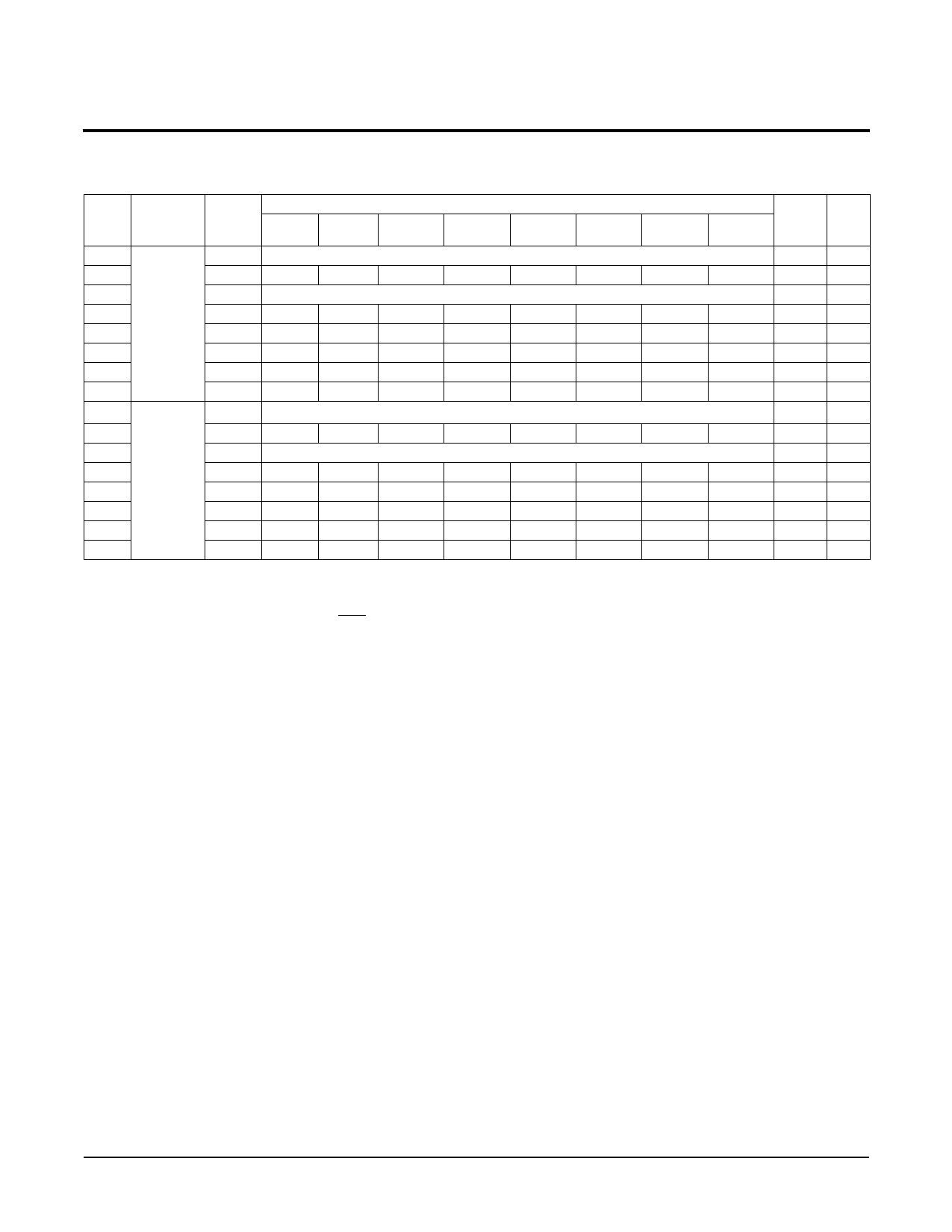

Table 1. Clock/Control Memory Map (Continued)

Addr.

000F

000E

000D

000C

000B

000A

0009

0008

0007

0006

0005

0004

0003

0002

0001

0000

Type

Alarm1

(EEPROM)

Alarm0

(EEPROM)

Reg

Name

Y2K1

DWA1

YRA1

MOA1

DTA1

HRA1

MNA1

SCA1

Y2K0

DWA0

YRA0

MOA0

DTA0

HRA0

MNA0

SCA0

7

EDW1

EMO1

EDT1

EHR1

EMN1

ESC1

EDW0

EMO0

EDT0

EHR0

EMN0

ESC0

Bit

65 4 3 2

Read-only - Default = 20h

0

1 (optional)

0 0 0 0 DY2 DY1 DY0

Unused - Default = RTC Year value (No EEPROM) - Future expansion

0 0 A1G20 A1G13 A1G12 A1G11 A1G10

0 A1D21 A1D20 A1D13 A1D12 A1D11 A1D10

0 A1H21 A1H20 A1H13 A1H12 A1H11 A1H10

A1M22 A1M21 A1M20 A1M13 A1M12 A1M11 A1M10

A1S22 A1S21 A1S20 A1S13 A1S12 A1S11 A1S10

Read-only - Default = 20h

0 0 0 0 DY2 DY1 DY0

Unused - Default = RTC Year value (No EEPROM) – Future expansion

0 0 A0G20 A0G13 A0G12 A0G11 A0G10

0 A0D21 A0D20 A0D13 A0D12 A0D11 A0D10

0 A0H21 A0H20 A0H13 A0H12 A0H11 A0H10

A0M22 A0M21 A0M20 A0M13 A0M12 A0M11 A0M10

A0S22 A0S21 A0S20 A0S13 A0S12 A0S11 A0S10

Range

20

0-6

1-12

1-31

0-23

0-59

0-59

20

0-6

1-12

1-31

0-23

0-59

0-59

20h

00h

00h

00h

00h

00h

00h

20h

00h

00h

00h

00h

00h

00h

When there is a match, an alarm flag is set. The occur-

rence of an alarm can be determined by polling the

AL0 and AL1 bits or by enabling the IRQ output, using

it as hardware flag.

The alarm enable bits are located in the MSB of the

particular register. When all enable bits are set to ‘0’,

there are no alarms.

– The user can set the X1286 to alarm every Wednes-

day at 8:00 AM by setting the EDWn*, the EHRn*

and EMNn* enable bits to ‘1’ and setting the DWAn*,

HRAn* and MNAn* Alarm registers to 8:00 AM

Wednesday.

– A daily alarm for 9:30PM results when the EHRn*

and EMNn* enable bits are set to ‘1’ and the HRAn*

and MNAn* registers are set to 9:30 PM.

*n = 0 for Alarm 0: N = 1 for Alarm 1

REAL TIME CLOCK REGISTERS

Clock/Calendar Registers (SSEC, SC, MN, HR, DT,

MO, YR)

These registers depict BCD representations of the

time. As such, SSEC (1/100 Second) range from 00 to

99, SC (Seconds) and MN (Minutes) range from 00 to

59, HR (Hour) is 1 to 12 with an AM or PM indicator

(H21 bit) or 0 to 23 (with MIL=1), DT (Date) is 1 to 31,

MO (Month) is 1 to 12, YR (Year) is 0 to 99. The SSEC

register is read-only.

Date of the Week Register (DW)

This register provides a Day of the Week status and

uses three bits DY2 to DY0 to represent the seven days

of the week. The counter advances in the cycle 0-1-2-

3-4-5-6-0-1-2-… The assignment of a numerical value

to a specific day of the week is arbitrary and may be

decided by the system software designer. The default

value is defined as ‘0’.

24 Hour Time

If the MIL bit of the HR register is 1, the RTC uses a

24-hour format. If the MIL bit is 0, the RTC uses a 12-

hour format and H21 bit functions as an AM/PM indica-

tor with a ‘1’ representing PM. The clock defaults to

standard time with H21=0.

Leap Years

Leap years add the day February 29 and are defined

as those years that are divisible by 4. Years divisible by

100 are not leap years, unless they are also divisible

by 400. This means that the year 2000 is a leap year,

the year 2100 is not. The X1286 does not correct for

the leap year in the year 2100.

STATUS REGISTER (SR)

The Status Register is located in the CCR memory

map at address 003Fh. This is a volatile register only

and is used to control the WEL and RWEL write enable

REV 1.1 7/8/04

www.intersil.com

11 of 26

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet X1286.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| X1286 | Intersil Real Time Clock/Calendar/CPU Supervisor with EEPROM X1286 | Intersil Corporation |

| X1288 | 2-Wire RTC Real Time Clock/Calendar/CPU Supervisor with EEPROM | Xicor |

| X1288 | RTC Real Time Clock/Calendar/CPU Supervisor | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |