|

|

PDF WM8143-12 Data sheet ( Hoja de datos )

| Número de pieza | WM8143-12 | |

| Descripción | 12-bit/4MSPS CCD Signal Processor | |

| Fabricantes | Wolfson Microelectronics plc | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WM8143-12 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

WM8143-12

12-bit/4MSPS CCD Signal Processor

Production Data Nov. 1999 Rev 4

Description

The WM8143-12 integrates the analogue signal

conditioning required by CCD sensors with a 12-bit ADC.

The WM8143-12 requires minimal external circuitry and

provides a cost-effective sensor to digital domain system

solution.

Each of the three analogue conditioning channels

includes reset level clamp, CDS, fine offset level shifting

and programmable gain amplification. The three channels

are multiplexed into the ADC. The output from the ADC is

fed to the output bus pins OP[11:0] via a 12/8 bit

multiplexer, enabled by the OEB signal.

The flexible output architecture allows twelve-bit data to

be accessed either on a twelve-bit bus or via a time-

multiplexed eight-bit bus. The WM8143-12 can be

configured for pixel-by-pixel or line-by-line multiplexing

operation. Reset level clamp and/or CDS features can be

optionally bypassed. The device configuration is

programmed either via a simple serial interface or via an

eight-bit parallel interface.

The serial/parallel interfaces of the WM8143-12 are

control compatible with those of the WM8144-10 and

WM8144-12.

Features

• Reset level clamp

• Correlated double sampling (CDS)

• Fine offset level shifting

• Programmable gain amplification

• 12-bit ADC with maximum 4 MSPS

• Simple clocking scheme

• Control by serial or parallel interface

• Time multiplexed eight-bit data output mode

• 32 pin TQFP package

• Interface compatible with WM8144-10 and

WM8144-12

Applications

• Flatbed scanners

• Sheet feed scanners

• Film scanners

• CCD sensor interfaces

• Contact image sensor (CIS) interfaces

Block Diagram

VRLC

VRU VRT

VRB

VMID

VSMP MCLK RLC

AGND DGND DVDD AVDD

VMID

RINP

GINP

BINP

CL RS VS

S/H

S/H

CDS

S/H

S/H

CDS

MUX

PGA

5-BIT REG

PGA

5-BIT REG

S/H

S/H

CDS

PGA

5-BIT REG

TIMING CONTROL

OFFSET

++

8-BIT +

SIGN DAC

VMID

OFFSET

++

8-BIT +

SIGN DAC

VMID

OFFSET

++

8-BIT +

SIGN DAC

VMID

M

U

X

WM8143-12

12-bit

ADC

12/8

MUX

CONFIGURABLE

SERIAL/PARALLEL

CONTROL INTERFACE

OEB

OP[11:0]

SDI / DNA

SCK / RNW

SEN / STB

NRESET

Production Data datasheets contain

final specifications current on

publication date. Supply of products

conforms to Wolfson

Microelectronics' terms and

conditions.

Wolfson Microelectronics ©1999 Wolfson Microelectronics Ltd.

Lutton Court, Bernard Terrace, Edinburgh, EH8 9NX, UK

Tel: +44 (0) 131 667 9386 Fax +44 (0) 131 667 5176

email: [email protected]

www: http://www.wolfson.co.uk

1 page

Production Data

WM8143-12

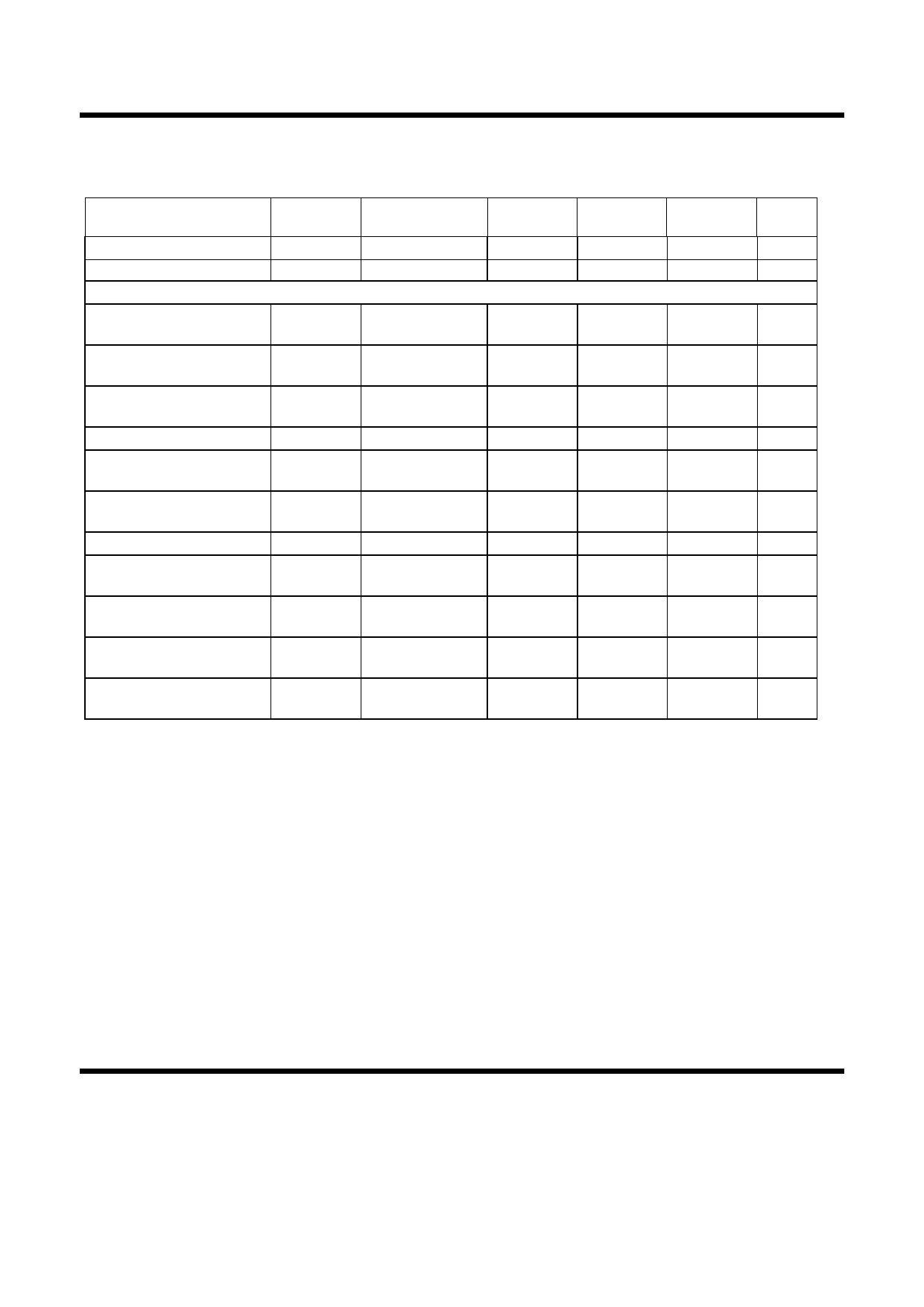

Test Characteristics

AVDD = DVDD = 4.75V to 5.25V, AGND = DGND = 0V … TA = 0oC to +70oC, MCLK = 8MHz, unless otherwise stated

PARAMETER

SYMBOL

Set up Time - SEN to SCK

SEN Pulse Width

Parallel Interface

RNW Low to OP[11:4] Tri-

state

Address Setup Time to STB

Low

DNA Low Setup Time to STB

Low

Strobe Low Time

Address Hold Time from STB

High

DNA Low Hold Time from

STB High

Data Setup Time to STB Low

DNA High Setup Time to STB

Low

Data Hold Time from STB

High

Data High Hold Time from

STB High

RNW High to OP[11:4]

Output

tSEC

tSEW

tOPZ

tASU

tADLS

tSTB

tAH

tADLH

tDSU

tADHS

tDH

tADHH

tOPD

TEST

CONDITIONS

MIN

20

50

0

10

50

10

10

0

10

10

10

0

TYP

MAX

20

UNIT

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Wolfson Microelectronics

5

PD. Rev 4 Nov. 99

5 Page

Production Data

WM8143-12

MCLK

VSMP

RLC 1

Input video

r,g,b

X

X0X

r,g,b

RLC on this pixel

X 0X

r,g,b

No RLC on this pixel

Figure 7 RLC TimingVideo Sampling Options

Video Sampling Options

The WM8143-12 can interface to CCD sensors using

six basic modes of operation (summarised in Table 3).

Mode configurations are controlled by a combination of

control bits and timing applied to MCLK and VMSP

pins. The default operational mode is mode 1: colour

with CDS enabled.

Colour Mode Definition (Mode 1)

Figure 9 summarises the timing relationships. MCLK is

applied at twice the required ADC conversion rate.

Synchronisation of sampling and channel multiplexing

to the incoming video signal is performed by the VSMP

pulse (active high). The three input channels (R,G,B)

are sampled in parallel on the rising edge of MCLK

following a VSMP pulse. The sampled data is

multiplexed into a single data stream at three times the

VSMP rate and passes through the internal pipeline

and emerges on the OP[11:0] bus. Both Correlated

Double Sampling (CDS) and Single Ended modes of

operation are available.

Monochrome Mode Definitions

One input channel is continuously sampled on the

rising edge of MCLK following a VSMP pulse. The user

can specify which input channel (R,G,B) is to be

sampled by writing to the WM8143-12 internal control

registers. There are four separate monochrome modes

with different maximum sample rates and CDS

availability.

Monochrome Mode (Mode 2)

Figure 10 summarises the timing relationships. The

timing in this mode is identical to mode 1 except that

one input channel is sampled three times (due to the

multiplexer being held in one position) and passes

through the device as three separate samples. The last

two samples can be ignored at the output OP[11:0].

Fast Monochrome Mode (Mode 3)

Figure 11 summarises the timing relationships. This

mode allows the maximum sample rate to be increased

to 2.67 MSPS. This is achieved by altering the

MCLK:VSMP ratio to 3:1. In this mode, the timing of

RS and CL must be fixed (refer to Table 3). The

sampled video data will pass through the internal

pipeline and emerge on the OP[11:0] bus.

Max. Speed Monochrome Mode (Mode 4)

Figure 12 summarises the timing relationships. This

mode allows the maximum sample rate to be increased

to 4 MSPS. This is achieved by altering the

MCLK:VSMP ratio to 2:1. The latency through the

device is identical to modes 1 and 2. CDS is not

available in this mode.

Slow Colour Mode (Mode 5)

Figure 13 summarises the timing relationships. This

mode is identical to Mode 1 except that the MCLK to

VSMP ratio is 8 : 1 and the maximum sample rate is 1

MSPS. To obtain a ratio of 4:4 between the video

sample position and the reset sample position, Setup

Register 3 CDSREF1-0 control bits b[5:4] should be set

to 10. The first three of the four output words are valid.

Slow Monochrome Mode (Mode 6)

Figure 14 summarises the timing relationships. This

mode is identical to mode 2 except that the MCLK to

VSMP ratio is 8 : 1 and the maximum sample rate is 1

MSPS. To obtain a ratio of 4:4 between the video

sample position and the reset sample position, Setup

Register 3 CDSREF 1-0 control bits b[5:4] should be

set to 10. The first of the four output words is the only

valid output.

Input Impedance

The input impedance of the WM8143-12 is dependent

upon the sampling frequency of the input signal and the

gain that the PGA is set to. This is due to the effective

capacitance of the ‘sample and hold’ circuits (Figure 8).

RINP/VMID

S/H

C

VMID

PGA

VS/RS

Figure 8 Input Impedance S/H Circuit

Wolfson Microelectronics

PD. Rev 4 Nov. 99

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet WM8143-12.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WM8143-10 | 10-bit/6MSPS CCD Signal Processor | Wolfson Microelectronics plc |

| WM8143-12 | 12-bit/4MSPS CCD Signal Processor | Wolfson Microelectronics plc |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |