|

|

PDF W78L52-24 Data sheet ( Hoja de datos )

| Número de pieza | W78L52-24 | |

| Descripción | 8-BIT MICROCONTROLLER | |

| Fabricantes | Winbond | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W78L52-24 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

W78L52

8-BIT MICROCONTROLLER

GENERAL DESCRIPTION

The W78L52 microcontroller supplies a wider frequency and supply voltage range than most 8-bit

microcontrollers on the market. It is compatible with the industry standard 80C52 microcontroller

series. The W78L52 contains four 8-bit bidirectional parallel ports, one extra 4-bit bit-addressable I/O

port (Port 4) and two additional external interrupts (INT2 , INT3 ), three 16-bit timer/counters, one

watchdog timer and a serial port. These peripherals are supported by a eight-source, two-level

interrupt capability. There are 256 bytes of RAM and an 8K byte mask ROM for application

programs.

The W78L52 microcontroller has two power reduction modes, idle mode and power-down mode, both

of which are software selectable. The idle mode turns off the processor clock but allows for continued

peripheral operation. The power-down mode stops the crystal oscillator for minimum power

consumption. The external clock can be stopped at any time and in any state without affecting the

processor.

FEATURES

• Fully static design

• Supply voltage of 1.8V to 5.5V

• DC-24 MHz operation

• 256 bytes of on-chip scratchpad RAM

• 8K bytes of on-chip mask ROM

• 64K bytes program memory address space

• 64K bytes data memory address space

• Four 8-bit bidirectional ports

• Three 16-bit timer/counters

• One full duplex serial port

• Eight-source, two-level interrupt capability

• One extra 4-bit bit-addressable I/O port

• Two additional external interrupts INT2 / INT3

• Watchdog timer

• EMI reduction mode

• Built-in power management

• Code protection

• Packages:

− DIP 40: W78L52-24

− PLCC 44: W78L52P-24

− QFP 44: W78L52F-24

Publication Release Date: January 1999

- 1 - Revision A2

1 page

W78L52

FUNCTIONAL DESCRIPTION

The W78L52 architecture consists of a core controller surrounded by various registers, five general

purpose I/O ports, 256 bytes of RAM, three timer/counters, one watchdog timer and a serial port. The

processor supports 111 different opcodes and references both a 64K program address space and a

64 K data storage space.

Timers 0, 1, and 2

Timers 0, 1, and 2 each consist of two 8-bit data registers. These are called TL0 and TH0 for Timer

0, TL1 and TH1 for Timer 1, and TL2 and TH2 for Timer 2. The TCON and TMOD registers provide

control functions for timers 0, 1. The T2CON register provides control functions for Timer 2. RCAP2H

and RCAP2L are used as reload/capture registers for Timer 2. The operations of Timer 0 and Timer

1 are the same as in the W78L51. Timer 2 is a special feature of the W78L52: it is a 16-bit

timer/counter that is configured and controlled by the T2CON register. Like Timers 0 and 1, Timer 2

can operate as either an external event counter or as an internal timer, depending on the setting of

bit C/T2 in T2CON. Timer 2 has three operating modes: capture, auto-reload, and baud rate

generator. The clock speed at capture or auto-reload mode is the same as that of Timers 0 and 1.

Clock

The W78L52 is designed to be used with either a crystal oscillator or an external clock. Internally, the

clock is divided by two before it is used. This makes the W78L52 relatively insensitive to duty cycle

variations in the clock.

Crystal Oscillator

The W78L52 incorporates a built-in crystal oscillator. To make the oscillator work, a crystal must be

connected across pins XTAL1 and XTAL2. In addition, a load capacitor must be connected from each

pin to ground, and a resistor must also be connected from XTAL1 to XTAL2 to provide a DC bias

when the crystal frequency is above 24 MHz.

External Clock

An external clock should be connected to pin XTAL1. Pin XTAL2 should be left unconnected. The

XTAL1 input is a CMOS-type input, as required by the crystal oscillator. As a result, the external clock

signal should have an input one level of greater than 3.5 volts when VDD = 5 volts.

Power Management

Idle Mode

The idle mode is entered by setting the IDL bit in the PCON register. In the idle mode, the internal

clock to the processor is stopped. The peripherals and the interrupt logic continue to be clocked. The

processor will exit idle mode when either an interrupt or a reset occurs.

Power-down Mode

When the PD bit of the PCON register is set, the processor enters the power-down mode. In this

mode all of the clocks, including the oscillator are stopped. The only way to exit power-down mode is

by a reset.

Reset

The external RESET signal is sampled at S5P2. To take effect, it must be held high for at least two

machine cycles while the oscillator is running. An internal trigger circuit in the reset line is used to

deglitch the reset line when the W78L52 is used with an external RC network. The reset logic also has

Publication Release Date: January 1999

- 5 - Revision A2

5 Page

W78L52

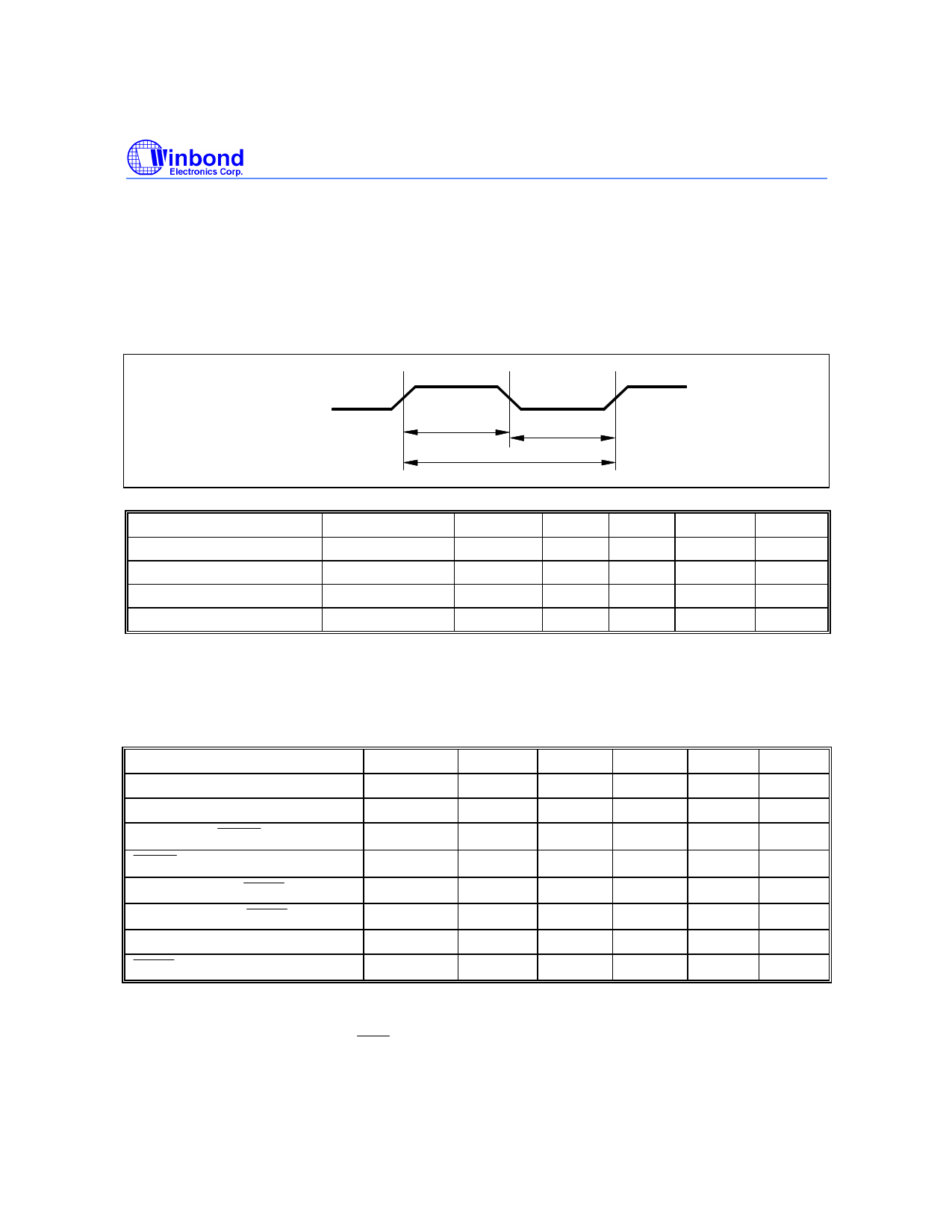

AC CHARACTERISTICS

The AC specifications are a function of the particular process used to manufacture the part, the

ratings of the I/O buffers, the capacitive load, and the internal routing capacitance. Most of the

specifications can be expressed in terms of multiple input clock periods (TCP), and actual parts will

usually experience less than a ±20 nS variation. The numbers below represent the performance

expected from a 0.5 micron CMOS process when using 2 and 4 mA output buffers.

Clock Input Waveform

XTAL1

TCH

TCL

F OP, TCP

PARAMETER

SYMBOL

MIN.

Operating Speed

FOP

0

Clock Period

TCP 25

Clock High

TCH 10

Clock Low

TCL 10

Notes:

1. The clock may be stopped indefinitely in either state.

2. The TCP specification is used as a reference in other specifications.

3. There are no duty cycle requirements on the XTAL1 input.

TYP.

-

-

-

-

MAX.

24

-

-

-

UNIT

MHz

nS

nS

nS

NOTES

1

2

3

3

Program Fetch Cycle

PARAMETER

SYMBOL MIN.

Address Valid to ALE Low

TAAS

1 TCP-∆

Address Hold from ALE Low

TAAH

1 TCP-∆

ALE Low to PSEN Low

TAPL

1 TCP-∆

PSEN Low to Data Valid

TPDA

-

Data Hold after PSEN High

TPDH

0

Data Float after PSEN High

TPDZ

0

ALE Pulse Width

TALW

2 TCP-∆

PSEN Pulse Width

TPSW

3 TCP-∆

Notes:

1. P0.0−P0.7, P2.0−P2.7 remain stable throughout entire memory cycle.

2. Memory access time is 3 TCP.

3. Data have been latched internally prior to PSEN going high.

4. "∆" (due to buffer driving delay and wire loading) is 20 nS.

TYP.

-

-

-

-

-

-

2 TCP

3 TCP

MAX.

-

-

-

2 TCP

1 TCP

1 TCP

-

-

UNIT

nS

nS

nS

nS

nS

nS

nS

nS

NOTES

4

1, 4

4

2

3

4

4

- 11 -

Publication Release Date: January 1999

Revision A2

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet W78L52-24.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W78L52-24 | 8-BIT MICROCONTROLLER | Winbond |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |