|

|

PDF PCF8594C-2P02 Data sheet ( Hoja de datos )

| Número de pieza | PCF8594C-2P02 | |

| Descripción | 512 X 8-bit CMOS EEPROM with I2C-bus interface | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCF8594C-2P02 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

PCF8594C-2

512 × 8-bit CMOS EEPROM with I2C-bus interface

Rev. 05 — 25 October 2004

Product data

1. Description

The PCF8594C-2 is a floating gate Electrically Erasable Programmable Read Only

Memory (EEPROM) with 4 kbits (512 × 8-bit) non-volatile storage. By using an

internal redundant storage code, it is fault tolerant to single bit errors. This feature

dramatically increases the reliability compared to conventional EEPROMs. Power

consumption is low due to the full CMOS technology used. The programming voltage

is generated on-chip, using a voltage multiplier.

Data bytes are received and transmitted via the serial I2C-bus. Up to four

PCF8594C-2 devices may be connected to the I2C-bus. Chip select is accomplished

by two address inputs (A1 and A2).

Timing of the E/W cycle is carried out internally, thus no external components are

required. Programming Time Control (PTC), Pin 7, must be connected to either VDD

or left open-circuit. There is an option of using an external clock for timing the length

of an E/W cycle.

2. Features

s Low power CMOS:

x 2.0 mA maximum operating current

x maximum standby current 10 µA (at 6.0 V), typical 4 µA

s Non-volatile storage of 4 kbits organized as 512 × 8-bit

s Single supply with full operation down to 2.5 V

s On-chip voltage multiplier

s Serial input/output I2C-bus

s Write operations:

x byte write mode

x 8-byte page write mode (minimizes total write time per byte)

s Read operations:

x sequential read

x random read

s Internal timer for writing (no external components)

s Internal power-on reset

s 0 kHz to 100 kHz clock frequency

s High reliability by using a redundant storage code

s Endurance: 1,000,000 Erase/Write (E/W) cycles at Tamb = 22 °C

s 10 years non-volatile data retention time

1 page

Philips Semiconductors

PCF8594C-2

512 × 8-bit CMOS EEPROM with I2C-bus interface

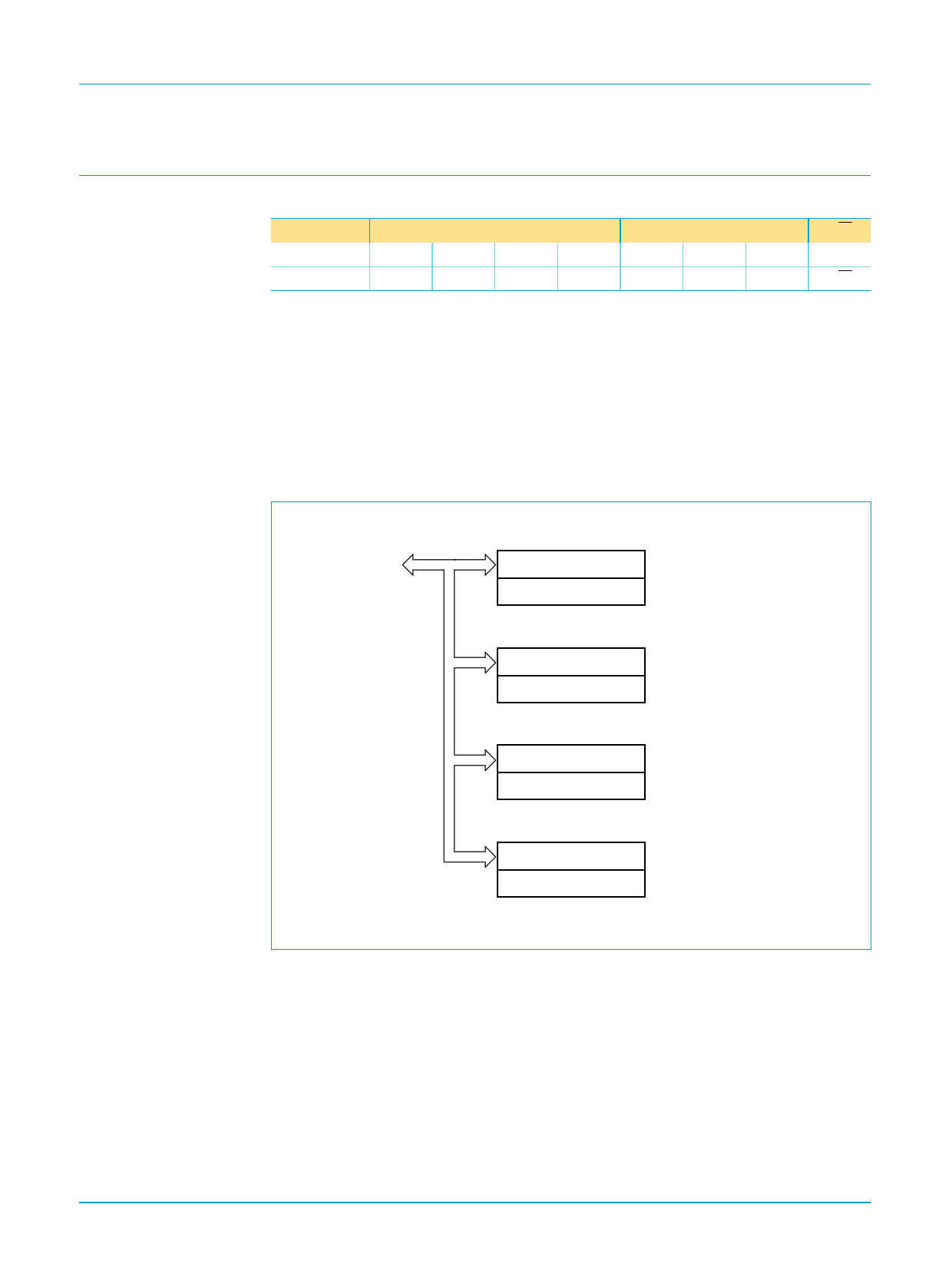

7. Device addressing

Table 5: Device address code

Selection

Device code

Bit

b7[1]

b6

b5

Device

101

b4

0

[1] The Most Significant Bit (MSB) ‘b7’ is sent first.

Chip Enable

b3 b2 b1

A2 A1 A0

R/W

b0

R/W

A2 and A1 are hardware selectable pins and A0 is software selectable pin.

A system could have up to four PCF8594C-2 devices on the same I2C-bus,

equivalent to a 16 kbit EEPROM or 4 devices of 512 bytes of memory.

A0 selects the lower (logic level ‘0’) or the higher (logic level ‘1’) 256-byte page on the

selected device. The device is selected by bits A2 and A1. Figure 3 shows the various

address and page combinations.

I2C-BUS

PCF8594C-2

DEVICE 1

A2 A1 A0

HIGHER 256-BYTE PAGE 0 0 1

LOWER 256-BYTE PAGE 0 0 0

PCF8594C-2

DEVICE 2

HIGHER 256-BYTE PAGE 0 1 1

LOWER 256-BYTE PAGE 0 1 0

PCF8594C-2

DEVICE 3

HIGHER 256-BYTE PAGE 1 0 1

LOWER 256-BYTE PAGE 1 0 0

Fig 3. Device addressing.

PCF8594C-2

DEVICE 4

HIGHER 256-BYTE PAGE 1 1 1

LOWER 256-BYTE PAGE 1 1 0

002aaa260

9397 750 14221

Product data

Rev. 05 — 25 October 2004

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

5 of 21

5 Page

Philips Semiconductors

PCF8594C-2

512 × 8-bit CMOS EEPROM with I2C-bus interface

Table 7: Characteristics…continued

VDD = 2.5 V to 6.0 V; VSS = 0 V; Tamb = −40 °C to +85 °C; unless otherwise specified.

Symbol Parameter

Conditions

Min

SDA input/output (pin 5)

VIL LOW level input voltage

−0.8

VIH HIGH level input voltage

0.7VDD

VOL

LOW level output voltage

IOL = 3 mA; VDD(min)

-

ILO output leakage current

VOH = VDD

-

Ci input capacitance

VI = VSS

-

Data retention time

tS data retention time

Tamb = 55 °C

10

Typ

-

-

-

-

-

−

11. I2C-bus characteristics

Max

0.3VDD

+6.5

0.4

1

7

−

Unit

V

V

V

µA

pF

years

Table 8: I2C-bus characteristics

All of the timing values are valid within the operating supply voltage and ambient temperature range and refer to VIL and VIH

with an input voltage swing from VSS to VDD; see Figure 9.

Symbol

Parameter

Conditions

Min Max Unit

fSCL clock frequency

tBUF bus free time between a STOP and

START condition

0 100 kHz

4.7 −

µs

tHD;STA

START condition hold time after

which first clock pulse is generated

4.0 −

µs

tLOW

tHIGH

tSU;STA

LOW level clock period

HIGH level clock period

set-up time for START condition

repeated start

4.7 −

4.0 −

4.7 −

µs

µs

µs

tHD;DAT

data hold time

for bus compatible masters

5 − µs

for bus devices

[1] 0 − ns

tSU;DAT

tr

tf

tSU;STO

data set-up time

SDA and SCL rise time

SDA and SCL fall time

set-up time for STOP condition

250 −

ns

− 1 µs

− 300 ns

4.0 −

µs

[1] The hold time required (not greater than 300 ns) to bridge the undefined region of the falling edge of SCL must be internally provided by

a transmitter.

9397 750 14221

Product data

Rev. 05 — 25 October 2004

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

11 of 21

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet PCF8594C-2P02.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCF8594C-2P02 | 512 X 8-bit CMOS EEPROM with I2C-bus interface | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |