|

|

PDF UPD16681 Data sheet ( Hoja de datos )

| Número de pieza | UPD16681 | |

| Descripción | LCD CONTROLLER/DRIVER FOR DOT MATRIX DISPLAY OF JIS LEVEL 1 AND JIS LEVEL 2 KANJI SETS | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD16681 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATA SHEET

MOS INTEGRATED CIRCUIT

µ PD16681

LCD CONTROLLER/DRIVER FOR DOT MATRIX DISPLAY OF JIS LEVEL 1

AND JIS LEVEL 2 KANJI SETS

DESCRIPTION

The µPD16681 is a single-chip controller driver that can display Japanese text; including JIS Level 1 kanji, JIS Level

2 kanji, hiragana, and katakana. Each chip can display up to four lines containing up to eight full width characters (11

x 12 dots), or up to four lines containing up to 16 half width characters (5 x 12 dots), as well 96 pictographs.

FEATURES

• LCD controller/driver for dot matrix display of JIS Level 1 and JIS Level 2 kanji sets

• On-chip ROM for character generation

−JIS Level 1 + Level 2 kanji (11 x 12 dots) : 6,355 characters

−JIS non-kanji characters (11 x 12 dots) : 453 characters

−Other characters (symbols, etc.) (11 x 12 dots): 256 characters

−Half width alphanumeric characters (5 x 12 dots) : 192 characters

• On-chip RAM for character generation

−8 types (12 x 13 dots)

• On-chip boost circuit : switchable between 3x and 4x modes

• RAM for pictograph data displays : 96 bits

• Outputs : 96 segments, 52 commons

• Duty settings : 1/39 or 1/52

• Switchable data inputs : serial or 8-bit parallel

• On-chip divider resistor

• Selectable bias settings (1/8 bias, 1/7 bias, or 1/6 bias)

• On-chip oscillation circuit

ORDERING INFORMATION

Part number

µPD16681W-011

µPD16681P-011

Package

Wafer

Chip (COG compliant)

ROM code

Standard

Standard

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. S13104EJ5V0DS00(5th edition)

Date Published November 1999 NS CP(K)

Printed in Japan

The mark 5 shows major revised points.

©

1999

1 page

µPD16681

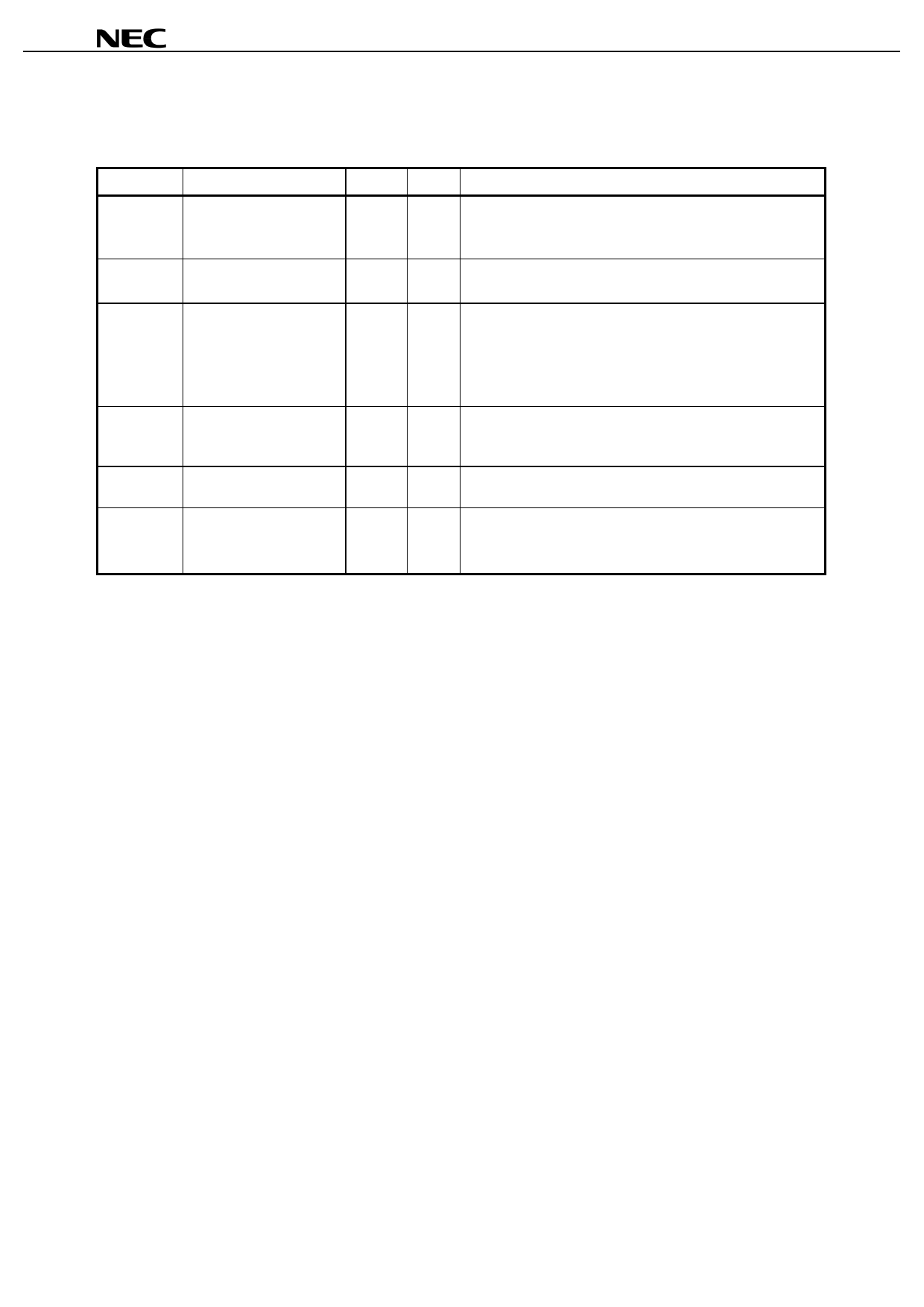

3. PIN FUNCTIONS

3.1 Power Supply System Pins

Pin Symbol

Pin Name

VDD Logic power supply pin

Boost circuit power supply

pin

VSS Logic ground

Driver ground

VLCD

Driver power supply pins

Pad No.

50-54

55-59

29-31

VLC1 - VLC5

Reference power supply

pins for driver

14-28

VLCBS1 - VLCBS3 Bias value setting pins

C1+, C1-

C2+, C2-

C3+, C3-

Capacitor connection pins

2-7

32-49

I/O Description

− Power supply pins for logic and boost circuit

− Ground pins for logic and driver circuit

− Power supply pins for driver. Output pin for internal boost circuit.

Connect a 1-µF capacitor between these pins and the VSS pins

for boosting.

If not using the internal boost circuit, a direct driver power supply

can be input.

− These are reference power supply pins for the LCD driver.

Leave these pins open if an internal bias has been selected.

Connect a capacitor to ground.

− When selecting an internal bias, the bias value can be changed

connecting these pins outside of the IC.

− These are capacitor connection pins for the boost circuit.

Connect a 1-µF capacitor.

Data Sheet S13104EJ5V0DS00

5

5 Page

µPD16681

4.4 Control of Op Amp for Level Power Supply

Input to the AMPCHA pin is used to control the op amp for the LCD driver level power supply.

• High power mode (AMPCHA = L)

This mode maximizes the LCD drive current supply capacity in the op amp for the LCD driver level power supply.

• Normal mode (AMPCHA = H)

This mode uses a lower LCD drive current supply capacity in the op amp for the LCD driver level power supply,

which is suitable for charging the capacitor used to stabilize the external level.

Caution For either mode, be sure to connect a level stabilization capacitor (rated from about 0.1 to 1.0 µF)

for the VLC1 to VLC5 pins. Poorer display quality results when these capacitors are not connected.

Figure 4-4. Reference Voltage Circuit

AMPOUT

VLC1

R

+

−

Output to SEG and COM

VLC2

R

+

−

Output to SEG and COM

VLC3

VLCBS1

+

−

R

VLCBS2

Output to SEG and COM

Op amp for level driver

R

VLCBS3

2R

VLC4

R

VLC5

R

VSS

+

−

+

−

Output to SEG and COM

Output to SEG and COM

Output to SEG and COM

Data Sheet S13104EJ5V0DS00

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UPD16681.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD16680 | 1/53/ 1/40 DUTY/ LCD CONTROLLER/DRIVER WITH BUILT-IN RAM | NEC |

| UPD16680P | 1/53/ 1/40 DUTY/ LCD CONTROLLER/DRIVER WITH BUILT-IN RAM | NEC |

| UPD16680W | 1/53/ 1/40 DUTY/ LCD CONTROLLER/DRIVER WITH BUILT-IN RAM | NEC |

| UPD16681 | LCD CONTROLLER/DRIVER FOR DOT MATRIX DISPLAY OF JIS LEVEL 1 AND JIS LEVEL 2 KANJI SETS | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |