|

|

PDF UPB1007K Data sheet ( Hoja de datos )

| Número de pieza | UPB1007K | |

| Descripción | PLL FREQUENCY SYNTHESIZER | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPB1007K (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

NEC's 3 V DUAL

DOWNCONVERTER AND UPB1007K

PLL FREQUENCY SYNTHESIZER

FEATURES

DESCRIPTION

• INTEGRATED RF BLOCK:

LNA, RF & IF Downconverter + PLL frequency

synthesizer

• STATE OF THE ART 25 GHz fT UHS0 BIPOLAR

PROCESS

• DOUBLE-CONVERSION: f1stIF = 61.380 MHz

f2ndIF = 4.092 MHz

• ADJUSTABLE GAIN: 20 dB range MIN

• FIXED DIVISION PRESCALER

• LOW POWER CONSUMPTION: 25 mA @ 3 V

NEC's UPB1007K is a Silicon RFIC designed for low cost GPS

receivers. The IC combines an LNA, followed by a double-

conversion RF/IF downconverter block and a PLL frequency

synthesizer on one chip. The device operates on a 3V supply

voltage and is housed in a small 36 pin QFN (Quad Flat No-

lead) package, resulting in low power consumption and re-

duced board space. The device is manufactured using the

state of the art UHS0 25 GHz fT silicon bipolar process.

NEC's stringent quality assurance and test procedures en-

sure the highest reliability and performance.

• SMALL 36 PIN QFN PACKAGE

Flat lead style for better performance

APPLICATIONS

• TAPE AND REEL PACKAGING AVAILABLE

• LOW POWER HANDHELD GPS RECEIVER

• IN-VEHICLE NAVIGATION SYSTEMS

• PC/PDA+GPS INTEGRATION

ELECTRICAL CHARACTERISTICS (TA = 25°C, VCC = 3.0 V, unless otherwise specified)

PART NUMBER

PACKAGE OUTLINE

UPB1007K

QFN-36

SYMBOLS

PARAMETERS AND CONDITIONS

UNITS

MIN

TYP

MAX

ICC Total Circuit Current, No Signals

mA

25 31

VCC Supply Voltage

V 2.7

3.0

3.3

LNA (fRFin = 1575.42 MHz, ZL = ZS = 50 Ω)

ZLNAin

RF Input Impedance of LNA

Ω 28 - j38

ZLNAop RF Output Impedance of LNA

Ω 85 - jx6

P1dBLNA 1 dB Compression, Input matched

dBm

-22

PGLNA Power Gain LNA, Input matched, PRFin = -60 dBm

dB

14

15

NFLNA Noise Figure of LNA, Input matched

dB

2.8

Mixer (fRFin = 1575.42 MHz, f1stLOin = 1636.80 MHz, PLO = -10 dBm, f1stIF = 61.38 MHz, ZL = ZS = 50 Ω)

ZMIXin

RF Input Impedance of Mixer

Ω 31 -j103

P1dBMIX 1 dB Compression (refer to input), Input matched

dBm

-25

PCGMIX Power Conversion Gain

dB 21

NFMIX Noise Figure of Mixer (SSB), Input matched

dB

9.5

ALO-IF

LO Leakage to IF Pins, PLO = -10 dBm

dBm

-40

ALO-RF LO Leakage to RF Input Pins, PLO = -10 dBm

dBm

-48

ZMIXout RF Output Impedance of Mixer

+152 - j9

PLL

ICPOH

PLL Charge Pump High Side Current @ VCPout = VCC/2

mA

1

ICPOL

PLL Charge Pump Low Side Current @ VCPout = VCC/2

mA

-1

fPD Phase Comparison Frequency

MHz

8.184

IF Downconverter Block (f1stIFin = 61.38 MHz, f2ndLOin = 65.472 MHz, f2ndIF output = 4.092 MHz, ZS = 2kΩ, ZL = 2 kΩ)

NF2ndMIX Noise Figure of 2nd IF Mixer (SSB), (ZS = 50Ω)

dB

12

GV2ndMIX Voltage Gain of 2nd Mixer/Amplifier, P1stIF = -50 dBm

dB

47

VGC Gain Control Voltage (Voltage at maximum gain)

V

0.5

DGC

Gain Control Range, P1stIF = -50 dBm

(Voltage at maximum gain)

dB 20

A2ndLO1stIF 2nd LO Isolation to 1st IF Input Pins, VAGC = 0 V

dB

-70

A2ndLO2ndIF 2nd LO Isolation to 2nd IF Output Pins, VAGC = 0 V

dB

-70

3.2

10

California Eastern Laboratories

1 page

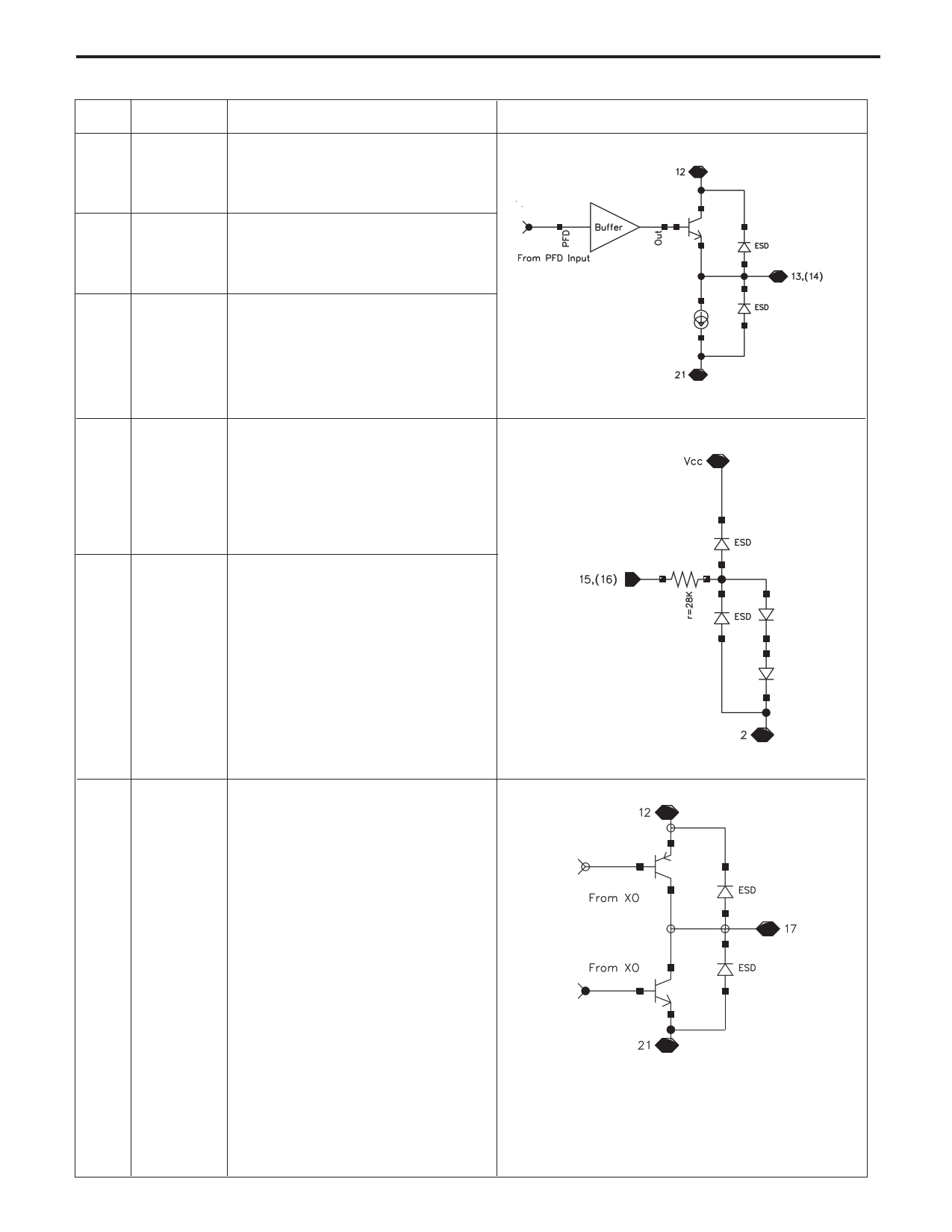

PIN FUNCTIONS

Pin No.

Symbol

Function and Application

12 VCC Supply voltage pin of prescaler, phase

detector, crystal oscillator, VCO buffer.

(Divider Block)

13 LO_out Monitor pin of frequency at phase

detector.

14

XO_out

Monitor pin of oscillator ÷2 output at

phase detector.

15 PD1 Power down control pin

Low = Whole chip off except XTAL osc.

High = Whole chip on except XTAL osc.

16 PD2 Reference block standby mode.

Low = Reference block disabled.

High = Reference block enabled.

UPB1007K

Internal Equivalent Circuit

17 REFout Output pin of reference frequency. The

frequency from pin 17 can be taken out as

1Vp-p swing.

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet UPB1007K.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPB1007K | PLL FREQUENCY SYNTHESIZER | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |