|

|

PDF PCD3316T Data sheet ( Hoja de datos )

| Número de pieza | PCD3316T | |

| Descripción | Caller-ID on Call Waiting CIDCW receiver | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCD3316T (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PCD3316

Caller-ID on Call Waiting (CIDCW) receiver

11 March 1999

Product specification

1. General description

The PCD3316 is a low power mixed signal CMOS integrated circuit for receiving

physical layer signals like Bellcore’s ‘CPE1 Alerting Signal (CAS)’ and the signals

used in similar services. The device is capable of a very high precision detection of

the dual tone (2130 and 2750 Hz) by using a patented digital algorithm. The

PCD3316 can be used for on-hook and off-hook Caller-ID (CID), Caller-ID on Call

Waiting (CIDCW) and Caller-Name (CNAM) applications.

For timing purposes the PCD3316 can be programmed to generate an interrupt

signal to the microcontroller every second or every minute. These timings are derived

from an on-chip 32.768 kHz oscillator.

Also incorporated in the device are a Frequency Shift Keying (FSK)

receiver/demodulator and a ‘Ring or polarity change detector’. The status of the

PCD3316, the received FSK data bytes and the ringer period can be read and many

options can be selected via the I2C-bus serial interface. Two on-chip oscillators are

available. One 3.58 MHz oscillator for all internal functions and a low frequency

32.768 kHz oscillator for the 1 second or 1 minute timing.

In Power-down mode only the polarity comparators and the 32.768 kHz oscillator are

c active. The CAS detection, the FSK receiver and the 3.58 MHz oscillator can be

c

enabled separately. Detection of a polarity change on the inputs POL0 or POL1, the

reception of an FSK data byte, the detection of a CAS tone or a timebase interrupt is

signalled to the microcontroller by an interrupt request signal (IRQ). The

microcontroller can communicate with the PCD3316 device via the serial interface.

The PCD3316 is designed for use in a microcontroller controlled system. The device

is available in a SO16 package.

A demonstration board OM5843 and an application note AN98071 are available.

1. CPE = Customer Premises Equipment.

1 page

Philips Semiconductors

PCD3316

CIDCW receiver

They can be used for ring or line polarity reversal detection. The POL on/off bit (Mode

register 1, bit 4) must be set to enable generation of an interrupt when a polarity

change occurs. The result of the two comparators can be read in bits 7 and 6 (POL0

and POL1) of the Status register (see Section 7.4). The 3.58 MHz clock is not needed

for the generation of a polarity interrupt.

7.2 CAS detection

After a power-on reset or after enabling the CAS detector the internal registers of the

CAS detection function are initialized. The initialization takes a maximum of

100 periods of the 3.58 MHz clock.

If the CAS detection is enabled the PCD3316 will generate an interrupt (Interrupt

register, bit 1 is set) when a correct dual tone (2130 and 2750 Hz) is detected.

Interrupts will be blocked when the signal level on the CAS input is below the

threshold in the level detector.

7.3 FSK reception

The FSK receiver function can be enabled by setting the FSK on/off bit (Mode

register 1, bit 7).

In the FSK transmission specification of BT and Bellcore a channel seizure is

transmitted first (sequence of 1010..). After the channel seizure a block of marks and

finally the data pattern are sent (see Figure 3). These mark bits are detected by the

PCD3316 which sets the FSK-BOM Indication bit (Status register, bit 4). The

FSK-BOM Indication bit is reset when the FSK receiver is disabled.

width

FSK transmission

channel seizure mark

data

9397 750 04824

Product specification

FSK-BOM

Fig 3. FSK transmission specification.

MBH979

If the FSK-BOM Indication bit is set, the FSK receiver will generate an interrupt after it

has received a complete data word. An FSK data word consists of one start bit

(space), followed by eight data bits and one stop bit (mark). Interrupts will therefore

not be generated during the channel seizure and during the block of marks. When a

valid data word has been received, FSK data is available in the FSK data register.

By clearing the FSK-BOM-mask on/off bit (Mode register 1, bit 6), the FSK receiver

will not wait with the generation of interrupts until a Begin Of Mark (BOM) has been

detected but will handle the channel seizure as normal data. The block of marks

which is a string of logic 1 will still not generate interrupts because there are no start

bits.

After the generation of an interrupt the IRQ pin will become active (see Figure 4), and

the FSK Interrupt bit is set (Interrupt register, bit 5). The received data is available in

the FSK data register.

11 March 1999

© Philips Electronics N.V. 1999. All rights reserved.

5 of 30

5 Page

Philips Semiconductors

PCD3316

CIDCW receiver

SDA

SCL

MASTER

TRANSMITTER /

RECEIVER

SLAVE

RECEIVER

Fig 9. I2C-bus configuration.

SLAVE

TRANSMITTER /

RECEIVER

MASTER

TRANSMITTER

MASTER

TRANSMITTER /

RECEIVER

MBA605

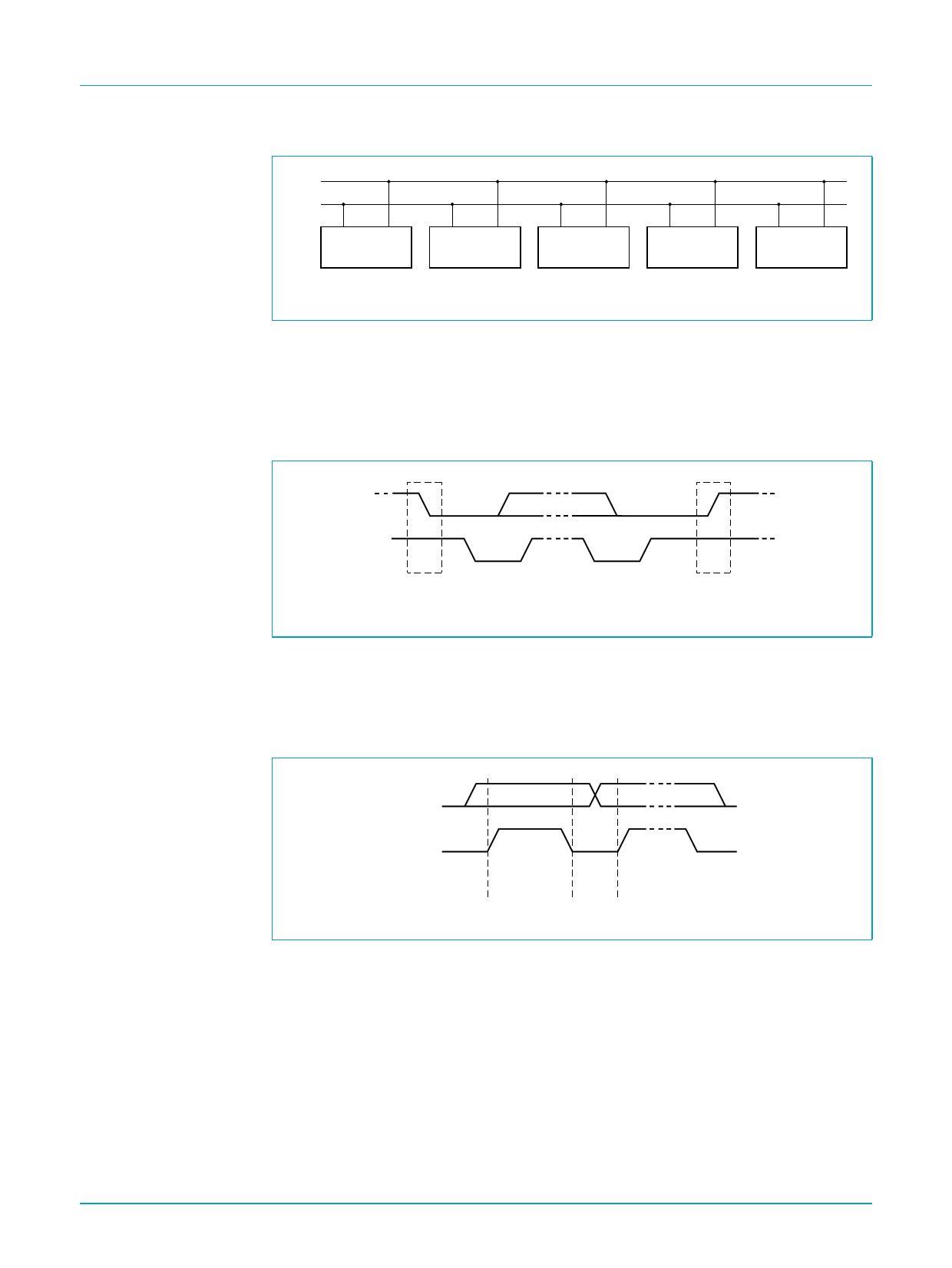

7.12.2 START and STOP conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW

transition of the data line, while the clock is HIGH is defined as the START condition

(S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as a

STOP condition (P); see Figure 10.

SDA

SDA

SCL

S

START condition

Fig 10. START and STOP conditions for the I2C-bus.

SCL

P

STOP condition

MBA608

7.12.3 Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must

remain stable during the HIGH period of the clock pulse as changes in the data line at

this time will be interpreted as a control signal; see Figure 11.

SDA

SCL

Fig 11. I2C-bus bit transfer.

data line

stable;

data valid

change

of data

allowed

MBA607

7.12.4 Acknowledge

The number of data bytes transferred between the START and the STOP conditions

from the transmitter to the receiver is unlimited. Each byte of eight bits is followed by

an acknowledge bit. The acknowledge bit is a HIGH level signal put on the bus by the

transmitter during which time the master generates an extra acknowledge-related

clock pulse.

A slave receiver which is addressed must generate an acknowledge after the

reception of each byte. Also a master receiver must generate an acknowledge after

the reception of each byte that has been clocked out of the slave transmitter.

9397 750 04824

Product specification

11 March 1999

© Philips Electronics N.V. 1999. All rights reserved.

11 of 30

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PCD3316T.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCD3316 | Caller-ID on Call Waiting CIDCW receiver | NXP Semiconductors |

| PCD3316T | Caller-ID on Call Waiting CIDCW receiver | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |