|

|

PDF PAC80 Data sheet ( Hoja de datos )

| Número de pieza | PAC80 | |

| Descripción | In-System Programmable Analog Circuit | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PAC80 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

ispPAC 80TM

In-System Programmable Analog Circuit

Features

• IN-SYSTEM PROGRAMMABLE (ISP™) ANALOG

— Instrument Amplifier Gain Stage

— Precision Active Filtering (50kHz to 500kHz)

— Continuous-Time Fifth Order Low Pass Topology

— Dual, A/B Configuration Memory

— Non-Volatile E2CMOS Cells

— IEEE 1149.1 JTAG Serial Port Programming

• UNIQUE FLEXIBILITY AND PERFORMANCE

— Programmable Gain Range (0dB to 20dB)

— Implements Multiple Filter Types: Elliptical,

Chebyshev, Bessel, Butterworth, Linear Phase,

Gaussian and Legendre

— Low Distortion (THD < -74dB max @ 100kHz)

— Auto-Calibrated Input Offset Voltage

• TRUE DIFFERENTIAL I/O

— High CMR (58dB) Instrument Amplifier Input

— 2.5V Common Mode Reference on Chip

— Rail-to-Rail Voltage Outputs

• SINGLE SUPPLY 5V OPERATION

— Power Dissipation of 165mW

— 16-Pin Plastic SOIC, PDIP Packages

• APPLICATIONS INCLUDE INTEGRATED

— Single +5V Supply Signal Conditioning

— Programmable Filters With Fully Differential I/O

— Analog Front Ends, 12-Bit Data Acq. Systems

— DSP System Front End Signal Conditioning

— High-Performance Reconstruction Filters

Typical Application Diagram

5V 5V

ispPAC80

Vin

12-Bit Differential

Input ADC

Ain+

Ain-

A/B & Gain

SPI Control

VREFout

Reference

5V

DSP

Functional Block Diagram

TMS 1

TCK 2

TDI 3

TDO 4

CS 5

CAL 6

ENSPI 7

GND 8

IA OA

5th Order LPF

E2CMOS Cfg A E2CMOS Cfg B

Ref & Auto-Cal

ISP Control

16 VS

15 TEST

14 OUT+

13 OUT–

12 TEST

11 IN+

10 IN–

9 VREFOUT

ispPAC80

Description

The ispPAC80 is a member of the Lattice family of In-System

Programmable analog circuits, digitally configured via non-

volatile E2CMOS® technology.

Analog building blocks, called PACell™(s), replace traditional

analog components such as opamps, eliminating the need for

external resistors and capacitors. With no requirement for

external configuration components, ispPAC80 expedites the

design process, simplifying prototype circuit implementation

and change, while providing high-performance integrated func-

tionality. With all components on chip, there is no longer a

concern of performance degradation due to component mis-

match or other external factors. The ispPAC80 provides reliable

and repeatable performance, every time.

Designers configure the ispPAC80 and verify its performance

using PAC-Designer™, an easy to use, Microsoft Windows®

compatible program. A filter configuration database is provided

whereby thousands of different configurations can be realized.

No special understanding of filter synthesis is required beyond

that of general specifications such as corner frequency and

stopband attenuation, etc. The software lists the possible

choices that meet the designer’s specifications which can then

be loaded directly into either of two device

(A/B) configurations from the lookup table. Device program-

ming is supported using PC parallel port I/O operations.

The ispPAC80 is configured through its IEEE Standard 1149.1

compliant serial port. The flexible In-System Programming

capability enables programming, verification and reconfig-

uration, if desired, directly on the printed circuit board.

Copyright © 2000 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.

Tel. (503) 268-8000; 1-888-477-7537; FAX (503) 268-8037; http://www.latticesemi.com

March 2000

pac80_03

1

1 page

Specifications ispPAC80

Timing Specifications (JTAG Interface Mode)

TA = 25°C; VS = +5.0V (Unless otherwise specified)

Symbol

Parameter

Condition

Min. Typ. Max. Units

Dynamic Performance

tckmin Minimum Clock Period

200 ns

tckh TCK High Time

50 ns

tckl TCK Low Time

50 ns

tmss TMS Setup Time

15 ns

tmsh TMS Hold Time

10 ns

tdis TDI Setup Time

15 ns

tdih TDI Hold Time

10 ns

tdozx TDO Float to Valid Delay

60 ns

tdov TDO Valid Delay

60 ns

tdoxz TDO Valid to Float Delay

60 ns

tpwp Time for a programming operation

Executed in Run-Test/Idle

80

100 ms

tpwe Time for an erase operation

Executed in Run-Test/Idle

80

100 ms

tpwcal1 Time for auto-cal operation on power-up Automatically executed at power-up

250 ms

tcalmin Minimum auto-cal pulse width

40 ns

tpwcal2 Time for user initiated auto-cal operation Executed on rising edge of CAL

100 ms

tckh tckl

tckmin

tpwp, tpwe

TCK

tmss tmsh

TMS

tdis tdih

TDI

TDO

tdozx

tdov

tdoxz

TCK

tmss

tmss

TMS

*(PRGUSR/UBE executed in

Run-Test/Idle state)

CAL

VOUT

(Note: CAL internally

initiated at device turn-on.)

tcalmin

VOUT = 0VDIFF

tpwcal1, tpwcal2

*Note: During device JTAG programming, analog output response will deviate from expected behavior. This is because all

configuration information is erased and then re-written as part of a normal programming cycle, momentarily changing device filter

and gain parameters. Behavior will deviate from that expected during both of these steps since the analog outputs are not clamped

during a programming cycle. During erase, a drop in the filter corner frequency and an automatic change to the 10X gain setting

can be expected (80ms minimum by specification) and will continue until bits go to there final state after a JTAG write command

is issued (less than 2ms later, though the write cycle must still be maintained for a full 80ms to achieve specified data retention).

5

5 Page

Specifications ispPAC80

Theory of Operation (Continued)

Differential I/O. Differential peak-peak voltage is deter-

mined by knowing the signal extremes on both differential

input or output pins. For example, if V(+) equals 4V and

V(-) equals 1V, the differential voltage is defined as V(+)

- V(-) = Vdiff, or 4V - 1V = +3V. Since either polarity can

exist on differential I/O pins, it is also possible for the

opposite extreme to exist and would mean when V(+)

equals 1V and V(-) equals 4V, the differential voltage is

now 1V - 4V = -3V. To calculate the differential peak-peak

voltage or full signal swing, the absolute difference be-

tween the two extreme Vdiff’s is calculated. Using the

previous examples would result in |(+3V) - (-3V)| = 6V. It

can be immediately seen that true differential signals

result in a doubling of usable dynamic range. For more

explanation of this and other differential circuit benefits,

please refer to application note AN6019.

Single-ended Input. To connect the ispPAC80 differen-

tial input to a single-ended signal, one of the differential

inputs needs to be connected to a DC bias, preferably

VREFOUT. The input signal must either be AC coupled or

have a DC bias equal to the DC level of the other input.

Since the input voltage is defined as VIN+- VIN-, the

common mode level is ignored. The signal information is

only present on one input, the other being connected to

a voltage reference.

Single-ended Output. Connecting the output to a single-

ended circuit is simpler still. Simply connect one-half of

the differential output, but not the other. Either output

conveys the signal information, just at half the magnitude

of the differential output. The DC level of the single-

ended output will be VREFOUT. If the load is not AC

coupled and is at a DC potential other than VREFOUT, the

load draws a constant current. Using one of the differen-

tial outputs halves the available output voltage swing

(3Vp-p versus 6Vp-p). If the load requires DC current, the

amount available for voltage swing is reduced. The

output is capable of 10mA, so any DC current raises the

minimum allowable load impedance.

Input Common-Mode Voltage Range

For the ispPAC80, both maximum input signal range and

corresponding common-mode voltage range are a func-

tion of the input gain setting. The maximum input voltage

times the gain of an individual PACblock cannot exceed

the output range of that block or clipping will occur. The

maximum guaranteed input range is 1V to 4V, with an

extended typical range of 0.7V to 4.3V for a 5V supply

voltage.

The input common-mode voltage is VCM = (VCM+ + VCM-)/2.

When the value of VCM is 2.5V, there are no further input

restrictions other than the previously mentioned clipping

consideration. This is easily achieved when the input

signal is true differential and referenced to 2.5V.

When VCM is not 2.5V and the gain setting is greater than

one, distortion will occur when the maximum input limit is

reached for a particular gain. The lowest VCM for a given

gain setting is expressed by the formula, VCM– = 0.675V

+ 0.584G·VIN where G is the gain setting and VIN is the

peak input voltage, expressed as |VIN+ - VIN–| and the

highest VCM is VCM+ = 5.0V - VCM– where 5V is the

nominal supply voltage.

In Table 4, the maximum VIN for a given VCM– to VCM+

range is given. If the maximum VIN is known, find the

equivalent or greater value under the appropriate gain

column and the widest range for VCM will be found

horizontally across in the left-most two columns. Only a

VCM range equal to or less than this will give distortion-

free performance. Conversely, if the maximum VCM

range is known, the largest acceptable peak value of VIN

can be found in the corresponding gain column. All

values of VIN less than this will give full rated perfor-

mance.

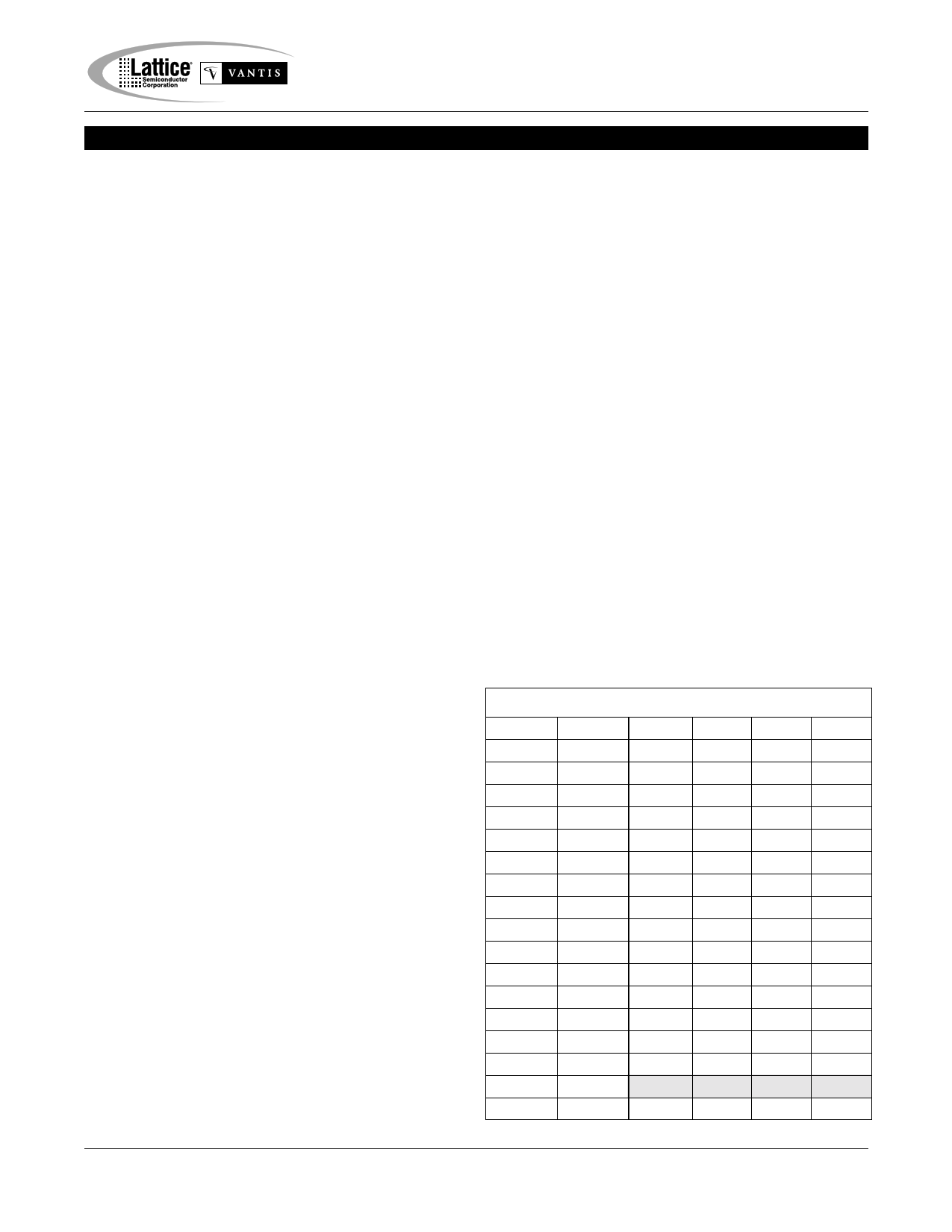

Table 4. Input Common-Mode Voltage Range

Limitations

Input Voltage Magnitude (Volts-Peak)

VCM-

1.000

VCM+

4.000

G=1 G=2 G=5 G=10

0.557 0.278 0.111 0.056

1.100

3.900 0.728 0.364 0.146 0.073

1.200

3.800 0.899 0.450 0.180 0.090

1.300

3.700 1.071 0.535 0.214 0.107

1.400

3.600 1.242 0.621 0.248 0.124

1.500

3.500 1.413 0.707 0.283 0.141

1.600

3.400 1.584 0.792 0.317 0.158

1.700

3.300 1.756 0.878 0.351 0.176

1.800

3.200 1.927 0.964 0.385 0.193

1.900

3.100 2.098 1.049 0.420 0.210

2.000

3.000 2.270 1.135 0.454 0.227

2.100

2.900 2.441 1.220 0.488 0.244

2.200

2.800 2.612 1.306 0.522 0.261

2.300

2.700 2.783 1.392 0.557 0.278

2.400

2.600 2.955 1.477 0.591 0.295

2.426

2.574 3.000* 1.500* 0.600* 0.300*

2.500

2.500 3.126 1.563 0.625 0.313

*Peak input voltage for guaranteed performance at a given gain setting.

11

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet PAC80.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PAC80 | In-System Programmable Analog Circuit | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |