|

|

PDF TDA8315 Data sheet ( Hoja de datos )

| Número de pieza | TDA8315 | |

| Descripción | Integrated NTSC decoder and sync processor | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TDA8315 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

TDA8315T

Integrated NTSC decoder

and sync processor

Preliminary specification

File under Integrated Circuits, IC02

September 1994

Philips Semiconductors

1 page

Philips Semiconductors

Integrated NTSC decoder

and sync processor

Preliminary specification

TDA8315T

FUNCTIONAL DESCRIPTION

CVBS or Y/C input

The TDA8315T has a video input which can be switched

to CVBS (with internal chrominance bandpass and trap

filters) and to Y/C (without chrominance bandpass and

trap filters). The switching between CVBS and Y/C is

achieved by the DC level of the CHROMA input (pin 15).

Integrated video filters

The circuit contains a chrominance bandpass and trap

circuit. The filters are realised by gyrator circuits that are

automatically tuned by comparing the tuning frequency

with the crystal frequency of the decoder. The

chrominance trap can be switched off by the DC level of

the CHROMA input.

The luminance delay line is also realised by gyrator

circuits.

Colour decoder

The colour decoder contains an alignment-free crystal

oscillator, a colour killer circuit and colour difference

demodulators. The gain of the two colour difference signal

demodulators is identical and the phase angle of the

reference carrier signals is 90°. This phase shift is

achieved internally. It is possible to switch the demodulator

angle to 110° by an internal matrix circuit. The switching is

obtained externally via pin 8.

Synchronization circuit

The sync separator is preceded by a voltage controlled

amplifier which adjusts the sync pulse amplitude to a fixed

level. The sync pulses are then fed to the slicing stage

(separator) which operates at 50% of the amplitude.

The separated sync pulses are fed to the first phase

detector and to the coincidence detector. The coincidence

detector is used to detect whether the line oscillator is

synchronized. The PLL has a very high static steepness,

this ensures that the phase of the picture is independent of

the line frequency. The line oscillator operates at twice the

line frequency.

The oscillator network is internal. Because of the spread of

internal components an automatic adjustment circuit has

been added to the IC.

The circuit compares the oscillator frequency with that of

the crystal oscillator in the colour decoder. This results in

a free-running frequency which deviates less than 2% from

the typical value.

The horizontal output pulse is derived from the horizontal

oscillator via a pulse shaper. The pulse width of the output

pulse is 5.4 µs, the front edge of this pulse coincides with

the front edge of the sync pulse at the input.

The vertical output pulse is generated by a count-down

circuit. The pulse width is approximately 380 µs. Both the

horizontal and vertical pulses will always be available at

the outputs even when no input signal is available.

September 1994

5

5 Page

Philips Semiconductors

Integrated NTSC decoder

and sync processor

Preliminary specification

TDA8315T

13. The horizontal output pulses are obtained from the horizontal oscillator by a pulse shaper. The width of the output

pulse is approximately 5.4 µs and the rising edge of the pulse symmetrically coincides with the start of the sync pulse

at the input.

14. The vertical output pulses are generated by a divider circuit. The vertical output pulse has a delay of 37.5 µs with

respect to the start of the vertical sync pulse at the input. This is caused by the clock frequency of the divider being

twice the horizontal frequency.

This divider circuit has 2 modes of operation:

Search mode (large window).

This mode is switched on when the circuit is not synchronized or, when a non-standard signal is received (the number

of lines per frame outside the range is between 261 and 264). In the search mode the divider can be triggered

between line 244 and line 288 (approximately 54 to 64.5 Hz).

Standard mode (narrow window).

This mode is switched on when more than 15 successive vertical sync pulses are detected in the narrow window.

When the circuit is in the standard mode and a vertical sync pulse is missing the output pulse is generated at the end

of the window. Consequently, the disturbance of the picture is very small. The circuit will switch back to the search

window when, for 6 successive vertical periods, no sync pulses are found within the window. When no input signal

is available the divider generates output pulses with a timing of 262.5 lines (standard 60 Hz signal).

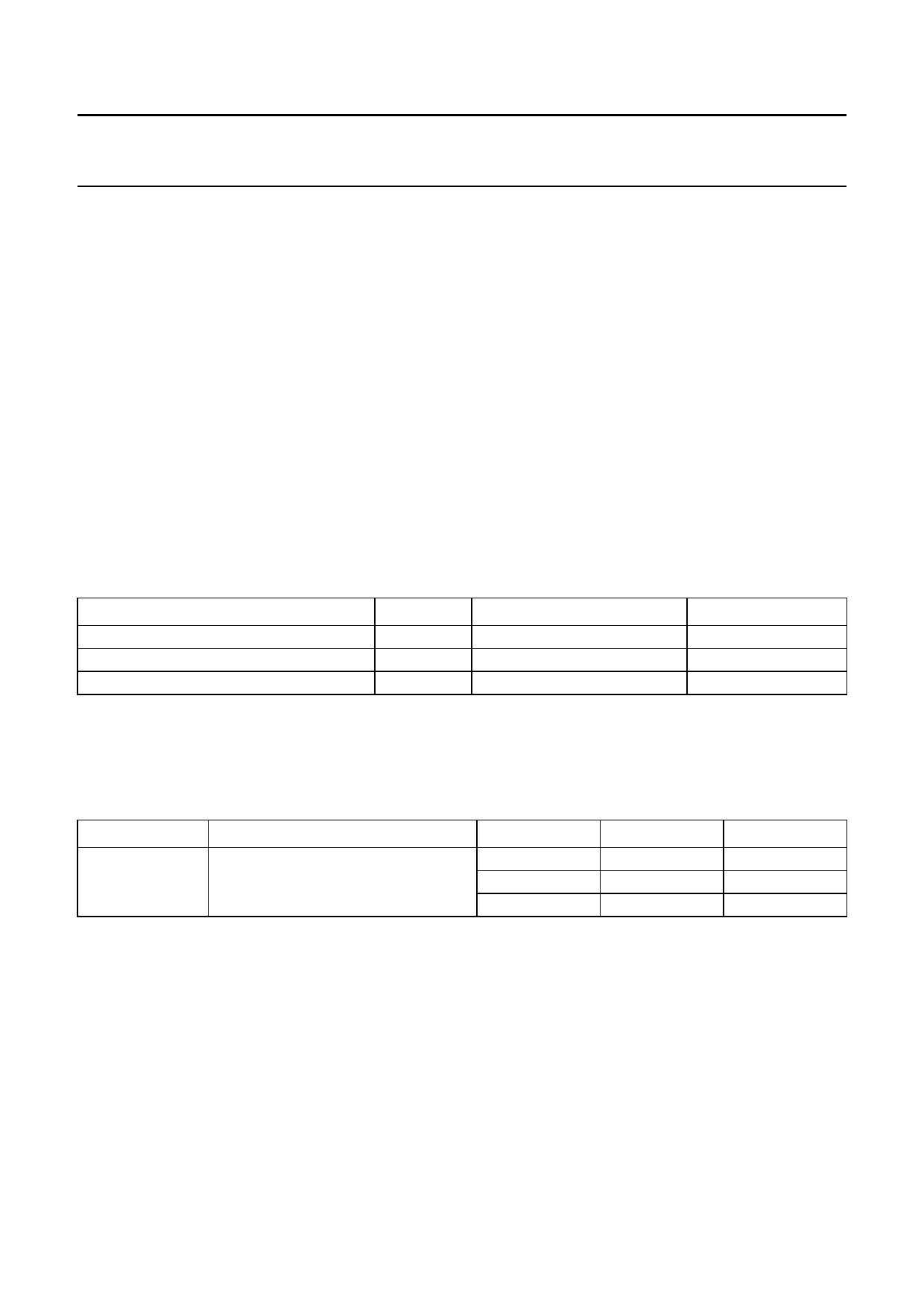

Table 1 Output current of phase detector.

CURRENT PHASE DETECTOR DURING

Weak signal and synchronized

Strong signal and synchronized

Not synchronized

Note

1. Vertical retrace.

SCAN (µA)

30

180

180

VERTICAL RETRACE (µA)

30

270

270

GATED YES/NO

YES (5.7 µs)

YES (12 µs)(1)

NO

QUALITY SPECIFICATION

Quality level in accordance with SNW-FQ-611-part E.

SYMBOL

ESD

PARAMETER

protection circuit specification (note 1)

RANGE A(2)

>2 000

100

1 500

Notes

1. All pins are protected against ESD by means of internal clamping diodes.

2. Range A is for Human body model.

3. Range B is for machine model.

Latch up

All pins meet the specification:

Itrigger ≥ 100 mA or ≥ 1.5 VDDmax

Itrigger ≤ −100 mA or ≤ −0.5 VDDmax.

RANGE B(3)

>200

200

0

UNIT

V

pF

Ω

September 1994

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet TDA8315.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA8310 | PAL/NTSC colour processor for PIP applications | NXP Semiconductors |

| TDA8310A | PAL/NTSC colour processor for PIP applications | NXP Semiconductors |

| TDA8315 | Integrated NTSC decoder and sync processor | NXP Semiconductors |

| TDA8315T | Integrated NTSC decoder and sync processor | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |