|

|

PDF UPD784044 Data sheet ( Hoja de datos )

| Número de pieza | UPD784044 | |

| Descripción | 16-BIT SINGLE-CHIP MICROCONTROLLER | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD784044 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD784044(A), 784046(A)

16-BIT SINGLE-CHIP MICROCONTROLLER

DESCRIPTION

The µPD784046(A) is a model in the µPD784046 subseries within the 78K/IV series. A stricter quality assurance

program applies µPD784046(A) compared to the µPD784046 (standard model). (In terms of NEC’s quality grading,

this is a ”special” grade product.)

The µPD784046(A) is provided with many peripheral hardware functions such as ROM, RAM, I/O port, 10-bit

resolution A/D converter, timer, serial interface, and interrupt functions, in addition to a high-speed, high-performance

CPU.

The µPD784046(A) is under development.

Moreover, a flash memory model, µPD78F4046Note, that can operate on the same supply voltage as the mask ROM

model, and many development tools are under development.

Note Use for functional evaluation only.

The functions are described in detail in the following User’s Manuals. Be sure to read these manuals when

designing your system.

µPD784046 Subseries User’s Manual - Hardware : U11515E

78K/IV Series User’s Manual - Instruction

: U10905E

FEATURES

• Higher reliability compared to the µPD784044 and 784046

• Minimum instruction execution time : 160 ns (with 12.5-MHz internal clock) ··· µPD784044(A), 784046(A)

200 ns (with 10-MHz internal clock) ··· µPD784044(A1), (A2),

784046(A1), (A2)

• I/O port

: 65 lines

• Timer

: 16-bit timer/counter × 2 units

16-bit timer × 3 units

• A/D converter

: 10-bit resolution × 16 channels

• Serial interface

UART/IOE (3-wire serial I/O) : 2 channels

• Watchdog timer

: 1 channel

• Standby function

HALT/STOP/IDLE mode

• Supply voltage

: VDD = 4.5 to 5.5 V

APPLICATION FIELDS

Automotive appliances, etc.

In this document, in addition to the µPD784044(A) and µPD784046(A), the µPD784044(A1), 784044(A2)

784046(A1), and 784046(A2) are also explained. However, unless otherwise specified, the µPD784046(A) is

treated as the representative model throughout this document.

The information in this document is subject to change without notice.

Document No. U13121EJ1V0DS00 (1st edition)

Date Published January 1998 N CP(K)

Printed in Japan

©

1998

1 page

µPD784044(A), 784046(A)

CONTENTS

1. DIFFERENCES BETWEEN µPD784044(A) AND 784046(A) ............................................................ 7

2. PIN CONFIGURATION (Top View) ..................................................................................................... 8

3. SYSTEM CONFIGURATION EXAMPLE ...........................................................................................10

4. BLOCK DIAGRAM ............................................................................................................................. 11

5. PIN FUNCTIONS ................................................................................................................................12

5.1 Port Pins .................................................................................................................................................... 12

5.2 Pins Other Than Port Pins ...................................................................................................................... 14

5.3 I/O Circuits of Pins and Processing of Unused Pins .......................................................................... 16

6. CPU ARCHITECTURE .......................................................................................................................18

6.1 Memory Space .......................................................................................................................................... 18

6.2 CPU Registers ........................................................................................................................................... 21

6.2.1 General-purpose registers ............................................................................................................. 21

6.2.2 Control registers ............................................................................................................................. 22

6.2.3 Special function registers (SFRs) .................................................................................................. 23

7. PERIPHERAL HARDWARE FUNCTIONS ........................................................................................29

7.1 Ports ........................................................................................................................................................... 29

7.2 Clock Generation Circuit ......................................................................................................................... 30

7.3 Real-Time Output Port ............................................................................................................................. 32

7.4 Timer/Counter ........................................................................................................................................... 32

7.5 A/D Converter ........................................................................................................................................... 35

7.6 Serial Interface .......................................................................................................................................... 36

7.6.1 Asynchronous serial interface/3-wire serial I/O (UART/IOE) ....................................................... 37

7.7 Edge Detection Circuit ............................................................................................................................ 39

7.8 Watchdog Timer ........................................................................................................................................ 39

8. INTERRUPT FUNCTION....................................................................................................................40

8.1 Interrupt Source ....................................................................................................................................... 40

8.2 Vectored Interrupt .................................................................................................................................... 42

8.3 Context Switching .................................................................................................................................... 43

8.4 Macro Service ........................................................................................................................................... 44

9. LOCAL BUS INTERFACE .................................................................................................................47

9.1 Memory Expansion .................................................................................................................................. 48

9.2 Memory Space .......................................................................................................................................... 49

9.3 Programmable Wait .................................................................................................................................. 49

9.4 Bus Sizing Function ................................................................................................................................. 49

5

5 Page

µPD784044(A), 784046(A)

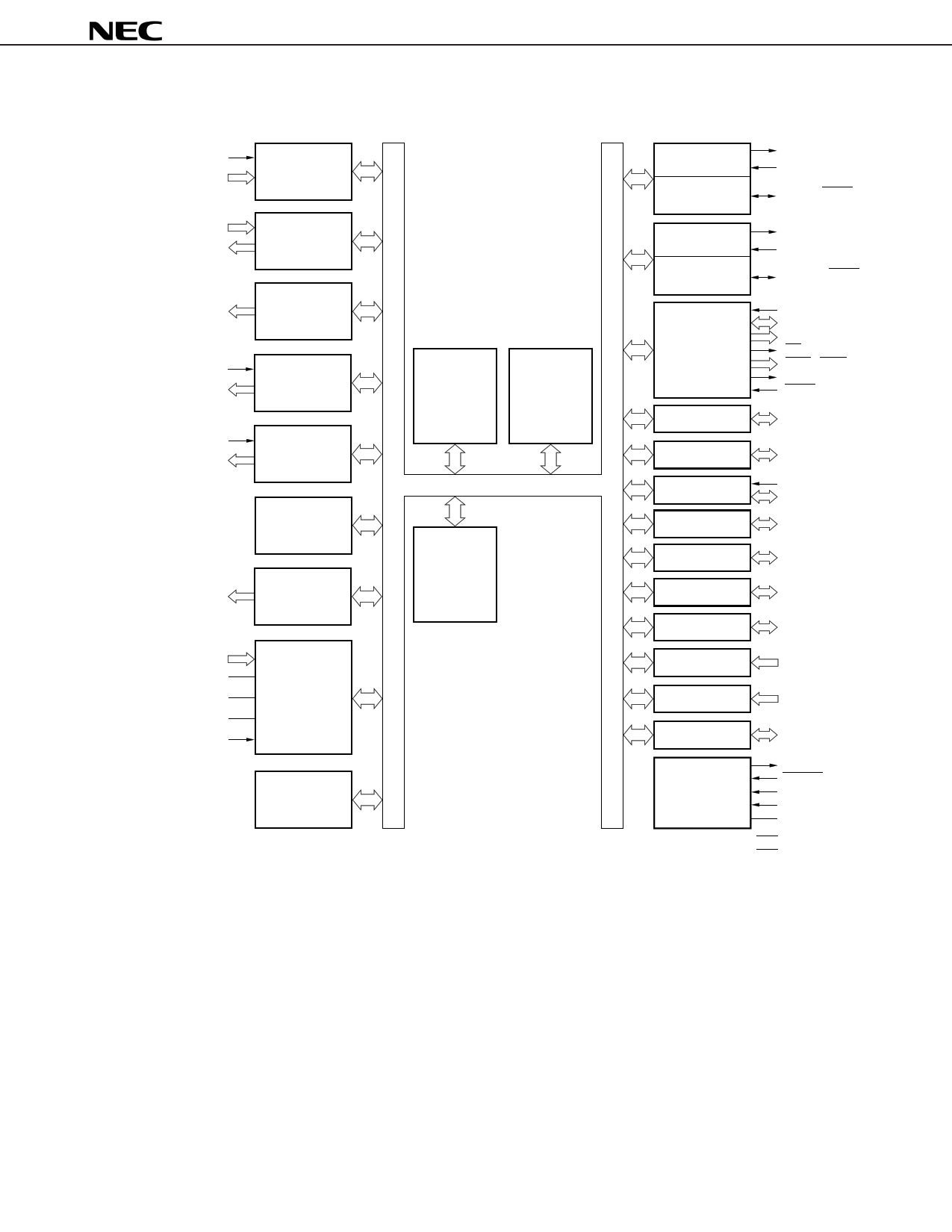

4. BLOCK DIAGRAM

NMI

INTP0-INTP6

INTP0-INTP3

TO00-TO03

Programmable

interrupt

controller

Timer 0

(16 bits)

TO10, TO11

Timer 1

(16 bits)

INTP5/TI2

TO20, TO21

Timer/counter2

(16 BITS)

INTP6/TI3

TO30, TO31

Timer/counter3

(16 BITS)

Timer 4

(16 bits)

RTP0-RTP3

ANI0-ANI15

AVDD

AVSS

AVREF

INTP4

Real-time

output port

A/D

converter

Watchdog

timer

78K/IV

CPU core

ROM

RAM

UART/IOE1

Baud-rate

generator

UART/IOE2

Baud-rate

generator

BUS I/F

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Port 7

Port 8

Port 9

System

control

Remark The internal ROM and RAM capacity differs depending on the products.

RxD/SI1

TxD/SO1

ASCK/SCK1

RxD2/SI2

TxD2/SO2

ASCK2/SCK2

BWD

AD0-AD15

A16-A19

RD

LWR, HWR

ASTB

WAIT

P00-P03

P10-P12

P20

P21-P27

P30-P37

P40-P47

P50-P57

P60-P63

P70-P77

P80-P87

P90-P94

CLKOUT

RESET

MODE

X1

X2

VDD

VSS

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet UPD784044.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD784044 | 16-BIT SINGLE-CHIP MICROCONTROLLER | NEC |

| UPD784044A | 16-BIT SINGLE-CHIP MICROCONTROLLER | NEC |

| UPD784044GC | 16-BIT SINGLE-CHIP MICROCONTROLLER | NEC |

| UPD784044GCA | 16-BIT SINGLE-CHIP MICROCONTROLLER | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |