|

|

PDF UPD77017GC Data sheet ( Hoja de datos )

| Número de pieza | UPD77017GC | |

| Descripción | 16 bits/ Fixed-point Digital Signal Processor | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD77017GC (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD77015,77017,77018

16 bits, Fixed-point Digital Signal Processor

µPD77015, 77017, 77018 are 16 bits fixed-point DSPs (Digital Signal Processors) developed for digital signal

processing with its demand for high speed and precision.

FEATURES

• FUNCTIONS

• Instruction cycle: 30 ns (MIN.)

Operation clock: 33 MHz

External clock: 33, 16.5, 8.25, 4.125 MHz

Crystal: 33 MHz

• On-chip PLL to provide higher operation clock than the external clock

• Dual load/store

• Hardware loop function

• Conditional execution

• Executes product-sum operation in one instruction cycle

• PROGRAMMING

• 16 bits × 16 bits + 40 bits → 40 bits multiply accumulator

• 8 general registers (40 bits each)

• 8 ROM/RAM data pointer: each data memory area has 4 registers

• 10 source interrupts (external: 4, internal: 6)

• 3 operand instructions (example: R0 = R0 +R1L∗R2L)

• Nonpipeline on execution stage

• MEMORY AREAS

• Instruction memory area : 64K words × 32 bits

• Data memory areas : 64K words × 16 bits × 2 (X memory, Y memory)

• CLOCK GENERATOR

• Mask option for CLKOUT pin:

Fixed to the low level.

Does not output the internal system clock.

• Selectable source clock: external clock input and crystal resonator

[External clock]

On-chip PLL to provide higher operation clock (33 MHz MAX.) than the external clock.

Variable multiple rates (1, 2, 4, 8) by mask option.

[Crystal resonator]

Oscillation frequency corresponds directly to the system clock frequency (Sure to specify the mask option

frequency multiple as "1").

In this document, all descriptions of the µPD77017 also apply to the µPD77015 and µPD77018, unless

otherwise specified.

The information in this document is subject to change without notice.

Document No. U10902EJ3V0DS00 (3rd edition)

Date Published June 1997 N

Printed in Japan

The mark shows major revised points.

©

1993, 1994

1 page

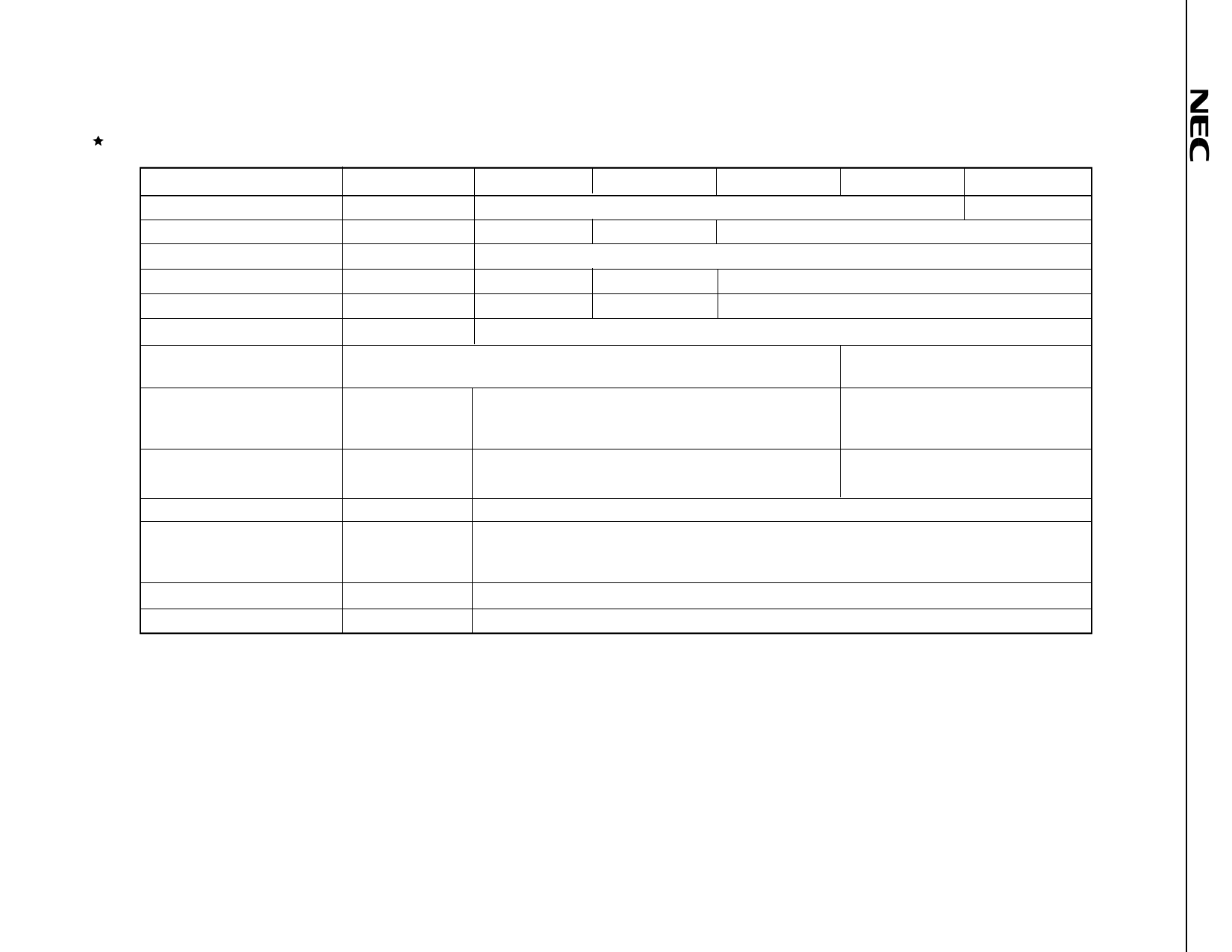

Functional Differences among the µPD7701× Family

Item

Internal instruction RAM

Internal instruction ROM

External instruction memory

Data RAM (X/Y memory)

Data ROM (X/Y memory)

External data memory

Instruction cycle

(Maximum operation speed)

External clock

(at maximum operation speed)

µPD77016

1.5K words

None

48K words

2K words each

None

48K words each

66 MHz

µPD77015

4K words

1K words each

2K words each

µPD77017

µPD77018

256 words

12K words

None

2K words each

4K words each

16K words each

µPD77018A

24K words

3K words each

12K words each

µPD77019

4K words

30 ns (33 MHz)

19 ns (52 MHz)

33/16.5/8.25/4.125 MHz

Variable multiple rate (1, 2, 4, 8 ) by mask option.

52/ 26/ 17.333/ 13/6.5 MHz

Variable multiple rate (1, 2, 3, 4, 8 ) by

mask option.

Crystal

(at maximum operation speed)

–

Instruction

–

Serial interface (2 Channels)

Channel 1 has the

same functions

as channel 2.

Power supply

5V

Package

160-pin plastic QFP

33 MHz

52 MHz

STOP instruction is added.

Channel 1 has the same functions as that of the µPD77016.

Channel 2 has no SORQ2 or SIAK2 pin (Channel 2 is used for CODEC connection).

3V

100-pin plastic TQFP

5 Page

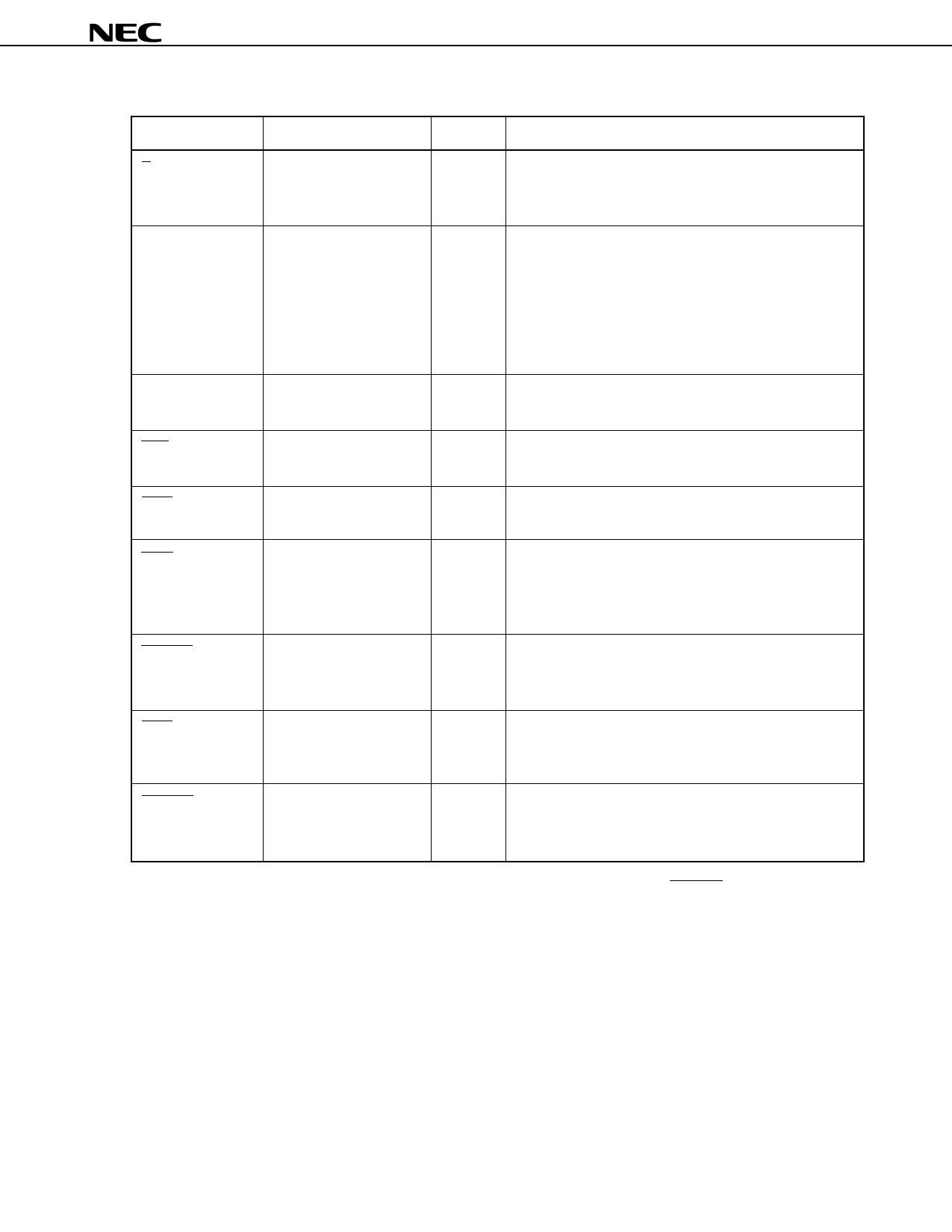

µPD77015, 77017, 77018

• External data memory interface

Symbol

Pin No.

X/Y 7

DA13 - DA0

8, 9, 12 -19, 22 - 25

D15 - D0

MRD

MWR

WAIT

26 -29, 32 - 35, 38 - 41,

44 - 47

98

95

100

HOLDRQ

BSTB

HOLDAK

93

99

94

I/O Function

O Memory select signal output

(3S) • 0: X memory is used.

• 1: Y memory is used.

O Address bus to external data memory

(3S) • External data memory is accessed.

• During the external memory is not accessed, these pins

keep the previous level.

These pins are set to low level; 0000H, by reset.

They continue outputting low level until the first external

memory access.

I/O 16 bits data bus to external data memory

(3S) • External data memory is accessed.

O Read output

(3S) • Reads external memory

O Write output

(3S) • Writes external memory

I Wait signal input

• Wait cycle is input when external memory is read.

1: No wait

0: Wait

I Hold request signal input

• Input low level when external data memory bus is

expected to use.

O Bus strobe signal output

• Outputs low level while the µPD77017 is occupying

external memory bus.

O Hold acknowledge signal output

• Outputs low level when the µPD77017 permits external

device to use external data memory bus.

Remark The state of the pins added 3S becomes high impedance when bus release signal (HOLDAK = 0) is output.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UPD77017GC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD77017GC | 16 bits/ Fixed-point Digital Signal Processor | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |