|

|

PDF UPD72873 Data sheet ( Hoja de datos )

| Número de pieza | UPD72873 | |

| Descripción | MOS INTEGRATED CIRCUIT | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD72873 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PRELIMINARY DATA SHEET

MOS INTEGRATED CIRCUIT

µPD72873

IEEE1394 OHCI 1.1 COMPLIANT 2PORT PHY-LINK 1-CHIP HOST CONTROLLER

The µPD72873 is the LSI that integrated OHCI-Link and PHY function into a single chip. The µPD72873 complies

with the 1394 OHCI Specification 1.1 and the IEEE Std 1394a-2000 specifications, and works up to 400 Mbps.

It makes design so compact for PC and PC card application.

FEATURES

• Compliant with Link Layer Services as defined in 1394 Open Host Controller Interface specification release 1.1

• Compliant with Physical Layer Services as defined in IEEE Std 1394a-2000

• Provides two cable ports at 100/200/400 Mbps

• Super Low power consumption for Physical Layer

• Compliant with protocol enhancement as defined in IEEE Std1394a-2000

• Modular 32-bit host interface compliant to PCI Specification release 2.2

• Supports PCI-Bus Power Management Interface Specification release 1.1

• Modular 32-bit host interface compliant to Card Bus Specification

• Cycle Master and Isochronous Resource Manager capable

• Built-in FIFOs for isochronous transmit (2048 bytes), asynchronous transmit (2048 bytes), and receive (3072

bytes)

• Supports D0, D1, D2, D3hot

• Supports wake up function from D3cold

• 32-bit CRC generation and checking for receive/transmit packets

• 4 isochronous transmit DMAs and 4 isochronous receive DMAs supported

• 32-bit DMA channels for physical memory read/write

• Clock generation by 24.576 MHz X’tal

• 2-wire Serial EEPROM TM interface supported

• Separate power supply Link and PHY

• Programmable latency timer from serial EEPROM in Cardbus mode (CARD_ON = 1)

ORDERING INFORMATION

Part number

µPD72873GC-YEB

Package

120-pin plastic TQFP (Fine pitch) (14 x 14)

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. S15305EJ2V0DS00 (2nd edition)

Date Published April 2002 NS CP (K)

Printed in Japan

The mark shows major revised points.

2001

1 page

PIN NAME

µPD72873

AD0 to AD31 : PCI Multiplexed Address and Data

CARD_ON : PCI/Card Select

CBE0 to : Command/Byte Enables

CBE3

CLKRUN : PCICLK Running

CPS

: Cable Power Status Input

D3CSUP : D3cold Support

DEVSEL : Device Select

FRAME : Cycle Frame

GND

: GND

GNT

: Bus_master Grant

GROM_EN : Serial EEPROM Enable

GROM_SCL : Serial EEPROM Clock Output

GROM_SDA : Serial EEPROM Data Input / Output

IC(H)

: Internally Connected (High Clamped)

IC(L)

: Internally Connected (Low Clamped)

IC(N)

: Internally Connected (Open)

IDSEL

: ID Select

INTA

: Interrupt

IRDY

: Initiator Ready

L_VDD

: VDD for Link Digital Core and Link I/Os

PAR

: Parity

PC0 to PC2 : Power Class Input

PCI_VDD : VDD for PCI I/Os

PCLK

: PCI Clock

PERR

PME

PRST

P_AVDD

P_DVDD

P_RESET

REQ

RI0

RI1

RSMRST

SERR

STOP

TpA0n

TpA0p

TpA1n

TpA1p

TpB0n

TpB0p

TpB1n

TpB1p

TpBias0

TpBias1

TRDY

XI

XO

: Parity Error

: PME Output

: Reset

: PHY Analog VDD

: PHY Digital VDD

: PHY Power on Reset Input

: Bus_master Request

: Resistor0 for Reference Current Setting

: Resistor1 for Reference Current Setting

: Resume Reset

: System Error

: PCI Stop

: Port-1 Twisted Pair A Negative Input/Output

: Port-1 Twisted Pair A Positive Input/Output

: Port-2 Twisted Pair A Negative Input/Output

: Port-2 Twisted Pair A Positive Input/Output

: Port-1 Twisted Pair B Negative Input/Output

: Port-1 Twisted Pair B Positive Input/Output

: Port-2 Twisted Pair B Negative Input/Output

: Port-2 Twisted Pair B Positive Input/Output

: Port-1 Twisted Pair Bias Voltage Output

: Port-2 Twisted Pair Bias Voltage Output

: Target Ready

: X’tal XI

: X’tal XO

Preliminary Data Sheet S15305EJ2V0DS

5

5 Page

µPD72873

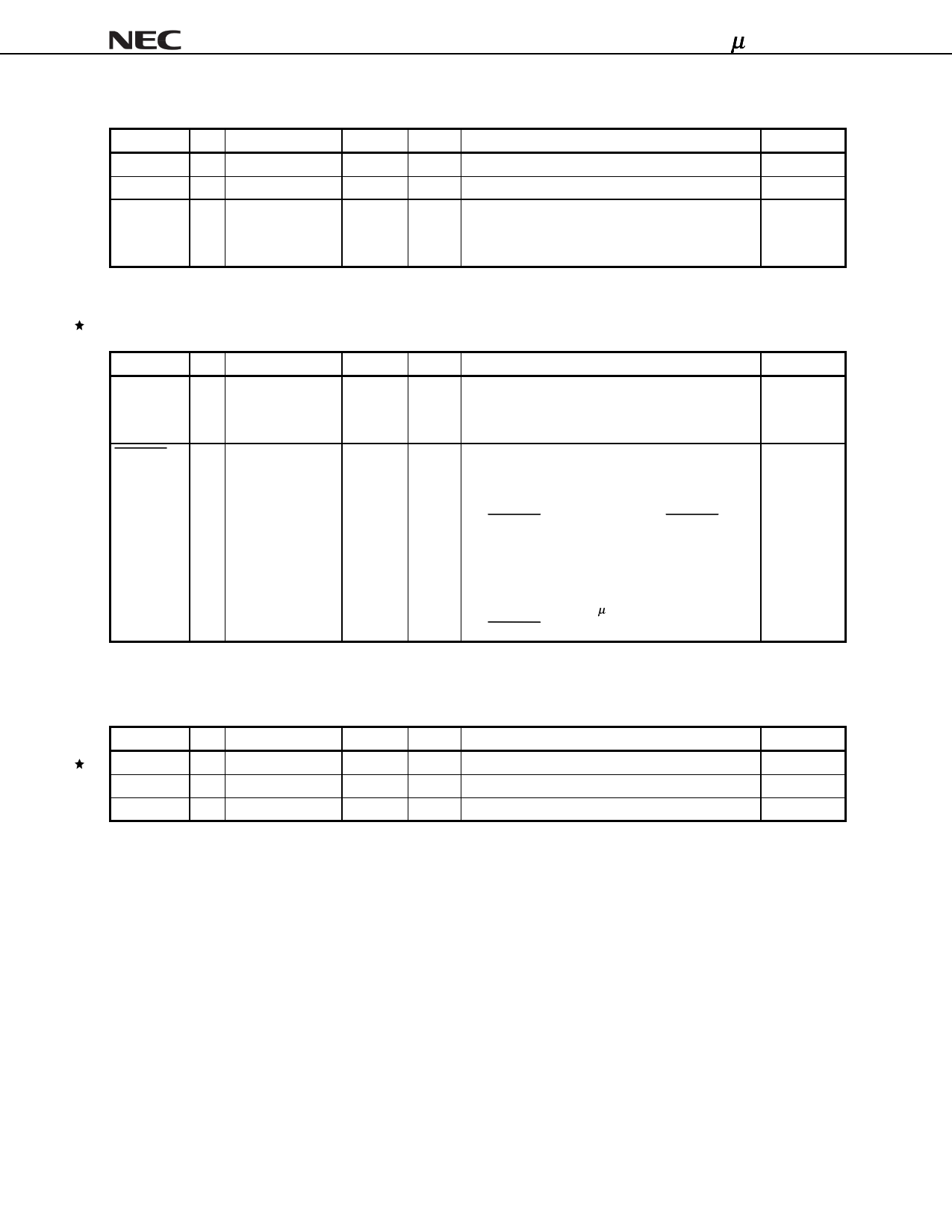

1.5 Serial ROM Interface Signals: (3 pins)

Name

I/O

Pin No.

IOL Volts(V)

Function

GROM_SDA I/O 116

6 mA

3.3 Serial EEPROM Data Input / Output

GROM_SCL O 117

6 mA

3.3 Serial EEPROM Clock Output

GROM_EN I 118

- 3.3 Serial EEPROM Enable

1: GUID Load enable

0: GUID Load disable

Remark *: If the Link pin is pulled up, it should be connected to L_VDD.

1.6 D3cold Wake Up Function Signals: (2 pins)

Name

D3CSUP

I/O Pin No.

I 114

RSMRST

I 74

IOL Volts(V)

Function

- 5/3.3 D3cold Support

1: D3cold wake up enable

0: D3cold wake up disable

- 5/3.3 Resume Reset

D3cold support (114 pin) = ‘1’

As this mode supports D3cold wake up,

RSMRST must connect system RSMRST

signal.

D3cold support (114 pin) = ‘0’

As this mode is the µPD72872 compatible,

RSMRST clamp to ‘1’.

Remark *: If the Link pin is pulled up, it should be connected to L_VDD.

1.7 IC: (7 pins)

Name

I/O

Pin No.

IOL Volts(V)

Function

IC(H)

I 75

- - Internally Connected (High clamped)

IC(L)

I 76 to 78, 80, 115

-

- Internally Connected (Low clamped)

IC(N)

- 85

- - Internally Connected (Open)

Remark *: If the Link pin is pulled up, it should be connected to L_VDD.

Block *

Link

Link

Link

Block *

Link

Link

Block *

Link

-

-

Preliminary Data Sheet S15305EJ2V0DS

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UPD72873.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD72870 | IEEE1394 1-CHIP OHCI HOST CONTROLLER | NEC |

| UPD72870A | IEEE1394 1-CHIP OHCI HOST CONTROLLER | NEC |

| UPD72870AF1-FA2 | IEEE1394 1-CHIP OHCI HOST CONTROLLER | NEC |

| UPD72870AGM-8ED | IEEE1394 1-CHIP OHCI HOST CONTROLLER | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |