|

|

PDF UPD720100A Data sheet ( Hoja de datos )

| Número de pieza | UPD720100A | |

| Descripción | MOS INTEGRATED CIRCUIT | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD720100A (archivo pdf) en la parte inferior de esta página. Total 32 Páginas | ||

|

No Preview Available !

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD720100A

USB2.0 HOST CONTROLLER

The µPD720100A complies with the Universal Serial Bus Specification Revision 2.0 and Open Host Controller

Interface Specification for full-/low-speed signaling and Intel's Enhanced Host Controller Interface Specification for

high-speed signaling and works up to 480 Mbps. The µPD720100A is integrated three host controller cores with PCI

interface and USB2.0 transceivers into a single chip.

Detailed function descriptions are provided in the following user’s manual. Be sure to read the manual before designing.

µPD720100A User’s Manual: S15534E

FEATURES

• Compliant with Universal Serial Bus Specification Revision 2.0 (Data Rate 1.5/12/480 Mbps)

• Compliant with Open Host Controller Interface Specification for USB Rev 1.0a

• Compliant with Enhanced Host Controller Interface Specification for USB Rev 0.95

• PCI multi-function device consists of two OHCI host controller cores for full-/low-speed signaling and one EHCI

host controller core for high-speed signaling.

• Root hub with five (max.) downstream facing ports which are shared by OHCI and EHCI host controller core

• All downstream facing ports can handle high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps)

transaction.

• Configurable number of downstream facing ports (2 to 5)

• 32-bit 33 MHz host interface compliant to PCI Specification release 2.2.

• Supports PCI Mobile Design Guide Revision 1.1.

• Supports PCI-Bus Power Management Interface Specification release 1.1.

• PCI Bus bus-master access

• System clock is generated by 30 MHz X’tal or 48 MHz clock input.

• Operational registers direct-mapped to PCI memory space

• Legacy support for all downstream facing ports. Legacy support features allow easy migration for motherboard

implementation.

• 3.3 V power supply, PCI signal pins have 5 V tolerant circuit.

ORDERING INFORMATION

Part Number

µPD720100AGM-8ED

µPD720100AGM-8EY

µPD720100AS1-2C

Package

160-pin plastic LQFP (Fine pitch) (24 × 24)

160-pin plastic LQFP (Fine pitch) (24 × 24)

176-pin plastic FBGA (15 × 15)

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. S15535EJ2V0DS00 (2nd edition)

Date Published October 2002 NS CP (K)

Printed in Japan

The mark shows major revised points.

©

2001

1 page

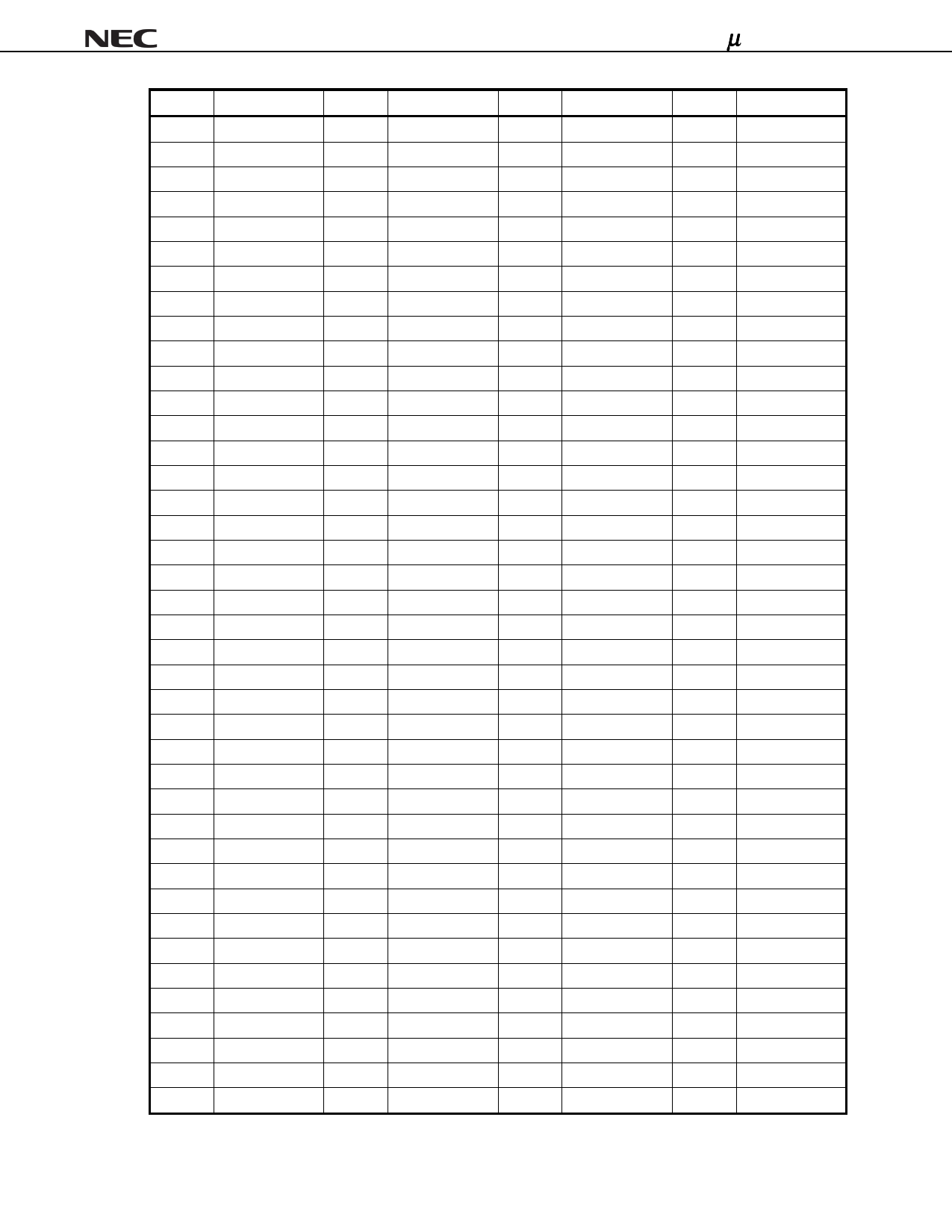

µPD720100A

Pin No.

Pin Name

Pin No.

Pin Name

Pin No.

Pin Name

Pin No.

Pin Name

1 VDD

41 VSS

81 VDD

121 VSS

2 NTEST1

42 VSS

82 AD5

122 VSS

3 NTEST2

43 AD23

83 AD4

123 RSDM1

4 TEST

44 SMC

84 AD3

124 DM1

5 XT1/SCLK 45 SIN/TIN

85 AD2

125 VDD

6 XT2

46

SOT/TOUT

86

AD1

126 DP1

7 LEGC

47 AD22

87 AD0

127 RSDP1

8 VDD

48 AD21

88 CRUN0

128 VSS

9 VSS

49 AD20

89 VDD_PCI

129 RSDM2

10 VCCRST0 50 AD19

90 SRDTA

130 DM2

11 SMI0

51 VDD

91 SRCLK

131 VDD

12 IRI1

52 AD18

92 SRMOD

132 DP2

13 IRI2

53 AD17

93 OCI1

133 RSDP2

14 IRO1

54 AD16

94 PPON1

134 VSS

15 IRO2

55 CBE20

95 OCI5

135 VDD

16 A20S

56 FRAME0

96 OCI2

136 AVSS

17 PME0

57 IRDY0

97 OCI4

137 AVDD

18 PCLK

58 TRDY0

98 AMC

138 PC2

19 VBBRST0

59 DEVSEL0

99 OCI3

139 AVSS

20 VDD

60 VDD_PCI

100 VDD

140 PC1

21 VSS

61 STOP0

101 VSS

141 N.C.

22 VDD_PCI

62 PERR0

102 PPON2

142 AVDD

23 INTA0

63 SERR0

103 PPON3

143 AVSS (R)

24 INTB0

64 PAR

104 SCK/TCLK

144 RREF

25 INTC0

65 CBE10

105 PPON4

145 AVSS

26 PIN_EN

66 VSS

106 TEB

146 VDD

27 GNT0

67 AD15

107 PPON5

147 VSS

28 REQ0

68 AD14

108 VSS

148 RSDM3

29 AD31

69 AD13

109 CLKSEL

149 DM3

30 AD30

70 VDD

110 VSS

150 VDD

31 VSS

71 AD12

111 RSDM5

151 DP3

32 AD29

72 AD11

112 DM5

152 RSDP3

33 AD28

73 AD10

113 VDD

153 VSS

34 AD27

74 AD9

114 DP5

154 RSDM4

35 AD26

75 AD8

115 RSDP5

155 DM4

36 AD25

76 CBE00

116 VSS

156 VDD

37 AD24

77 AD7

117 SELDAT

157 DP4

38 CBE30

78 AD6

118 N.C.

158 RSDP4

39 IDSEL

79 VSS

119 SELCLK

159 VSS

40 VDD

80 VSS

120 VDD

160 VSS

Remark AVSS (R) should be used to connect RREF through 1 % precision reference resistor of 9.1 kΩ.

Data Sheet S15535EJ2V0DS

5

5 Page

µPD720100A

2.2 Terminology

Terms Used in Absolute Maximum Ratings

Parameter

Symbol

Meaning

Power supply voltage

VDD Indicates voltage range within which damage or reduced reliability will not

result when power is applied to a VDD pin.

Input voltage

VI Indicates voltage range within which damage or reduced reliability will not

result when power is applied to an input pin.

Output voltage

VO Indicates voltage range within which damage or reduced reliability will not

result when power is applied to an output pin.

Operating temperature

TA Indicates the ambient temperature range for normal logic operations.

Storage temperature

Tstg Indicates the element temperature range within which damage or reduced

reliability will not result while no voltage or current are applied to the device.

Terms Used in Recommended Operating Range

Parameter

Symbol

Meaning

Power supply voltage

VDD Indicates the voltage range for normal logic operations occur when VSS = 0V.

High-level input voltage

VIH Indicates the voltage, which is applied to the input pins of the device, is the

voltage indicates that the high level states for normal operation of the input

buffer.

* If a voltage that is equal to or greater than the “MIN.” value is applied, the

input voltage is guaranteed as high level voltage.

Low-level input voltage

VIL Indicates the voltage, which is applied to the input pins of the device, is the

voltage indicates that the low level states for normal operation of the input

buffer.

* If a voltage that is equal to or lesser than the “MAX.” value is applied, the

input voltage is guaranteed as low level voltage.

Terms Used in DC Characteristics

Parameter

Symbol

Off-state output leakage current

IOZ

Output short circuit current

IOS

Input leakage current

II

Low-level output current

IOL

High-level output current

IOH

Meaning

Indicates the current that flows from the power supply pins when the rated

power supply voltage is applied when a 3-state output has high impedance.

Indicates the current that flows when the output pin is shorted (to GND pins)

when output is at high-level.

Indicates the current that flows when the input voltage is supplied to the

input pin.

Indicates the current that flows to the output pins when the rated low-level

output voltage is being applied.

Indicates the current that flows from the output pins when the rated high-

level output voltage is being applied.

Data Sheet S15535EJ2V0DS

11

11 Page | ||

| Páginas | Total 32 Páginas | |

| PDF Descargar | [ Datasheet UPD720100A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD720100A | MOS INTEGRATED CIRCUIT | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |