|

|

PDF VSP2210 Data sheet ( Hoja de datos )

| Número de pieza | VSP2210 | |

| Descripción | CCD SIGNAL PROCESSOR For Digital Cameras | |

| Fabricantes | Burr-Brown Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de VSP2210 (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

®

VSP2210

VSP2210

For most current data sheet and other product

information, visit www.burr-brown.com

CCD SIGNAL PROCESSOR

For Digital Cameras

FEATURES

q CCD SIGNAL PROCESSING:

Correlated Double Sampling (CDS)

Programmable Black Level Clamping

q PROGRAMMABLE GAIN AMPLIFIER (PGA):

–6 to +42dB Gain Ranging

q 10-BIT DIGITAL DATA OUTPUT:

Up to 20MHz Conversion Rate

No Missing Codes

q 79dB SIGNAL-TO-NOISE RATIO

q ON-CHIP GENERAL-PURPOSE 8-BIT

DIGITAL-TO-ANALOG CONVERTERS

q PORTABLE OPERATION:

Low Voltage: 2.7V to 3.6V

Low Power: 97mW (typ) at 3.0V

Stand-By Mode: 6mW

DESCRIPTION

The VSP2210 is a complete mixed-signal processing

IC for digital cameras, providing signal conditioning

and analog-to-digital conversion for the output of a

CCD array. The primary CCD channel provides Cor-

related Double Sampling (CDS) to extract video infor-

mation from the pixels, –6dB to +42dB gain ranging

with digital control for varying illumination condi-

tions, and black level clamping for an accurate black

reference. Input signal clamping and offset correction

of the input CDS is also performed. The stable gain

control is linear in dB. Additionally, the black level is

quickly recovered after gain change. The two on-chip

general-purpose 8-bit digital-to-analog converters al-

low you to obtain analog various control voltage, such

as VSUB control of CCD imager. The VSP2210Y is

available in an LQFP-48 package and operates from a

single +3V/+3.3V supply.

CLPDM SHP SHD SLOAD SCLK SDATA

RESET

DACOUT0 DACOUT1

ADCCK DRVDD

VCC

CCDIN

CCD

Output

Signal

Input

Clamp

Serial Interface

8-Bit

D/A Converter

(DAC0)

8-Bit

D/A Converter

(DAC1)

Timing

Control

Correlated

Double

Sampling

(CDS)

Programmable

Gain

Amplifier

(PGA)

–6dB

to

+42dB

Analog

to

Digital

Converter

Output

Latch

10-Bit

Digital

Output

B[9:0]

Optical Black (OB)

Preblanking Level Clamping

Reference Voltage Generator

PBLK

COB

CLPOB

BYPP2 BYP BYPM REFN

CM

REFP DRVGND GNDA

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©2000 Burr-Brown Corporation

PDS-11597A

VSPriPnte2d 2in1U.0S.A. May, 2000

®

1 page

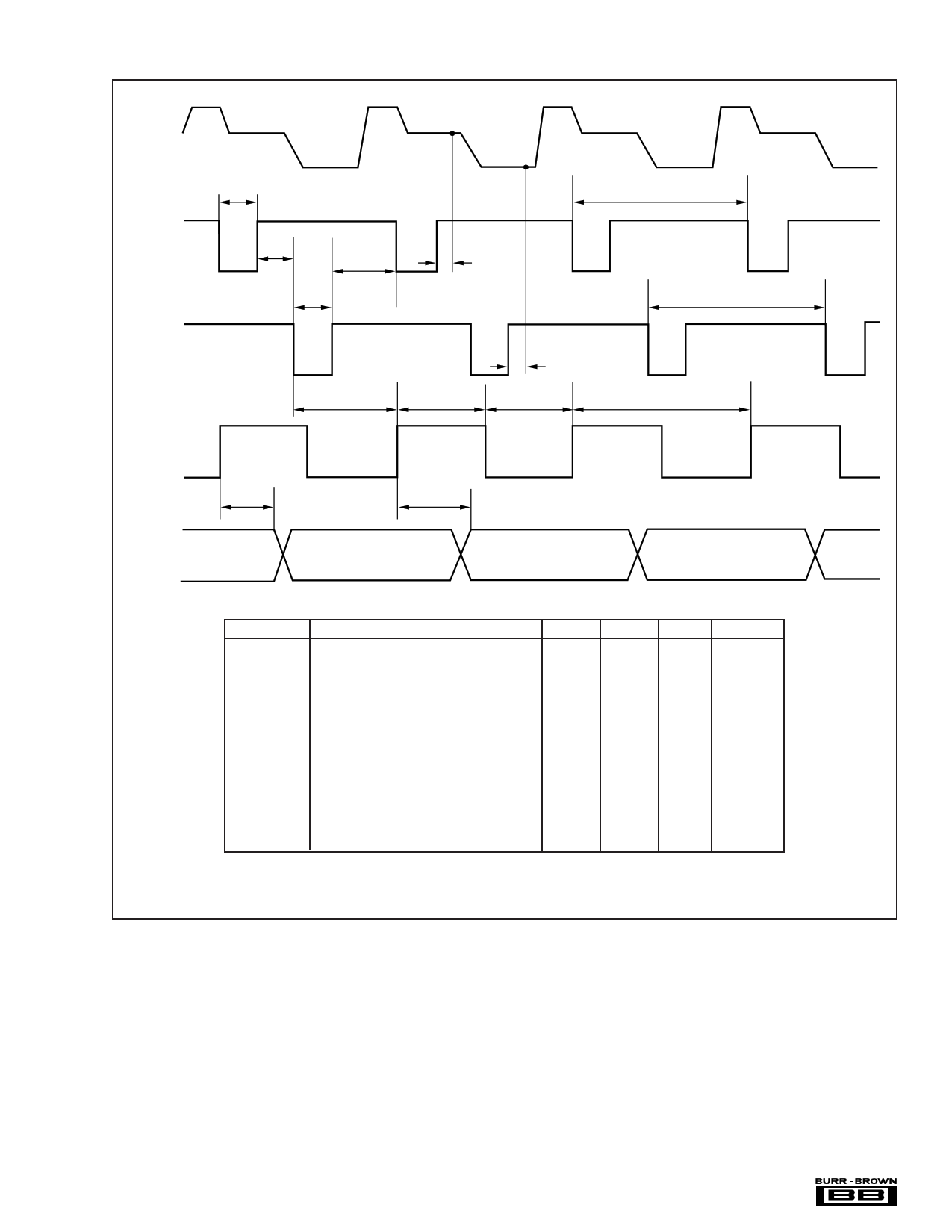

CDS TIMING SPECIFICATIONS

CCD

Output

Signal

SHP(1)

SHD(1)

ADCCK

N

tWP

tPD

tWD

tDP

tINHIBIT

N+1

tS

tADC

tS

tADC

tHOLD

tOD

B0 to B11

N – 11

N – 10

N–9

N+2

tCKP

tCKP

tCKP

N–8

N+3

N–7

SYMBOL

tCKP

tADC

tWP

tWD

tPD

tDP

tS

tINHIBIT

tHOLD

tOD

DL

PARAMETER

Clock Period

ADCCK HIGH/LOW Pulse Width

SHP Pulse Width

SHD Pulse Width

SHP Trailing Edge to SHD Leading Edge(1)

SHD Trailing Edge to SHP Leading Edge(1)

Sampling Delay

Inhibited Clock Period

Output Hold Time

Output Delay (No Load)

Data Latency, Normal Operation Mode

MIN

TYP

MAX

UNITS

48 ns

20 ns

14 ns

11 ns

8

12

5

ns

ns

ns

20 ns

7 ns

38 ns

9 (fixed)

Clock Cycles

NOTE: (1) The description and timing diagrams in this data sheet are all based on the polarity of Active LOW

(default value). The active polarity (Active LOW or Active HIGH) can be chosen through the serial interface.

Refer to the “Serial Interface” section for more detail.

®

5 VSP2210

5 Page

TIMINGS

The CDS and the ADC are operated by SHP/SHD and their

derivative timing clocks generated by the on-chip timing

generator. The digital output data is synchronized with

ADCCK. The timing relationship among the CCD signal,

SHP/SHD, ADCCK and the output data is shown in the

VSP2210 “CDS Timing Specifications”. CLPOB is used to

activate the black level clamp loop during the OB pixel

interval, and CLPDM is used to activate the input clamping

during the dummy pixel interval. If the CLPDM pulse is not

available in your system, the CLPOB pulse can be used in

place of CLPDM as long as the clamping takes place during

black pixels (refer to the “Input Clamp and Dummy Pixel

Clamp” section for more detail). The clock polarities of

SHP/SHD, CLPOB and CLPDM can be independently set

through the serial interface (refer to the “Serial Interface”

section for more detail). The description and the timing

diagrams in this data sheet are all based on the polarity of

Active LOW (default value). In order to keep a stable and

accurate OB clamp level, we recommend CLPOB should

not be activated during PBLK active period. Refer to the

“Preblanking and Data Latency” section for more detail. In

Stand-By mode, all of ADCCK, SHP, SHD, CLPOB and

CLPDM are internally masked and pulled HIGH.

GENERAL-PURPOSE 8-BIT DIGITAL-TO-ANALOG

CONVERTER (DAC0,DAC1)

The VSP2210 incorporates two identical 8-bit Digital-to-

Analog converters (DACs). These DACs are for user-defin-

able options such as iris control and sub-bias voltage control

of the CCD imager. The input data for these DACs is set by

the written data through the serial interface (refer to the

“Serial Interface” section for more detail). DAC input data

that is all ZEROs corresponds to a minimum output voltage

of 0.1V. In a similar manner, all ONEs correspond to a

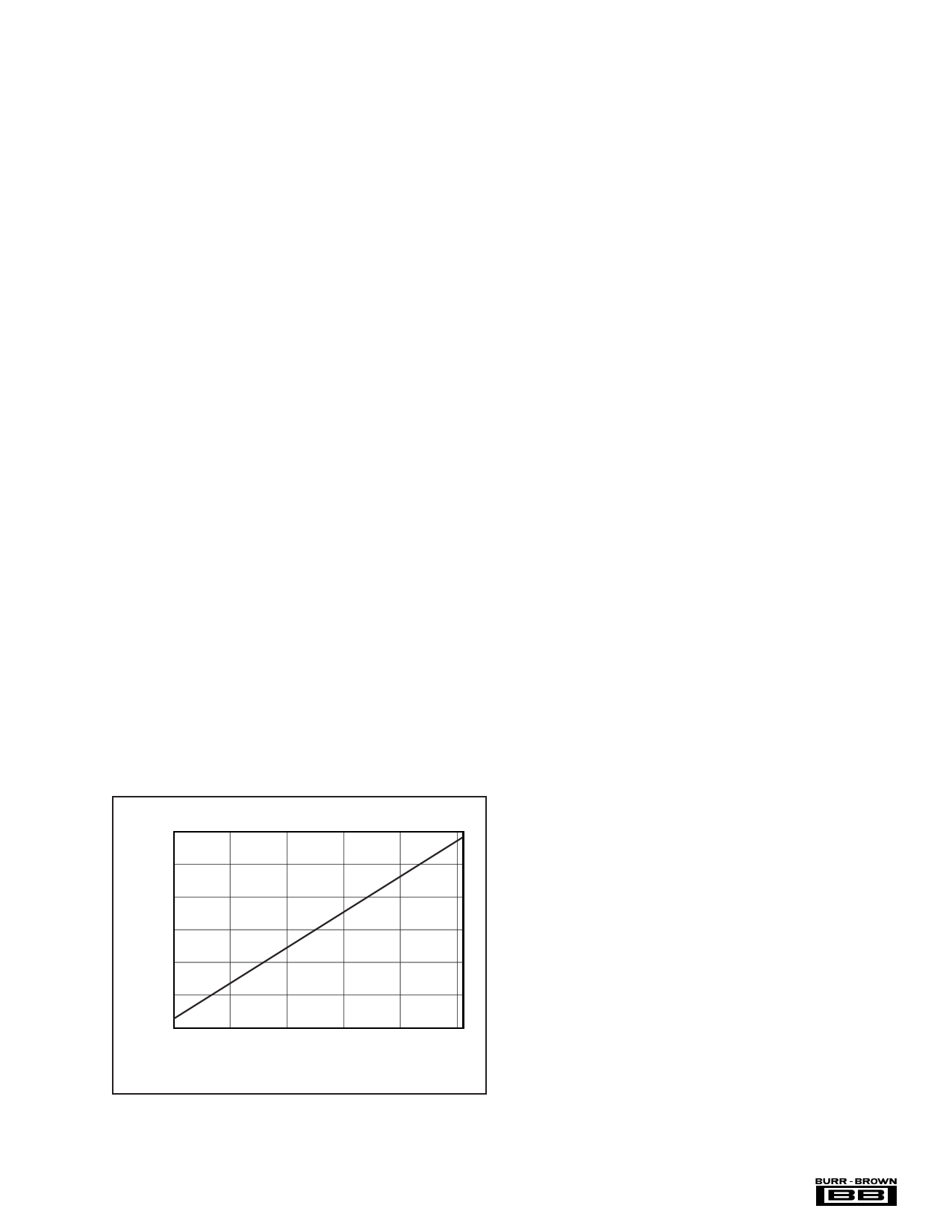

maximum output voltage of 2.9V. Figure 3 shows the

characteristics.

3.0

2.5

2.0

1.5

1.0

0.5

0

Input Control Code (0 to 255)

FIGURE 3. Characteristics for general-purpose 8-bit DAC

(DAC0, DAC1).

POWER SUPPLY, GROUNDING AND DEVICE

DECOUPLING RECOMMENDATIONS

The VSP2210 incorporates a very high-precision and high-

speed Analog-to-Digital converter and analog circuitry that

are vulnerable to any extraneous noise from the rails or

elsewhere. For this reason, it should be treated as an analog

component and all supply pins except for DRVDD should be

powered by the only analog supply of the system. This will

ensure the most consistent results, since digital power lines

often carry high level of wide band noise that would other-

wise be coupled into the device and degrade the achievable

performance. Proper grounding, short lead length and the

use of ground planes are also very important for high-

frequency designs. Multilayer PC boards are recommended

for the best performance, since they offer distinct advantages

like minimizing ground impedance, separation of signal

layers by ground layers, etc. It is highly recommended that

analog and digital ground pins of the VSP2210 be joined

together at the IC and be connected only to the analog

ground of the system. The driver stage of the digital outputs

(B[9:0]) is supplied through a dedicated supply pin (DRVDD)

and it should be separated from the other supply pins

completely, or at least with a ferrite bead. It is also recom-

mended to keep the capacitive loading on the output data

lines as low as possible (typically less than 15pF). Larger

capacitive loads demand higher charging current surges that

can feed back into the analog portion of the VSP2210 and

affect the performance. If possible, external buffers or latches

should be used, providing the added benefit of isolating the

VSP2210 from any digital noise activities on the data lines.

In addition, resistors in series with each data line may help

minimizing the surge current. Values in the range of 100Ω

to 200Ω will limit the instantaneous current the output stage

has to provide for recharging the parasitic capacitances as

the output levels change from LOW to HIGH, or HIGH to

LOW. Due to high operation speed, the converter also

generates high-frequency current transients and noises that

are fed back into the supply and reference lines. This

requires the supply and reference pins be sufficiently by-

passed. In most cases, 0.1µF ceramic chip capacitors are

adequate to decouple the reference pins. Supply pins should

be decoupled to the ground plane with a parallel combina-

tion of tantalum (1µF to 22µF) and ceramic (0.1µF) capaci-

tors. The effectiveness of the decoupling largely depends on

the proximity to the individual pin. DRVDD should be

decoupled to the proximity of DRVGND. Special attention

must be paid to the bypassing of COB, BYPP2 and BYPM,

since these capacitor values determine important analog

performances of the device.

®

11 VSP2210

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet VSP2210.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| VSP2210 | CCD SIGNAL PROCESSOR For Digital Cameras | Burr-Brown Corporation |

| VSP2210Y | CCD SIGNAL PROCESSOR For Digital Cameras | Burr-Brown Corporation |

| VSP2212 | CCD SIGNAL PROCESSOR For Digital Cameras | Burr-Brown Corporation |

| VSP2212 | VSP2212 CCD Signal Processor For Digital Cameras (Rev. A) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |