|

|

PDF VSP2101 Data sheet ( Hoja de datos )

| Número de pieza | VSP2101 | |

| Descripción | CCD SIGNAL PROCESSOR For Digital Cameras | |

| Fabricantes | Burr-Brown Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de VSP2101 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

®

VSP2101

VSP2101

TM CCD SIGNAL PROCESSOR

For Digital Cameras

FEATURES

q CCD SIGNAL PROCESSING:

Correlated Double Sampling

Black Level Clamping

–2 to +34dB Gain Ranging

High SNR: 53dB

q 10-BIT A/D CONVERSION:

Up to 27MHz Conversion Rate

No Missing Codes

q PORTABLE OPERATION:

Low Voltage: 2.7V to 3.6V

Low Power: 190mW at 3.0V

q LOW POWER: 160mW at 2.7V

q POWER-DOWN MODE: 18mW

APPLICATIONS

q VIDEO CAMERAS

q DIGITAL STILL CAMERAS

q PC CAMERAS

q SECURITY CAMERAS

REFCK DATCK WRT SD SCLK

DESCRIPTION

The VSP2101Y is a complete digital camera IC, pro-

viding signal conditioning and 10-bit analog-to-digital

conversion for the output of a CCD array.

The primary CCD channel provides correlated double

sampling to extract the video information from the

pixels, –2dB to +34dB gain ranging with digital con-

trol for varying illumination conditions, and black

level clamping for an accurate black reference.

Input signal clamping and offset correction of the CDS

is also performed. The stable gain control is linear in

dB. Additionally, the black level is quickly recovered

after gain change. An on-chip general purpose 10-bit

digital-to-analog converter allows you to obtain ana-

log control voltage for iris control.

The VSP2101Y is available in a 48-lead LQFP pack-

age and operates from a single +3V supply.

DAC OUT

C

OB

ADCK DRVDD

CCD D

CCD Out

CCD R

Serial Port

Register

10-Bit

D/A Converter

(DAC1)

Correlated

Double

Sampling

Clamp

10-Bit

D/A Converter

(DAC0)

+6dB

Log VCA

Dummy

Pixel

Auto- Zero

Black Level

Auto-Zero

A/D

Timing Control

+28dB

10-Bit

A/D

Converter

Output

Latch

10-Bit

Digital

Output

A/D

Reference

DUMC

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©1998 Burr-Brown Corporation

PDS-1506B

Printed in U.S.A. June, 1999

1 page

SERIAL CONTROL DATA FORMAT FOR DAC0/DAC1

BIT

NO. DESIGNATOR DESCRIPTION

1 A1 Start Bit. Either HIGH or LOW will be acceptable.

2 A0 Address Bit. Selects internal DACs.

LOW = DAC0, VGA control DAC

HIGH = DAC1, general purpose DAC

3 D9 Digital Input Data for DAC, Bit 10 (MSB)

4 D8 Digital Input Data for DAC, Bit 9

5 D7 Digital Input Data for DAC, Bit 8

6 D6 Digital Input Data for DAC, Bit 7

7 D5 Digital Input Data for DAC, Bit 6

8 D4 Digital Input Data for DAC, Bit 5

9 D3 Digital Input Data for DAC, Bit 4

10 D2 Digital Input Data for DAC, Bit 3

11 D1 Digital Input Data for DAC, Bit 2

12 D0 Digital Input Data for DAC, Bit 1 (LSB)

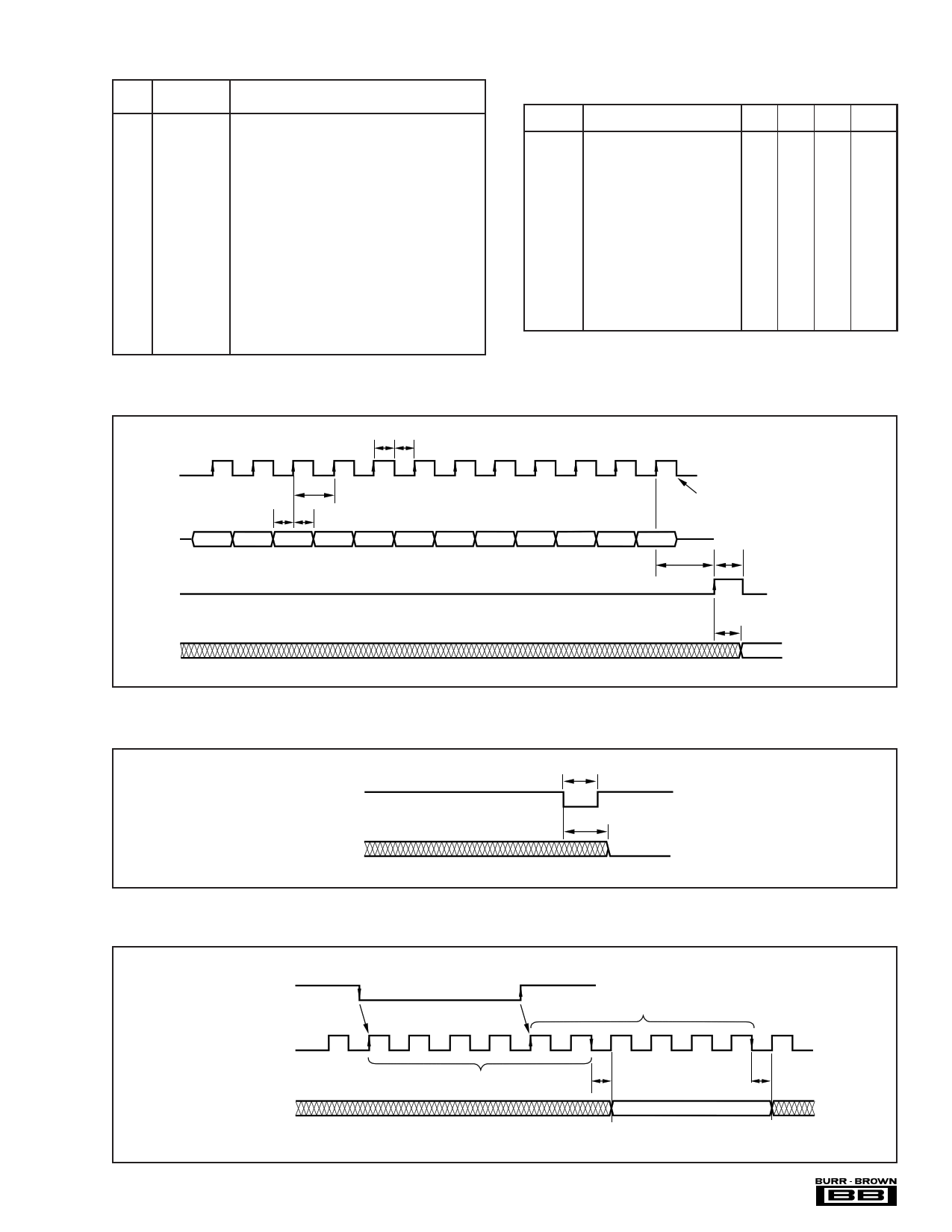

TIMING SPECIFICATIONS FOR SERIAL REGISTERS

Timing Specifications = tMIN to tMAX with +3V power supply.

SYMBOL

PARAMETER

MIN TYP MAX UNITS

tCKP

Serial Clock Period

100

tCKL Serial Clock Pulse Width LOW 50

tCKH Serial Clock Pulse Width HIGH 50

tSD

Data Setup Time

50

tHD

Data Hold Time

25

tSW

Write Pulse Setup Time

100

tW

Write Pulse Width

50

tWD

Data Valid Delay Time

50

tRS

Register Reset Pulse Width

50

tRSD

Register Reset Delay Time

50

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

TIMING FOR SERIAL PORT WRITING

SCLK

SD

WRT

DATA

tCKH

tCKL

tCKP

tSD tHD

Must be LOW before WRT goes HIGH

A1 A0 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

tSW

tW

tWD

Valid

TIMING FOR REGISTER RESET

RESET

REGISTER

DATA

TIMING FOR PREBLANKING

PB Mode

ADCK

DIGITAL OUTPUT

tRS

tRSD

All Zeros

5.5 Clocks

5

5.5 Clocks

t7

PB Mode

t7

VSP2101

®

5 Page

where C is the external filter capacitance applied to pin 24

(C), GM is .001Ω and D is the duty cycle of the time that the

black level auto-zero loop is in operation. The duty cycle (D)

must be considered as the loop operates in a sampled mode.

Operation of the black level auto-zero loop is activated by

the OB signal that happens once during each horizontal line

interval.

A/D CONVERTER

The A/D converter utilizes a pipline architecture. The fully

differential topology and digital error correction guarantee

10-bit resolution. The A/D converter circuitry includes a

reference circuit that provides bias voltages for the entire

system.

SERIAL INTERFACE AND DACs

The VSP2101 incorporates two identical 10-bit DACs (DAC0

and DAC1). DAC0 is for controlling the amount of attenu-

ation of the log Voltage Controlled Attenuator (VCA) and

DAC1 is for user-defineable options such as iris control.

The input data for these DACs are set by the written data

through the serial interface. The serial port has an 12-bit

register which is controlled by four signals (SD, SCLK,

WRT, RESET). SD is the serial data input, SCLK is the

clock for the serial data, WRT pulse takes the serial register

data into another internal parallel register at the rising edge,

RESET resets all the registers’ data to zeros asynchronously

when RESET = LOW. The serial register uses master-slave

dual flip-flops and the master flip-flop receives the input

data at the rising edge of SCLK and transmits this data into

the slave at the falling edge of SCLK. Therefore, the clock

SCLK must be normally LOW.

When the DAC input data is all zeros, this corresponds to a

maximum output voltage of 2.4V. In a similar manner, all

ones correspond to a DAC output voltage of 0.3V. The VCA

attenuation is at a minimum—which is the same as the

channel gain being a maximum—when the DAC voltage is

at 2.4V.

The serial data format and the related signal timing are

shown page 5. When the input serial data is longer than 12

bits, the last 12 bits become effective and the former bits are

erased.

When the registers are reset, the user should be careful that

the channel gain setting becomes maximum and DAC1

output voltage goes to maximum.

DECOUPLING AND GROUNDING

CONSIDERATIONS

The VSP2101 has several supply pins, one of which is

dedicated to supply only the digital output driver (pin 12,

DRVDD). The remaining supply pins are not, as is often the

case, divided into analog and digital supply pins since they

are internally connected on the chip. For this reason, it is

recommended that the VSP2101 be treated as an analog

component and be powered from the analog supply only.

Digital supply lines often carry high levels of wide band

noise which can couple back into the VSP2101 and limit

performance.

Figure 5 shows the recommended decoupling scheme for the

VSP2101. In most cases, 0.1µF ceramic chip capacitors are

adequate to keep the impedance low over a wide frequency

range. Their effectiveness largely depends on the proximity

to the individual pin. Therefore, they should be located as

close as possible to the pins. In addition, one larger capacitor

(1µF to 22µF) should be placed on the PC board in proxim-

ity of the VSP2101.

OTHER RECOMMENDATIONS

DRVDD is a power supply used exclusively for the digital

output driver and should not be connected to AVDD and

DVDD, even if the power supply voltage is the same. The

voltage level difference between DRVDD, AVDD, and DVDD

should be kept less than 0.3V.

If your PC board has analog and digital ground, AVSS, DVSS,

and DRVSS should be connected to analog ground.

DEMONSTRATION BOARD

A demonstration board, DEM-VSP2101, is available to

assist in the inital evaluation of the circuit performance

using the VSP2101. The schematic of the DEM-VSP2101 is

shown in Figure 5.

®

11 VSP2101

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet VSP2101.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| VSP2101 | CCD SIGNAL PROCESSOR For Digital Cameras | Burr-Brown Corporation |

| VSP2101 | VSP2101 CCD Signal Processor For Digital Cameras (Rev. A) | Texas Instruments |

| VSP2101Y | CCD SIGNAL PROCESSOR For Digital Cameras | Burr-Brown Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |