|

|

PDF X46402V8-3.1A Data sheet ( Hoja de datos )

| Número de pieza | X46402V8-3.1A | |

| Descripción | Dual Voltage CPU Supervisor with 64K Password Protected EEPROM | |

| Fabricantes | Xicor | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de X46402V8-3.1A (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

Preliminary Information

64K X46402

Dual Voltage CPU Supervisor with 64K Password Protected EEPROM

FEATURES

• Dual Voltage Detection and Reset Assertion

—Low Vcc Monitor

—Low V2MON Monitor

—Low Vcc Block of EEPROM Writes

—RESET Signal Valid down to Vcc=1V

• Selectable Watchdog Timer

—150ms, 450ms, 1s, 5s, 10s, 20s, 1min, OFF

• Volatile Flag shows Watchdog/Low Voltage Reset

• 64kbit 2-wire Serial EEPROM

—1MHz Serial Interface speed

—64-Byte Page Write Mode

• Two 64-Byte OTP memory blocks

—Requires 64-bit OTP password to write

• Adjustable size Password Protected Array

—64 Bit Read and Write Array Passwords

—Non-password protected array area

• 8 count tamper counter for invalid passwords

• Operates at 2.5-3.7V

• 8L TSSOP package

DESCRIPTION

The X46402 combines several functions into one device.

The first is a dual voltage CPU supervisor plus 64Kbit

serial EEPROM memory with password protected write

and read operations. The size of the password protected

area is selectable by 3 control bits. A Write Protect (WP)

pin in conjunction with a WPEN bit provides hardware

OTP control of the configuration of the array. Password

protected areas require 64 bit read or write passwords

prior to access. The eighth illegal password entry

(regardless of the number of correct entries) sets an OTP

tamper bit. This bit is one of the 32 bits in the Device ID.

A secondary voltage monitor circuit activates a V2FAIL

pin when the secondary supply voltage drops below a

V2trip voltage. This circuit is primarily intended to detect

the immediate loss of the battery supply.

A low Vcc voltage detect circuit activates a RESET pin

when Vcc drops below a VTRIP voltage. This signal also

blocks read or write operations.

A watchdog timer with the time period controlled by three

bits provides several possible time out periods from

150ms to 1 minute.

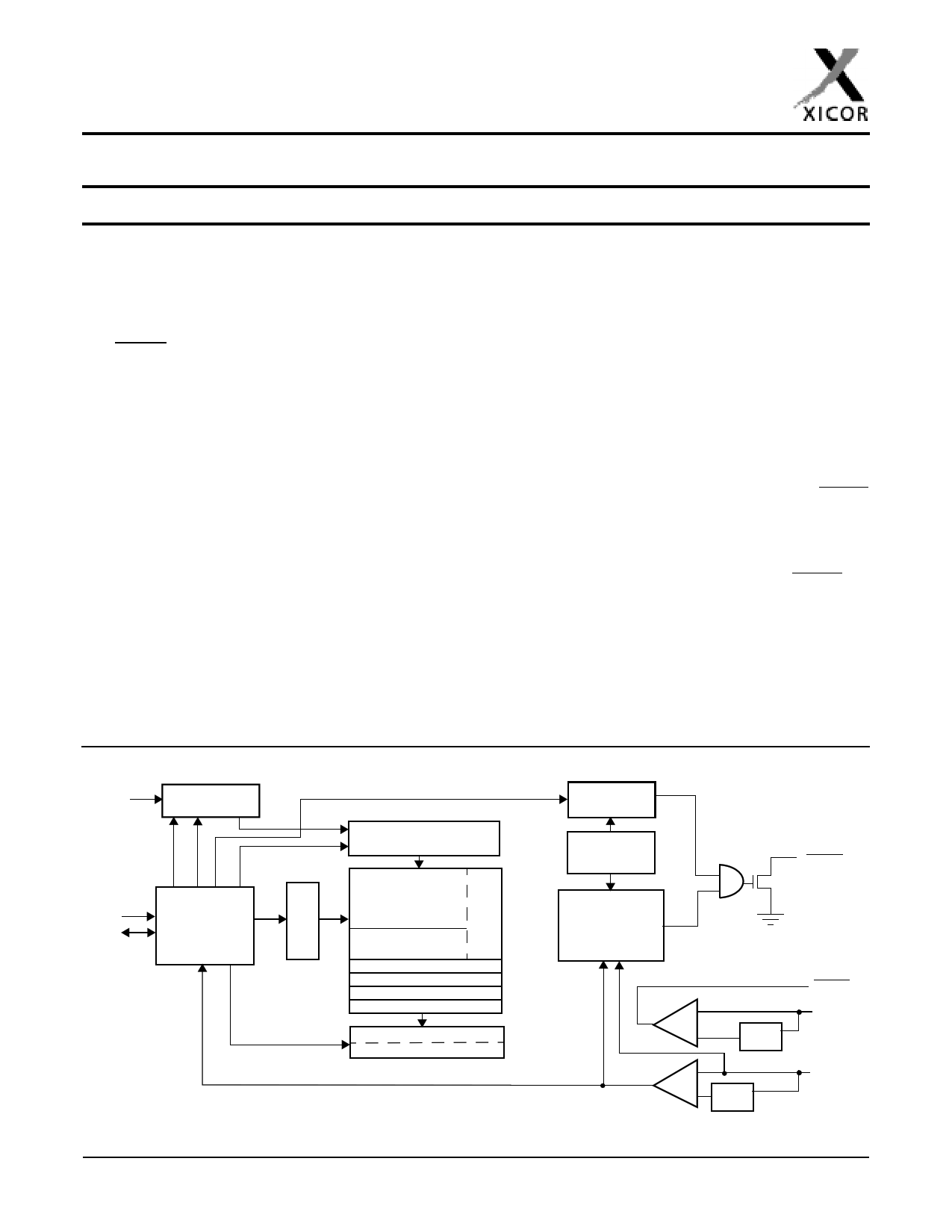

Functional Diagram

WP

Write Control

Password Logic

HV Generation

Timing and Control

SCL

SDA

Command

Decode

and

Control

Logic

Write Password Area

(Bytes)

(64, 128, 256, 512,

2K, 4K, All, None)

No Password Area

Control

OTP array 1

OTP array 2

Passwords

(Vcc) Control Signal

Y Decoder

Data Register

©Xicor, Inc. 1994, 1995, 1996, 1998 Patents Pending

9900-3003 5 1/11/00 CM

1

WATCHDOG

TIMER RESET

RESET &

WATCHDOG

TIMEBASE

POWER ON AND

LOW VOLTAGE

RESET

GENERATION

RESET

+

- V2TRIP

+

- VTRIP

V2FAIL

V2MON

Vcc

Characteristics subject to change without notice

1 page

X46402

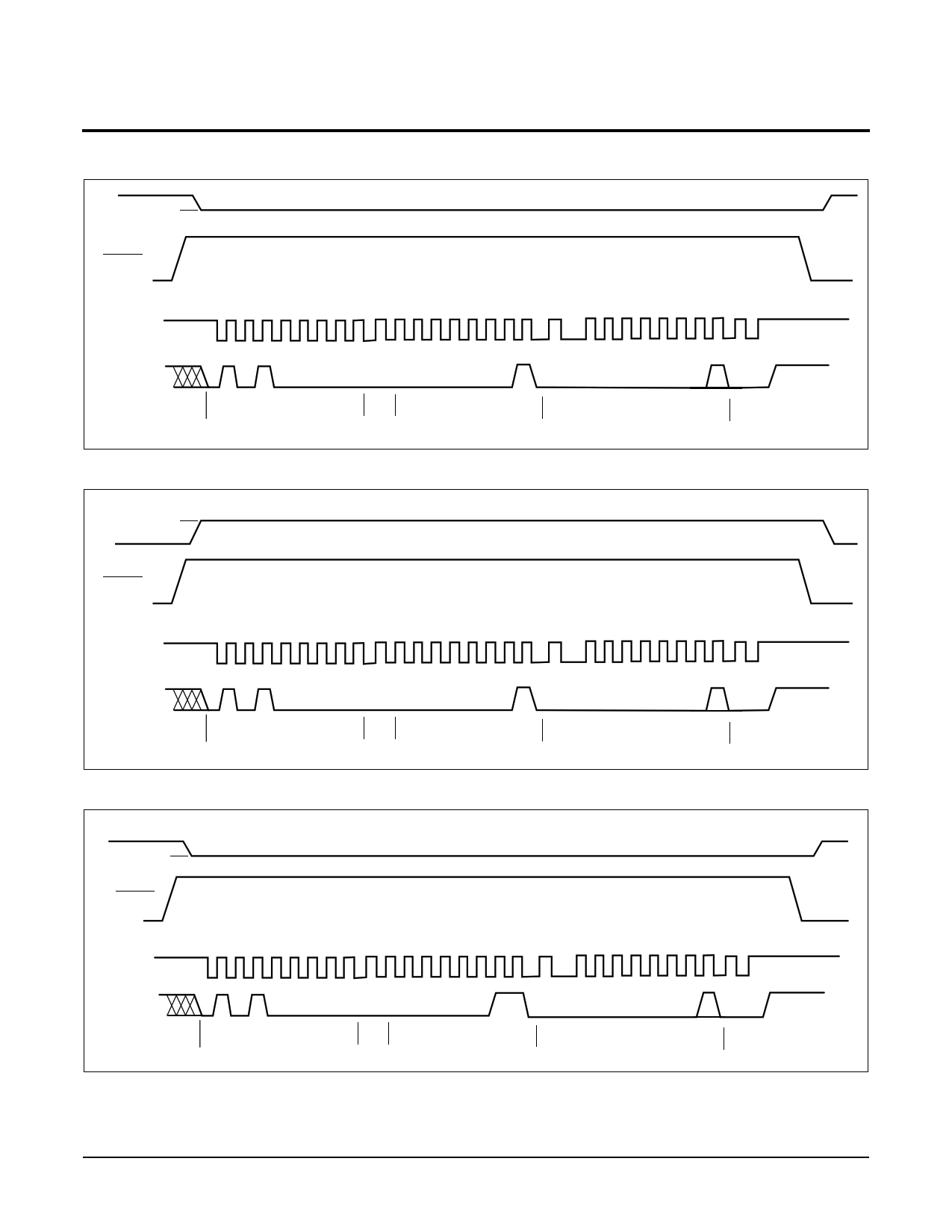

Figure 2. Set VTRIP Level Sequence (VCC ≥ VTRIP)

VCC

VTRIP

RESET

VP = 15V

0 1 2 34 5 6 7

0 1 2 34 5 6 7

SCL

SDA

D8h

00h

Figure 3. Set V2TRIP Level Sequence (VCC ≥ V2TRIP)

V2TRIP

V2MON

RESET

VP = 15V

0 1 2 34 5 6 7

0 1 2 34 5 6 7

SCL

SDA

D8h

00h

Figure 4. Reset VTRIP Level Sequence (Vcc > 3V, WEL is set.)

VCC

VTRIP

RESET

SCL

SDA

VP = 15V

0 1 2 34 5 6 7

0 1 2 34 5 6 7

D8h 00h

Preliminary Information

0 1 2 34 5 6 7

01h

01h sets Vcc

0 1 2 34 5 6 7

0Dh

0Dh sets V2MON

0 1 2 34 5 6 7

03h

03h resets Vcc

5

5 Page

X46402

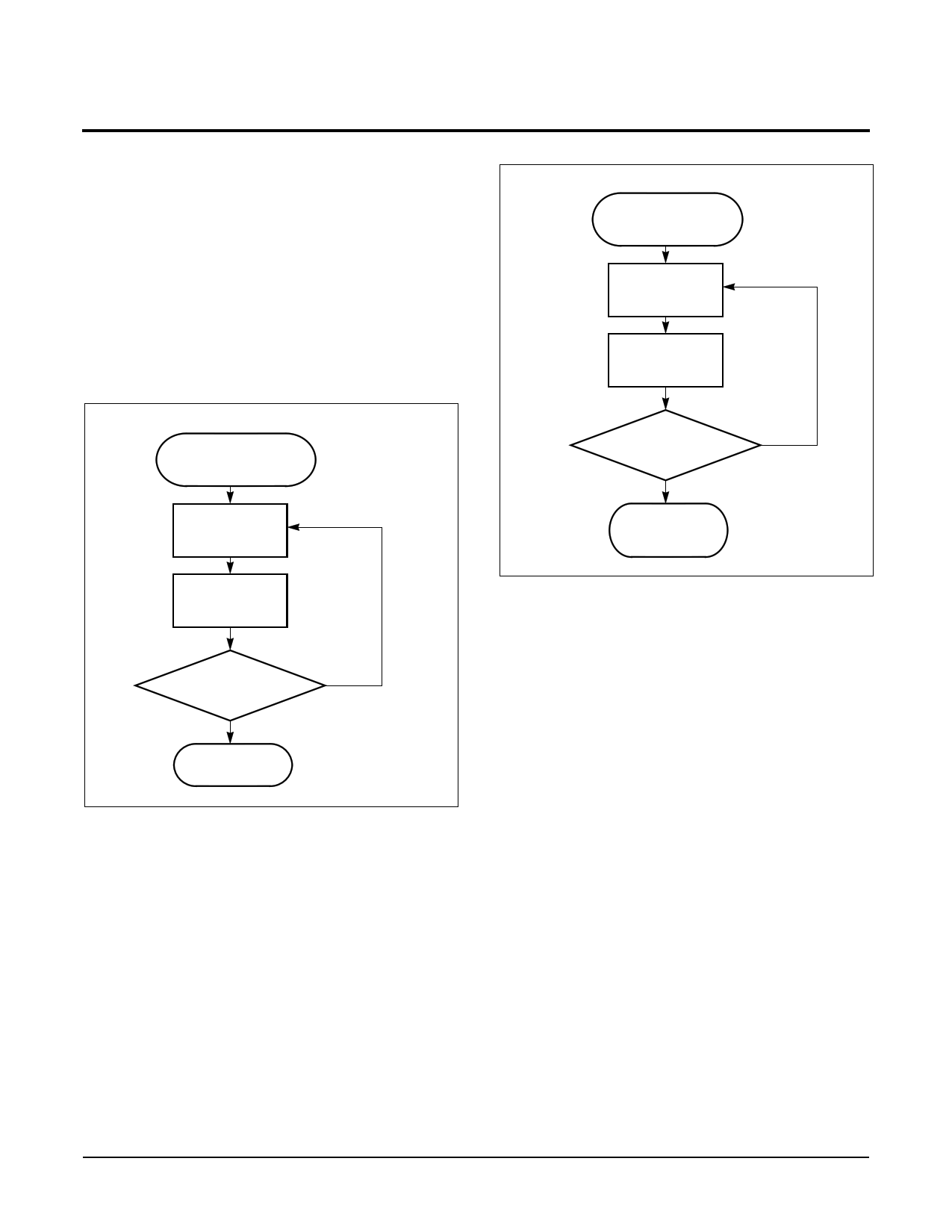

ACK Polling

Once a stop condition is issued to indicate the end of the

host’s write sequence, the X46402 initiates the internal

nonvolatile write cycle. In order to take advantage of the

typical 5ms write cycle, ACK polling can begin immedi-

ately. This involves issuing the start condition followed by

the new command code of 8 bits (1st byte of the protocol.)

If the X46402 is still busy with the nonvolatile write opera-

tion, it will issue a “no-ACK” in response. If the nonvolatile

write operation has completed, an “ACK” will be returned

and the host can then proceed with the rest of the proto-

col. See Figure 12.

Data ACK Polling Sequence

WRITE SEQUENCE

COMPLETED

ENTER ACK POLLING

ISSUE START

Preliminary Information

Password ACK Polling Sequence

PASSWORD LOAD

COMPLETED

ENTER ACK POLLING

ISSUE START

ISSUE

PASSWORD

ACK COMMAND

ACK

RETURNED?

YES

PROCEED

NO

ISSUE NEW

COMMAND

CODE

ACK

RETURNED?

YES

PROCEED

NO

If the password that was inserted was correct, then an

“ACK” will be returned once the nonvolatile cycle is over, in

response to the ACK polling cycle immediately following it.

If the password that was inserted was incorrect, then a “no

ACK” will be returned even if the nonvolatile cycle is over.

Therefore, the user cannot be certain that the password is

incorrect until the 10ms write cycle time has elapsed.

After the password sequence, there is always a nonvolatile

write cycle. This is done to discourage random guesses of

the password if the device is being tampered with. In order

to continue the transaction, the X46402 requires the mas-

ter to perform an ACK polling with the specific code of

F0h. As with regular Acknowledge polling the user can

either time out for 10ms, and then issue the ACK polling

once, or continuously loop as described in the flow.

11

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet X46402V8-3.1A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| X46402V8-3.1 | Dual Voltage CPU Supervisor with 64K Password Protected EEPROM | Xicor |

| X46402V8-3.1A | Dual Voltage CPU Supervisor with 64K Password Protected EEPROM | Xicor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |