|

|

PDF XC7336-12 Data sheet ( Hoja de datos )

| Número de pieza | XC7336-12 | |

| Descripción | 36-Macrocell CMOS EPLD | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XC7336-12 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

® XC7336

36-Macrocell CMOS EPLD

Product Specifications

Features

• Ultra high-performance EPLD

– 5 ns pin-to-pin speed on all fast inputs

– 167 MHz maximum clock frequency

• New low power XC7336Q

• 100% routable with 100% utilization

• Incorporates four PAL-like 24V9 Fast Function Blocks

• 36 Output Macrocells

– Programmable I/O architecture

– 24 mA drive

• High-performance µP compatible

• Peripheral Component Interface (PCI) compatible

• JEDEC standard 3.3 V or 5 V I/O operation

• Multiple security bits for design protection

• 44-pin leaded chip carrier and 44-pin quad flat pack

packages

General Description

The XC7336 is a member of the Xilinx XC7300 EPLD fam-

ily. It consists of four PAL-like 24V9 Fast Function Blocks

interconnected by the 100%-populated Universal Intercon-

nect Matrix (UIM™).

Each Fast Function Block has 24 inputs and contains nine

Macrocells configurable for registered or combinational

logic. The nine Macrocell outputs feed back to the UIM and

can simultaneously drive the output pads.

The UIM allows 100% connectivity between all function

blocks and input pins, providing the ability to utilize 100% of

the device while eliminating routing issues.

The XC7336 is designed in 0.8 µ CMOS EPROM technol-

ogy, in speed grades ranging from 5 to15 ns. The XC7336Q

is also available now, providing lower power consumption in

-10, -12 and -15 ns speed grades.

Device logic is automatically configured to the user’s speci-

fications using the XEPLD software. The XEPLD software

is capable of optimizing and collapsing logic. The SMART-

switch software/hardware feature allows implementation of

buried combinatorial logic functions in the UIM, thus

increasing device utilization. The XEPLD software supports

third party schematic capture and HDL entry tools, as well

as direct equation-based text files. Using a workstation or

PC platform, designs are automatically mapped into the

XC7336 in a matter of minutes.

PQ44 PC44

22 28

I/FI

1 7 I/FO/FI

2 8 I/FO

3 9 I/FO

5 11 I/FO

6 12 I/FO

7 13 I/FO

8 14 I/FO

9 15 I/FO

10 16

I/FO

21 27

I/FO

20 26

I/FO

19 25

I/FO

18 24

I/FO

16 22

I/FO

14 20 I/FO/FI

13 19 I/FO/FI

12 18 I/FO/FI

11 17

I/FO

19

FFB1

MC1-1

MC1-2

MC1-3

MC1-4

MC1-5

MC1-6

MC1-7

MC1-8

MC1-9

12

12

12

3

9

9

34

FFB4

MC4-1

MC4-2

MC4-3

MC4-4

MC4-5

MC4-6

MC4-7

MC4-8

MC4-9

12

12

12

3

9

UIM

9

12

12

12

3

9

15

FFB2

MC2-9

MC2-8

MC2-7

MC2-6

MC2-5

MC2-4

MC2-3

MC2-2

MC2-1

9

12

12

12

3

9

FFB3

MC3-9

MC3-8

MC3-7

MC3-6

MC3-5

MC3-4

MC3-3

MC3-2

MC3-1

9

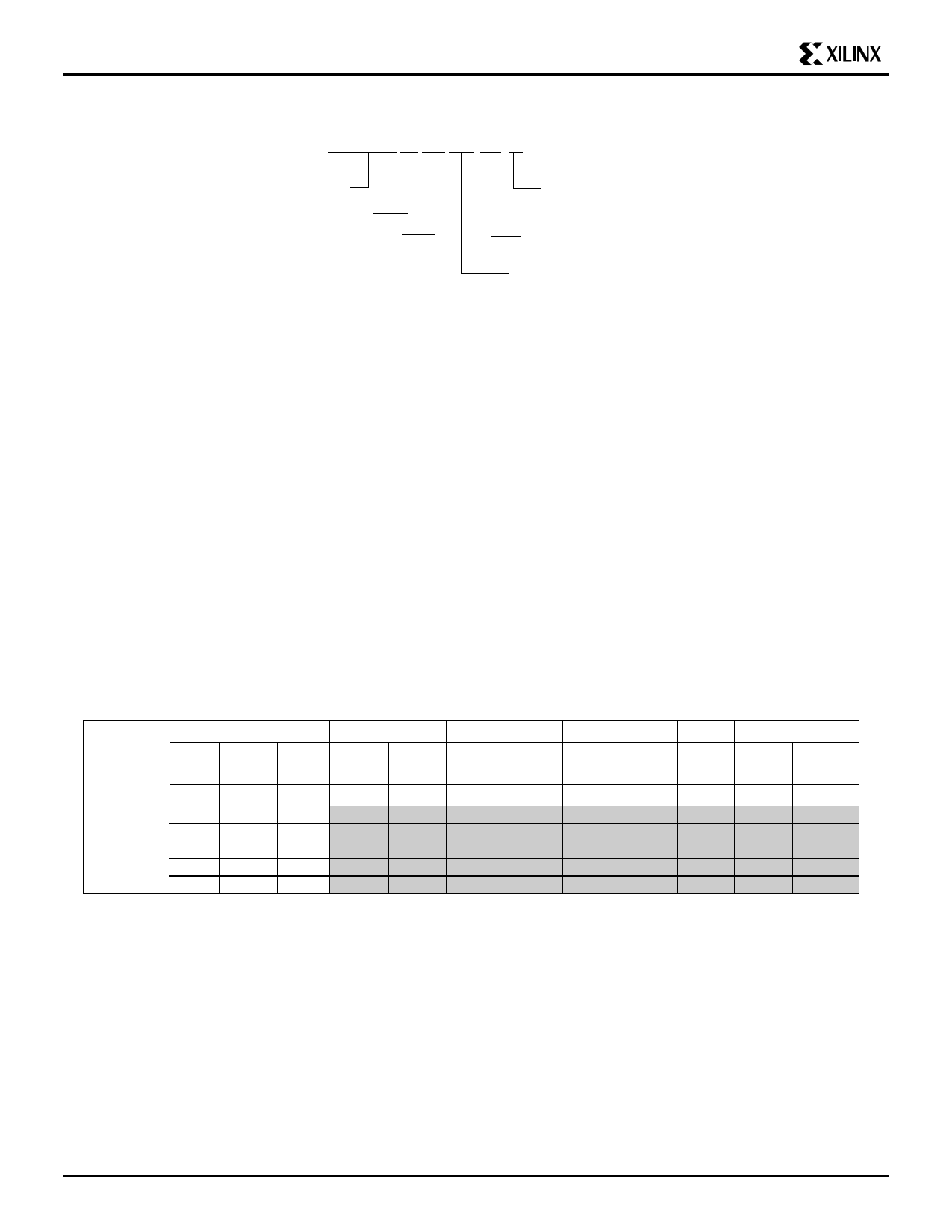

Figure 1. XC7336 Functional Block Diagram

2-23

This document was created with FrameMaker 4 0 2

PC44 PQ44

I/FI 42 36

I/FO

I/FO

I/FO

I/FO

I/FO

I/FO

I/FO

I/FO

FO/FOE1

29

30

33

34

35

36

37

38

39

23

24

27

28

29

30

31

32

33

FO/FOE0

I/FO/FI

I/FO/FI

I/FO/FI/MR

I/FO/FI

I/FO/FI

I/FO/FI

FO/FCLK0

FO/FCLK1

40

43

44

1

2

3

4

5

6

34

37

38

39

40

41

42

43

44

X5452

1 page

Here are just a few of the XEPLD Development System

features:

• Automatic Optimization and Mapping

Designs are automatically minimized and mapped into

the devices for optimal efficiency and high

performance. Critical logic functions are automatially

assigned to special resources such as high speed

clocks and global output enable signals. This allows

the user to concentrate on design functionality without

concern for physical implementation

• Automatic use of UIM Resources – SMARTswitch

The Universal Interconnect Maticx (UIM) used in Xilinx

EPLDs provides an additional level of logic at no

additional delay. XEPLD automatically uses the

inherent logic capability of the UIM when possible to

reduce Macrocell requirements and increase speed.

• N-to-1 PAL Conversion Utility

XEPLD automatically combines 20- and 24-pin

standard PAL files into one top-level design file,

checks for errors, and compiles the design into one or

more EPLDs. The N-to-1 PAL converter is ideal for

one step logic consolidation and board space

reduction.

• Complete Design Control

Users have the option to override the automatic

features of XEPLD and selectively control any or all

device resources.

• Multiple Platform Support

XEPLD runs on IBM Compatible PCs, Sun, HP700,

and IBM RS6000 platforms.

Notice: The information contained in this data sheet pertains to products in the initial production phases of development.

These specifications are subject to change without notice. Verify with your local Xilinx sales office that you have the latest

data sheet before finalizing a design.

Absolute Maximum Ratings

Symbol

VCC

VIN

VTS

TSTG

TSOL

Parameter

Supply voltage with respect to GND

DC Input voltage with respect to GND

Voltage applied to 3-state output with respect to GND

Storage temperature

Maximum soldering temperature (10s @ 1/16 in. = 1.5 mm)

Value

-0.5 to 7.0

-0.5 to VCC +0.5

-0.5 to VCC +0.5

-65 to +150

+250

Units

V

V

V

°C

°C

Warning: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed

under Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for

extended periods of time may affect device reliability.

Recommended Operating Conditions

Symbol

VCCINT/

VCCIO

VCCIO

VIL

VIH

VO

TIN

Parameter

Supply voltage relative to GND

Supply voltage relative to GND

Supply voltage relative to GND

I/O supply voltage relative to GND

Low-level input voltage

High-level input voltage

Output voltage

Input signal transition time

Commercial

TA = 0oC to 70oC

Industrial

TA = -40oC to 85oC

Military TA = -55oC to TC = +125oC

Min

4.75

4.50

4.50

3.0

0

2.00

0

Max

5.25

5.50

5.50

3.60

0.80

VCC +0.5

VCCIO

50

Units

V

V

V

V

V

V

V

ns

2-27

5 Page

Ordering Information

XC7336 - 5 PC 44 C

Device Type

Power Option

Speed

Temperature Range

Number of Pins

Package Type

Power Options

Q Low Power -10, -12, -15 speeds

Speed Options

-15 15 ns pin-to-pin delay

-12 12 ns pin-to-pin delay

-10 10 ns pin-to-pin delay

-7 7.5 ns pin-to-pin delay (commercial only)

-5 5 ns pin-to-pin delay (commercial only)

Packaging Options

PC44 44-Pin Plastic Leaded Chip Carrier

WC44 44-Pin Windowed Ceramic Leaded Chip Carrier

PQ44 44-Pin Plastic Quad Flat Pack

Temperature Options

C Commercial

I Industrial

0oC to70oC

-40oC to 85oC

Component Availability

Pins

44

68

84

100 144

160

Type

Plastic Ceramic Plastic Plastic Ceramic Plastic Ceramic Plastic Ceramic Plastic

PLCC CLCC PQFP PLCC CLCC PLCC CLCC PQFP PGA PQFP

Code

PC44 WC44 PQ44 PC68 WC68 PC84 WC84 PQ100 PG144 PQ160

XC7336

-15

-12

-10

-7

-5

CI

CI

CI

C

C

CI

CI

CI

C

C

C

C

C

C

C

C = Commercial = 0° to +70°C I = Industrial = -40° to 85°C

225

Plastic Windowed

BGA

BGA

BG225 WB225

X5650

®

The Programmable Logic Company SM

2-33

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet XC7336-12.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XC7336-10 | 36-Macrocell CMOS EPLD | Xilinx |

| XC7336-12 | 36-Macrocell CMOS EPLD | Xilinx |

| XC7336-15 | 36-Macrocell CMOS EPLD | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |