|

|

PDF SAA7707H Data sheet ( Hoja de datos )

| Número de pieza | SAA7707H | |

| Descripción | Car radio Digital Signal Processor CDSP | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SAA7707H (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA7707H

Car radio Digital Signal Processor

(CDSP)

Preliminary specification

Supersedes data of 1996 May 22

File under Integrated Circuits, IC01

1997 May 30

1 page

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

VDACPM

VDACNM

VrefMPX

VrefRDS

MPXRDS

AM

FM

AUXR

TAPER

TAPEL

AUXL

AMAF

FMMPX

FMRDS

CINT

VDACNL

VSSG

VSSA1

VSSD2

VSSD5

VSSD8

VDDD3

VSSD3

VSSD6

VSSD9

VDDD4

VSSD1

VSSD4

VSSD7

VDDD2

VDDD5

MUTE

MSS/P

VSSO

VDDD1

DEEM

VDDA VDDO VSSA

STEREO

VDDA1

VSSD1

77 2 1 67 68

78

70

80

62

4

3

72

74

73

ANALOG

71 SOURCE

75 SELECTOR

76

79

5

22 50 51

54 55 34

41 29 56 49 52 53

44 45 42 43 8 69 15 14 6 5 7

ADC

ADC

ADC

SIGNAL

LEVEL

SAA7707H

SIGNAL

QUALITY

INTERFERENCE

ABSORPTION

CIRCUIT

DIGITAL

STEREO

DECODER

DIGITAL

SOURCE

SELECTOR

DIGITAL

SIGNAL

PROCESSOR

40

20

13

18

19

16

17

QUADRATURE

DAC

11

12

9

10

EXCLK

Vref

Iref(int)

FIOL

FVOL

FIOR

FVOR

RIOL

RVOL

RIOR

RVOR

RDS

DECODER

CRYSTAL

OSCILLATOR

DIGITALLY

CONTROLLED

SAMPLING

I2C-BUS

21 POM

INTERFACE

32 33 30 66 65

60 61

64 63 23 24

25 48 47

46 59 57 58 35 36

28 27 37

TSCAN VDDX

SHTCB VSSX

RTCB

RDSDAT

RDSCLK

XTALO

CDWS

DCCWS

CDCLK

DCCDAT

XTALI

CDDAT

TEST1

EXSCL

TEST2

EXDAT

DCCCLK VSSD10

EXWS

EXDAT1

EXDAT2

38 39 31 26 MBH163

A0

SDA DSPRESET

SCL

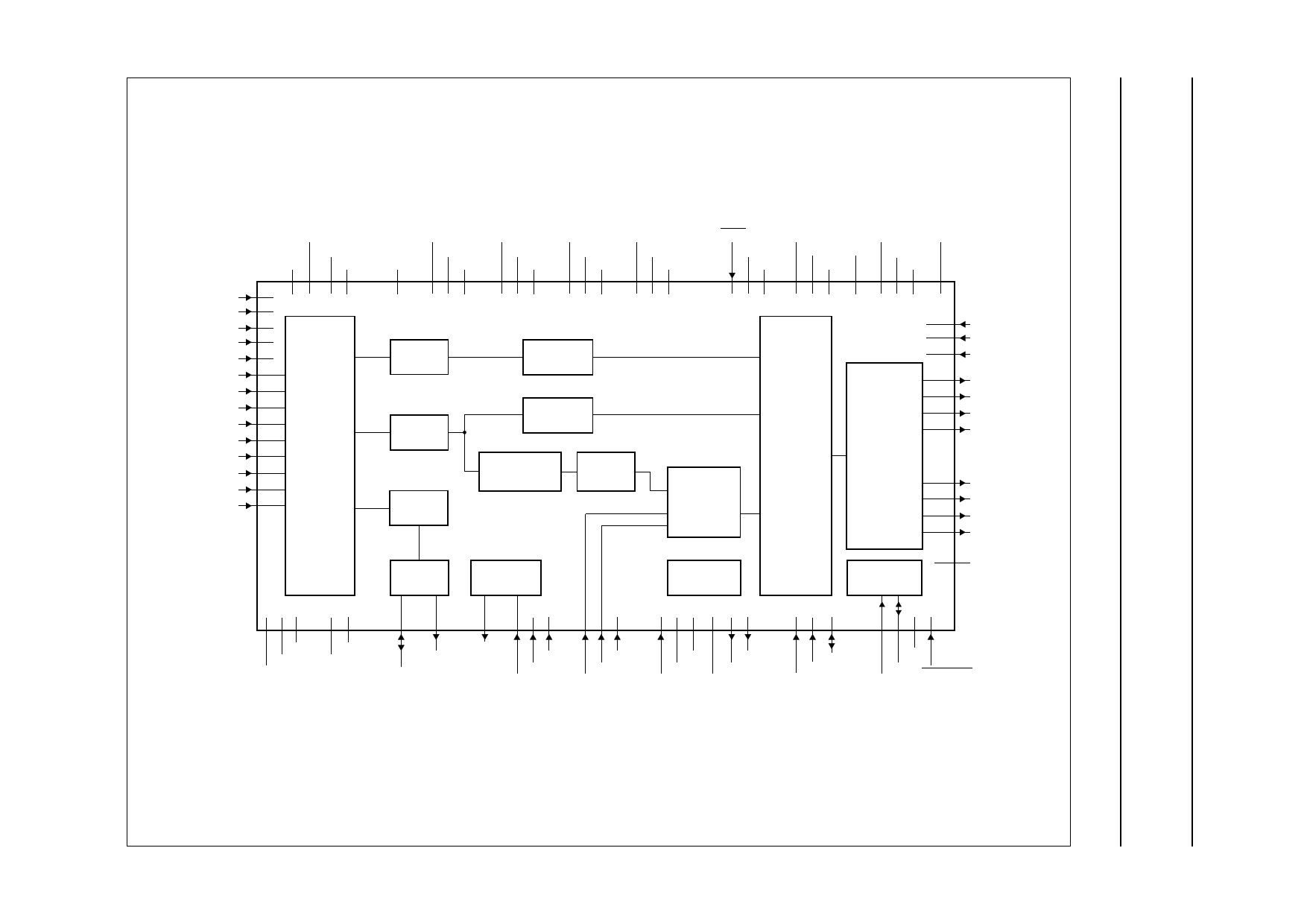

Fig.1 Block diagram.

5 Page

Philips Semiconductors

Car radio Digital Signal Processor (CDSP)

Preliminary specification

SAA7707H

8.4 Common mode reference voltage for RDS

ADC, ADC level and buffers (pin VrefRDS)

The middle reference voltage of the RDS ADC can be

filtered via this pin. This middle reference voltage is used

as a positive reference for the level ADC of the switch

capacitor DAC and as half supply reference for the RDS

ADC, the switch capacitor DACs and buffers. An external

capacitor (connected to VSSA1) prevents crosstalk

between the switch capacitor DACs of the RDS ADC, level

ADC and buffers, and improves the power supply rejection

ratio.

8.5 Signal path for audio/MPX and stereo decoder

The SAA7707H has four analog audio source inputs; two

single-multiplex channel inputs for AM and FM radio and

two stereo inputs for tape and auxiliary. The auxiliary input

can be used for functions such as an analog CD changer

or speech applications. The stereo inputs are multiplexed

so that they can share the same filters as the multiplexed

FM signal. The selection between the AM, FM, TAPE and

AUX input is made via the input selector control register.

The input signal behind the source selector is digitized by

a bitstream 3rd-order Sigma-Delta ADC. The first

decimation filter reduces the sample rate. This is followed

by the sample-and-hold switch of the IAC and the 19 kHz

regeneration circuit. From here, the wide-band noise

detector signal HP2 (High-Pass 2) with a frequency range

of 60 to 240 kHz is derived. A second decimation filter

reduces the output of the IAC to a lower sample rate.

This filter has two outputs, one for the multiplex signal with

a frequency range of 0 to 60 kHz (low-pass) and one for

the small-band noise detector signal HP1 (High-Pass 1)

with a frequency range of 60 to 120 kHz. The overall

low-pass frequency response of the decimation filters is

illustrated in Fig.4.

In the FM mode, the RDS ADC can be used as an input for

the MPX decimation filter. This can be selected via the

RDSMPX input at pin 62.

The outputs from this signal path to the DSP, which are all

at a sample frequency of 38 kHz, are as follows:

• Pilot presence indication: Pilot-I. This 1-bit signal is

LOW for a pilot frequency deviation of less than 4 kHz

and HIGH for a pilot frequency deviation greater than

4 kHz. It is AND locked on a pilot tone.

• Pilot quality indication: Pilot-Q. This 10-bit signal

contains information about the signal quality and is

derived from the quadrature component of the pilot-I

signal.

• ‘Left’ and ‘Right’: This is the 18-bit output of the stereo

decoder after the matrix decoding. For AM reception,

the ‘Right’ signal contains the AM-mono signal. For tape

or auxiliary signals, the output of the stereo decoder

contains sum and difference signals, but with other

crosstalk properties than on FM. Therefore, a different

matrix correction, as shown in Table 1, has to be applied

to these signals in the DSP program. The overall

frequency response of the demultiplexed signal at the

output of the stereo decoder is illustrated in Fig.5.

Table 1 Overview of the signals to the CDSP

MODE

AM

FM

TAPE/AUX

LEFT

0

1⁄2(R − L)

1⁄2(R + L) × 4/π

RIGHT

mono

R+L

R+L

Apart from the aforementioned theoretical response, the

non-flat frequency response of the ADC must also be

compensated for in the DSP program.

8.6 Mono/stereo switching

After division, the Digitally Controlled Sampling (DCS)

clock generates a clock signal with a frequency which is a

multiple of 19 kHz plus or minus a few Hertz. For mono

reception, the DCS circuit generates a preset frequency of

n × 19 kHz ±2 Hz. For stereo reception, the frequency is

exactly n × 19 kHz (DCS locked to n × pilot tone).

The detection of the pilot and the stereo indication is

performed in the DSP program.

8.7 The automatic lock system

The VCO operates at 19 kHz ±2 Hz exactly for no-pilot.

For stereo reception, the phase error is zero for a pilot tone

with a frequency of exactly 19 kHz. Therefore, no switch is

required to preset the clock to 19 kHz. With auxiliary

sources (tape, CD, etc.), the DCS circuit has to be preset

to a fixed value.

8.8 Input sensitivity for FM

The FM input sensitivity is optimally designed for an FM

front-end with an output voltage of 200 mV (RMS) at a

modulation depth of 22.5 kHz of a 1 kHz tone. Due to the

full-scale 1.2 V (RMS) handling capacity of the ADC, the

maximum allowed modulation depth of a transmitter, for a

THD of 10%, is 135 kHz. Full performance is possible for

transmitters with a modulation depth of up to 110 kHz.

1997 May 30

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SAA7707H.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA7707H | Car radio Digital Signal Processor CDSP | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |