|

|

PDF SAA7274P Data sheet ( Hoja de datos )

| Número de pieza | SAA7274P | |

| Descripción | Audio Digital Input Circuit ADIC | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SAA7274P (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA7274

Audio Digital Input Circuit (ADIC)

Product specification

File under Integrated Circuits, IC01

July 1991

1 page

Philips Semiconductors

Audio Digital Input Circuit (ADIC)

Product specification

SAA7274

FUNCTIONAL DESCRIPTION

Main function

The biphase input signal must conform to the IEC/EBU standards, IEC tech. com. No. 84, secr. 50, Jan. 1987 format,

as well as satisfying the following conditions:

• number of channels: 2

• transmission code: biphase mark

• synchronization method: biphase violation

• number of data bits: 24, starting with the LSB

• number of control bits: 4

• preamble values:

Table 1 Preamble values

preceding cell

block preamble

0

11101000

1

00010111

The main function performs the following tasks:

• Provides the output function with the equivalent binary value of the data bits separately for each of the two channels.

These values are available until new information is received.

• Generates an out-of-lock output signal (OLOC) which is HIGH when the frequency of the biphase input signal is equal

to 1/4 of the system clock frequency and when the block preambles are detected in the biphase input signal.

• If the biphase input signal is not present after 32 clock pulses and also whenever the biphase input signal and IOSCL/4

drift away from each other by more than 32 clock pulses, then the output OSCU is forced HIGH and output OSDU,

OPRE, OLOC, OCDB and OSDA are forced LOW.

• Generates a data clock output signal (ODCL) with a frequency of 1/4 of the system clock. When a block preamble is

detected in the biphase input signal ODCL is synchronized to a LOW value.

• Generates a word clock output signal (OWSY) with a frequency of 1/256 of the system clock. When a block preamble

is detected in the biphase input signal OWSY is synchronized to a LOW value.

• Generates a block synchronization output signal (OBSY). This signal is HIGH during 4 system clock periods and has

a frequency of 1/49152 of the system clock. The signal is synchronized with the block preambles of the biphase input

signal.

• Generates a phase output signal (OPHA) and a phase reference signal (OREF). If the frequency of the biphase input

signal (IBIFA) equals 1/4 of the system clock frequency (fIOSCL/4) then the IC generates OPHA and OREF as shown

in Fig.3.

If the frequency of the biphase input signal (IBIFA) is greater or less than 1/4 of the system clock frequency then the

IC generates OPHA and OREF as shown in Fig.4.

July 1991

5

5 Page

Philips Semiconductors

Audio Digital Input Circuit (ADIC)

Product specification

SAA7274

AC CHARACTERISTICS

VDD = 4.5 to 5.5 V.

Tamb = −40 to +70 °C.

Load capacitance (CL): OSCL = 50 pF; OWSY, ODCL and OSDA = 30 pF (see application note);

all other outputs = 20 pF.

Clock frequency fIOSCL = ≤ 12.5 MHz.

IOSCL timing pulse LOW, tLOW ≥ 37 ns; rise and fall times tr and tf = ≤ 10 ns.

Delay times are specified from clock input = 50% VDD to output = 50% VDD; unless otherwise specified

PARAMETER

CONDITIONS

SYMBOL MIN.

TYP.

MAX.

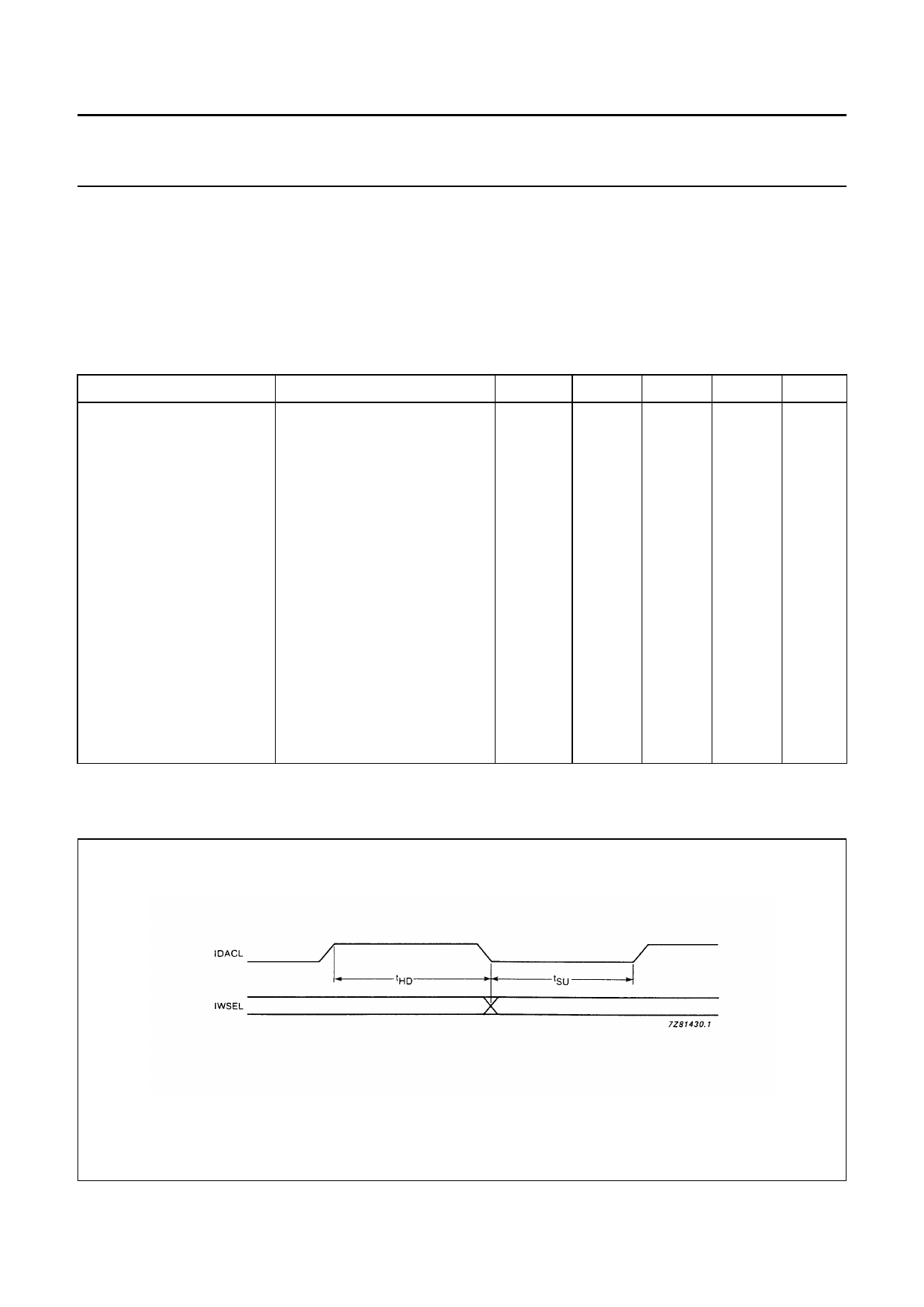

Set-up and hold times

IWSEL to IDACL

see Fig.5

Data set-up time

Data hold time

tSU 1 − −

tHD − − 1

Propagation delays

IOSCL to OSCL

IDACL to OSDA

OSCL to OWSY and ODCL

tp − − 25

tp − − 60

tp 5 − 50

Rise and fall times

OSCL

Rise and fall time

Rise and fall time

OWSY and ODCL

TTL levels = 0.4 to 2 V

tr, tf − − 10

CMOS levels = 10 to 90% VDD tr, tf

−

−

15

Rise and fall time

Rise and fall time

TTL levels = 0.4 to 2 V

tr, tf − − 15

CMOS levels = 10 to 90% VDD tr, tf

−

−

25

Note

1. Clock periods of OSCL.

UNIT

note 1

note 1

ns

ns

ns

ns

ns

ns

ns

July 1991

Fig.5 Set-up and hold time diagram.

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet SAA7274P.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA7274 | Audio Digital Input Circuit ADIC | NXP Semiconductors |

| SAA7274P | Audio Digital Input Circuit ADIC | NXP Semiconductors |

| SAA7274T | Audio Digital Input Circuit ADIC | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |