|

|

PDF SAA7108E Data sheet ( Hoja de datos )

| Número de pieza | SAA7108E | |

| Descripción | PC-CODEC | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SAA7108E (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA7108E; SAA7109E

PC-CODEC

Product specification

Supersedes data of 2001 Dec 12

2004 Mar 16

1 page

Philips Semiconductors

PC-CODEC

Product specification

SAA7108E; SAA7109E

3 GENERAL DESCRIPTION

The SAA7108E; SAA7109E is a new multi-standard video

decoder and encoder chip, offering high quality video input

and TV output processing as required by PC-99

specifications. It enables hardware manufacturers to

implement versatile video functions on a significantly

reduced printed-circuit board area at very competitive

costs.

Separate pins for supply voltages as well as for I2C-bus

control and boundary scan test have been provided for the

video encoder and decoder sections to ensure both

flexible handling and optimized noise behaviour.

The video encoder is used to encode PC graphics data at

maximum 800 × 600 resolution to PAL (50 Hz) or NTSC

(60 Hz) video signals. A programmable scaler and

interlacer ensures properly sized and flicker-free TV

display as CVBS or S-video output.

Alternatively, the three Digital-to-Analog Converters

(DACs) can output RGB signals together with a TTL

composite sync to feed SCART connectors.

When the scaler/interlacer is bypassed, a second VGA

monitor can be connected to the RGB outputs and

separate H and V-syncs as well, thereby serving as an

auxiliary monitor at maximum 800 × 600 resolution/60 Hz

(PIXCLK < 45 MHz).

The video decoder, a 9-bit video input processor, is a

combination of a 2-channel analog pre-processing circuit

including source selection, anti-aliasing filter and

Analog-to-Digital Converter (ADC), automatic clamp and

gain control, a Clock Generation Circuit (CGC), and a

digital multi-standard decoder (PAL BGHI, PAL M, PAL N,

combination PAL N, NTSC M, NTSC-Japan, NTSC N,

NTSC 4.43 and SECAM).

The decoder includes a brightness, contrast and

saturation control circuit, a multi-standard VBI data slicer

and a 27 MHz VBI data bypass. The pure 3.3 V (5 V

compatible) CMOS circuit SAA7108E; SAA7109E,

consisting of an analog front-end and digital video

decoder, a digital video encoder and analog back-end, is a

highly integrated circuit especially designed for desktop

video applications.

The decoder is based on the principle of line-locked clock

decoding and is able to decode the colour of PAL, SECAM

and NTSC signals into ITU-R BT.601 compatible colour

component values.

The encoder can operate fully independently at its own

variable pixel clock, transporting graphics input data, and

at the line-locked, single crystal-stable video encoding

clock.

As an option, it is possible to slave the video PAL/NTSC

encoding to the video decoder clock with the encoder FIFO

acting as a buffer to decouple the line-locked decoder

clock from the crystal-stable encoder clock.

4 QUICK REFERENCE DATA

SYMBOL

PARAMETER

CONDITIONS

MIN. TYP. MAX. UNIT

VDDD

VDDA

Tamb

PA+D

digital supply voltage

analog supply voltage

ambient temperature

analog and digital power dissipation

note 1

3.0 3.3

3.15 3.3

0−

−−

3.6 V

3.45 V

70 °C

1.4 W

Note

1. Power dissipation is extremely dependent on programming and selected application.

5 ORDERING INFORMATION

TYPE

NUMBER

SAA7108E

SAA7109E

NAME

BGA156

PACKAGE

DESCRIPTION

plastic ball grid array package; 156 balls; body 15 × 15 × 1.15 mm

VERSION

SOT472-1

2004 Mar 16

5

5 Page

Philips Semiconductors

PC-CODEC

Product specification

SAA7108E; SAA7109E

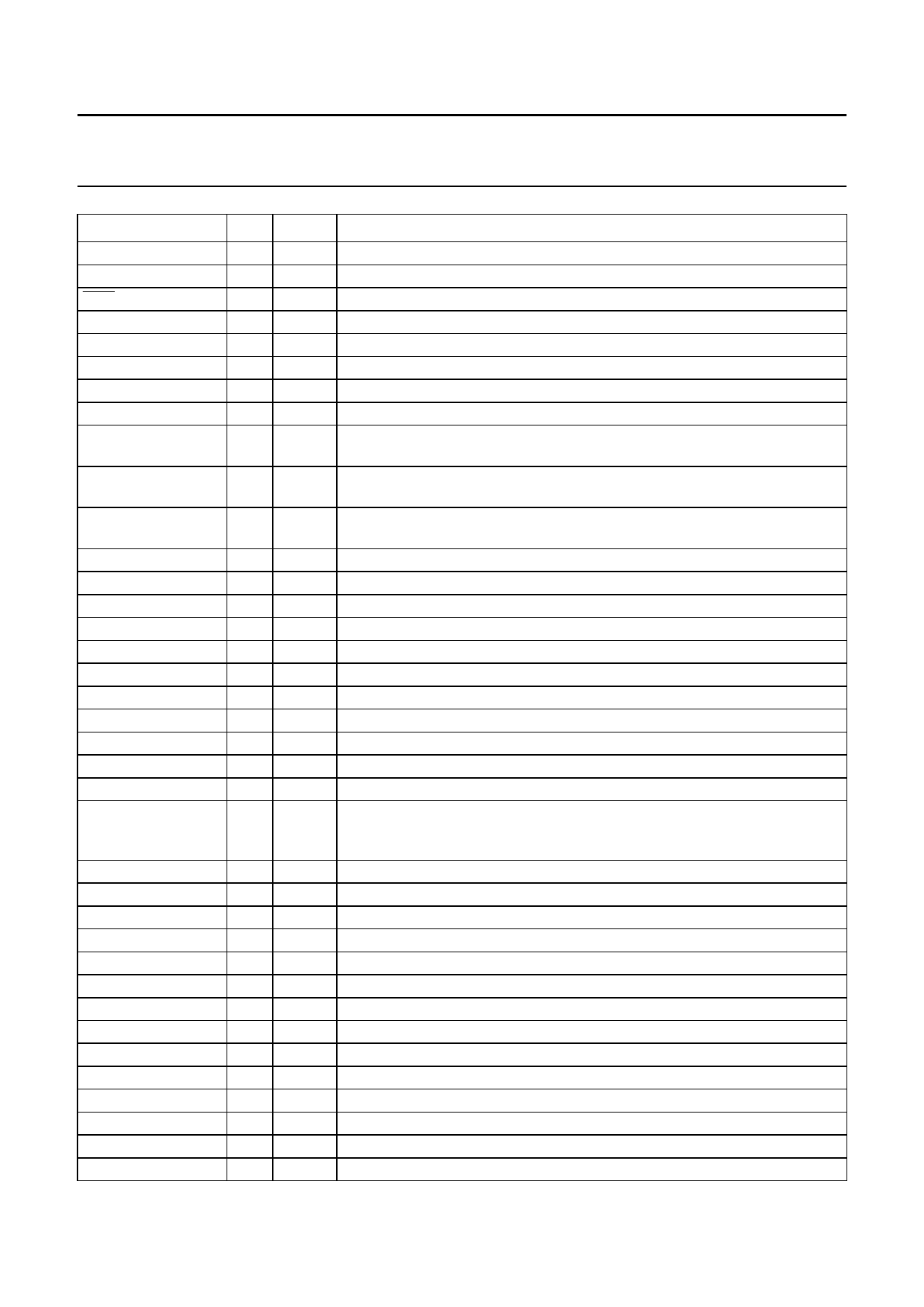

SYMBOL

FSVGC

SDAe

CBO

PIXCLKO

VDDEd

IGPH

IGP1

ITRI

PD2

PD1

PD0

VSSEd

VSSEd

ICLK

TEST0

IDQ

TEST4

TEST5

TEST3

VDDId

VDDId

AMXCLK

ALRCLK

ITRDY

XTRI

XPD7

XPD6

VSSId

VSSId

AMCLK

RTS0

ASCLK

XPD5

XPD4

XPD3

VDDId

XRV

2004 Mar 16

PIN TYPE(1)

DESCRIPTION

G1 I/O frame synchronization output to VGC (optional input)

G2 I/O I2C-bus serial data input/output (encoder)

G3 O composite blanking output to VGC; active LOW

G4 O pixel clock output to VGC

G11 S 3.3 V digital supply voltage for peripheral cells (decoder)

G12 O multi-purpose horizontal reference output with IPD output bus

G13 O general purpose output signal 1 with IPD output bus

G14 I/(O) programmable control signals for IPD output bus

H1 I MSB − 5 of encoder input bus with CB-Y-CR 4 : 2 : 2; see Tables 25 to 31 for

pin assignment

H2 I MSB − 6 of encoder input bus with CB-Y-CR 4 : 2 : 2; see Tables 25 to 31 for

pin assignment

H3 I MSB − 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; see Tables 25 to 31 for

pin assignment

H4 S digital ground for peripheral cells (decoder)

H11 S digital ground for peripheral cells (decoder)

H12 I/O clock for IPD output bus (optional clock input)

H13 O scan test output, do not connect

H14 O data qualifier for IPD output bus

J1 O scan test output, do not connect

J2 I scan test input, do not connect

J3 I scan test input, do not connect

J4 S 3.3 V digital supply voltage for core (decoder)

J11 S 3.3 V digital supply voltage for core (decoder)

J12 I audio master external clock input

J13 (I/)O audio left/right clock output; can be strapped to supply via a 3.3 kΩ resistor to

indicate that the default 24.576 MHz crystal (ALRCLK = 0; internal pull-down)

has been replaced by a 32.110 MHz crystal (ALRCLK = 1); notes 5 and 6

J14 I target ready input for IPD output bus

K1 I control signal for all X port pins

K2 I/O MSB of XPD bus

K3 I/O MSB − 1 of XPD bus

K4 S digital ground core (decoder)

K11 S digital ground core (decoder)

K12 O audio master clock output, must be less than 50% of crystal clock

K13 O real-time status or sync information line 0

K14 O audio serial clock output

L1 I/O MSB − 2 of XPD bus

L2 I/O MSB − 3 of XPD bus

L3 I/O MSB − 4 of XPD bus

L4 S 3.3 V digital supply voltage for core (decoder)

L5 I/O vertical reference for XPD bus

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SAA7108E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA7108 | PC-CODEC | NXP Semiconductors |

| SAA7108E | PC-CODEC | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |