|

|

PDF K4S641632C Data sheet ( Hoja de datos )

| Número de pieza | K4S641632C | |

| Descripción | 1M x 16Bit x 4 Banks Synchronous DRAM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K4S641632C (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

K4S641632C

1M x 16Bit x 4 Banks Synchronous DRAM

CMOS SDRAM

FEATURES

• JEDEC standard 3.3V power supply

• LVTTL compatible with multiplexed address

• Four banks operation

• MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page)

-. Burst type (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system

clock

• Burst read single-bit write operation

• DQM for masking

• Auto & self refresh

• 64ms refresh period (4K cycle)

FUNCTIONAL BLOCK DIAGRAM

GENERAL DESCRIPTION

The K4S641632C is 67,108,864 bits synchronous high data

rate Dynamic RAM organized as 4 x 1,048,576 words by 16

bits, fabricated with SAMSUNG′s high performance CMOS

technology. Synchronous design allows precise cycle control

with the use of system clock I/O transactions are possible on

every clock cycle. Range of operating frequencies, programma-

ble burst length and programmable latencies allow the same

device to be useful for a variety of high bandwidth, high perfor-

mance memory system applications.

ORDERING INFORMATION

Part No.

K4S641632C-TC/L60

K4S641632C-TC/L70

K4S641632C-TC/L75

K4S641632C-TC/L80

K4S641632C-TC/L1H

K4S641632C-TC/L1L

K4S641632C-TC/L10

Max Freq. Interface Package

166MHz(CL=3)

143MHz(CL=3)

133MHz(CL=3)

125MHz(CL=3)

100MHz(CL=2)

LVTTL

54

TSOP(II)

100MHz(CL=3)

66MHz(CL=3&2)

Data Input Register

CLK

ADD

Bank Select

1M x 16

1M x 16

1M x 16

1M x 16

Column Decoder

LCKE

LRAS LCBR

LWE

LCAS

Latency & Burst Length

Programming Register

LWCBR

Timing Register

LWE

LDQM

DQi

LDQM

CLK CKE

CS

RAS

CAS

WE L(U)DQM

* Samsung Electronics reserves the right to change products or specification without notice.

1 page

K4S641632C

AC OPERATING TEST CONDITIONS (VDD = 3.3V ± 0.3V, TA = 0 to 70°C)

Parameter

AC input levels (Vih/Vil)

Input timing measurement reference level

Input rise and fall time

Output timing measurement reference level

Output load condition

Value

2.4/0.4

1.4

tr/tf = 1/1

1.4

See Fig. 2

3.3V

Output

870Ω

1200Ω

VOH (DC) = 2.4V, IOH = -2mA

VOL (DC) = 0.4V, IOL = 2mA

50pF*Note1

Output

CMOS SDRAM

Unit

V

V

ns

V

Z0 = 50Ω

Vtt = 1.4V

50Ω

50pF*Note1

(Fig. 1) DC output load circuit

Note : 1. The DC/AC test Output Load of K4S641632C-60 is 30pF.

2. The VDD condition of K4S641632C-60 is 3.135V~3.6V.

(Fig. 2) AC output load circuit

OPERATING AC PARAMETER

(AC operating conditions unless otherwise noted)

Parameter

Symbol

Version

Unit

-60 -70 -75 -80 -1H -1L -10

Row active to row active delay

tRRD(min) 12 14 14 16 20 20 20 ns

RAS to CAS delay

tRCD(min) 18 20 20 20 20 20 24 ns

Row precharge time

tRP(min)

18

20

20

20

20

20

24 ns

Row active time

tRAS(min)

42

48

48

48

50

50

50 ns

tRAS(max)

100

us

Row cycle time

tRC(min)

60

68

68

68

70

70

80 ns

Last data in to row precharge

tRDL(min)

6

7

7

8 10 10 12 ns

Last data in to new col. address Delay tCDL(min) 1 CLK

Last data in to burst stop

tBDL(min)

1

CLK

Col. address to col. address delay

tCCD(min)

1

CLK

Number of valid output

data

CAS latency=3

CAS latency=2

2

ea

1

Notes : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time

and then rounding off to the next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

Not

e

1

1

1

1

1

2

2

2

3

4

5 Page

K4S641632C

CMOS SDRAM

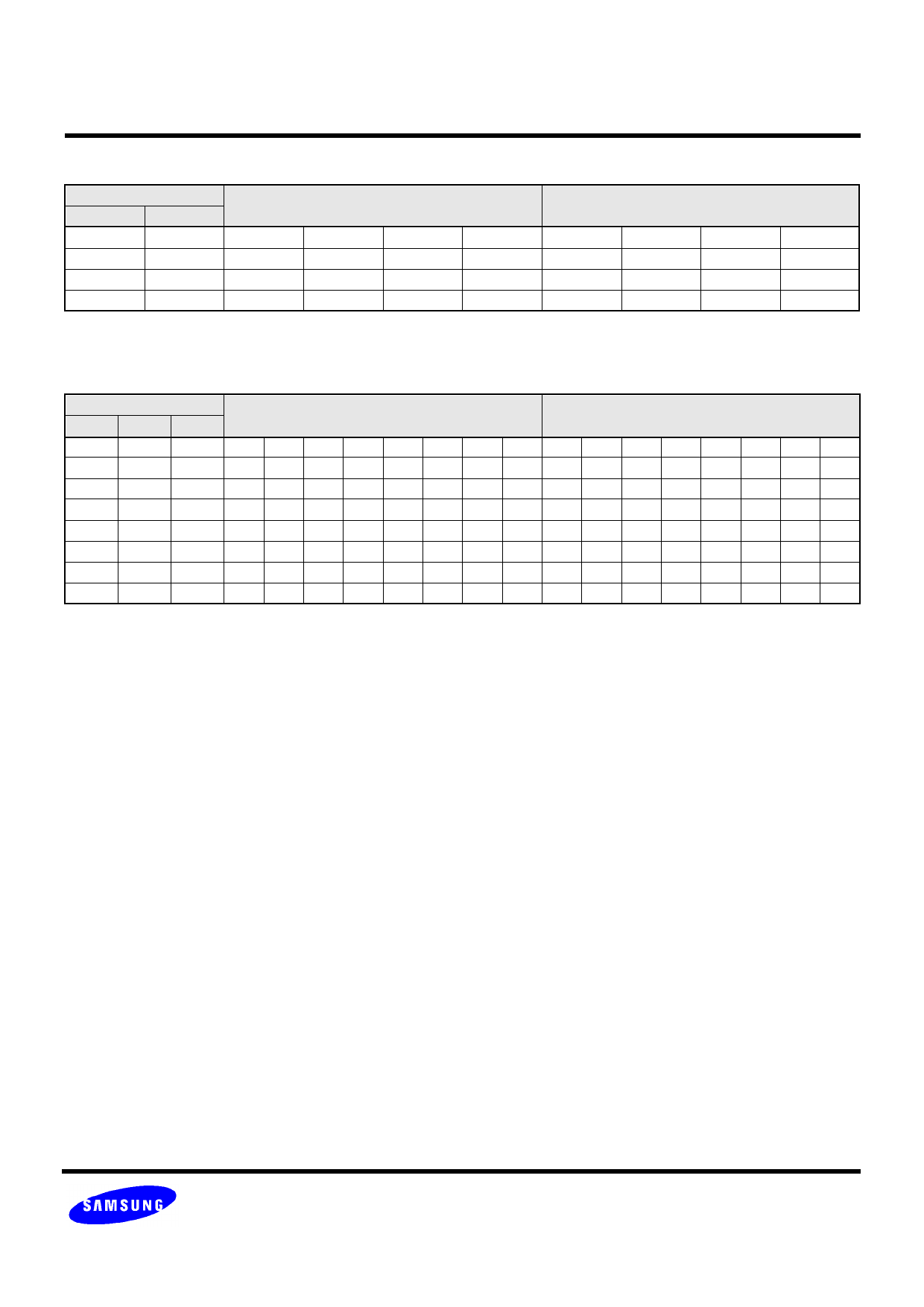

BURST SEQUENCE (BURST LENGTH = 4)

Initial Address

A1 A0

Sequential

Interleave

0001230123

0112301032

1023012301

1130123210

BURST SEQUENCE (BURST LENGTH = 8)

Initial Address

A2 A1 A0

Sequential

Interleave

0 0 0 0 123 4 5 6 70 1234 5 6 7

0 0 1 1 234 5 6 7 01 0325 4 7 6

0 1 0 2 345 6 7 0 12 3016 7 4 5

0 1 1 3 456 7 0 1 23 2107 6 5 4

1 0 0 4 567 0 1 2 34 5670 1 2 3

1 0 1 5 670 1 2 3 45 4761 0 3 2

1 1 0 6 701 2 3 4 56 7452 3 0 1

1 1 1 7 012 3 4 5 67 6543 2 1 0

ELECTRONICS

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet K4S641632C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4S641632C | 1M x 16Bit x 4 Banks Synchronous DRAM | Samsung semiconductor |

| K4S641632D | 64Mbit SDRAM 1M x 16Bit x 4 Banks Synchronous DRAM LVTTL | Samsung semiconductor |

| K4S641632E | 64Mbit SDRAM | Samsung semiconductor |

| K4S641632F | 64Mbit SDRAM 1M x 16Bit x 4 Banks Synchronous DRAM LVTTL | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |