|

|

PDF K4S161622E-TC60 Data sheet ( Hoja de datos )

| Número de pieza | K4S161622E-TC60 | |

| Descripción | 1M x 16 SDRAM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K4S161622E-TC60 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

K4S161622E

CMOS SDRAM

1M x 16 SDRAM

512K x 16bit x 2 Banks

Synchronous DRAM

LVTTL

Revision 1.1

Jan 2003

Samsung Electronics reserves the right to change products or specification without notice.

Rev 1.1 Jan '03

1 page

K4S161622E

CMOS SDRAM

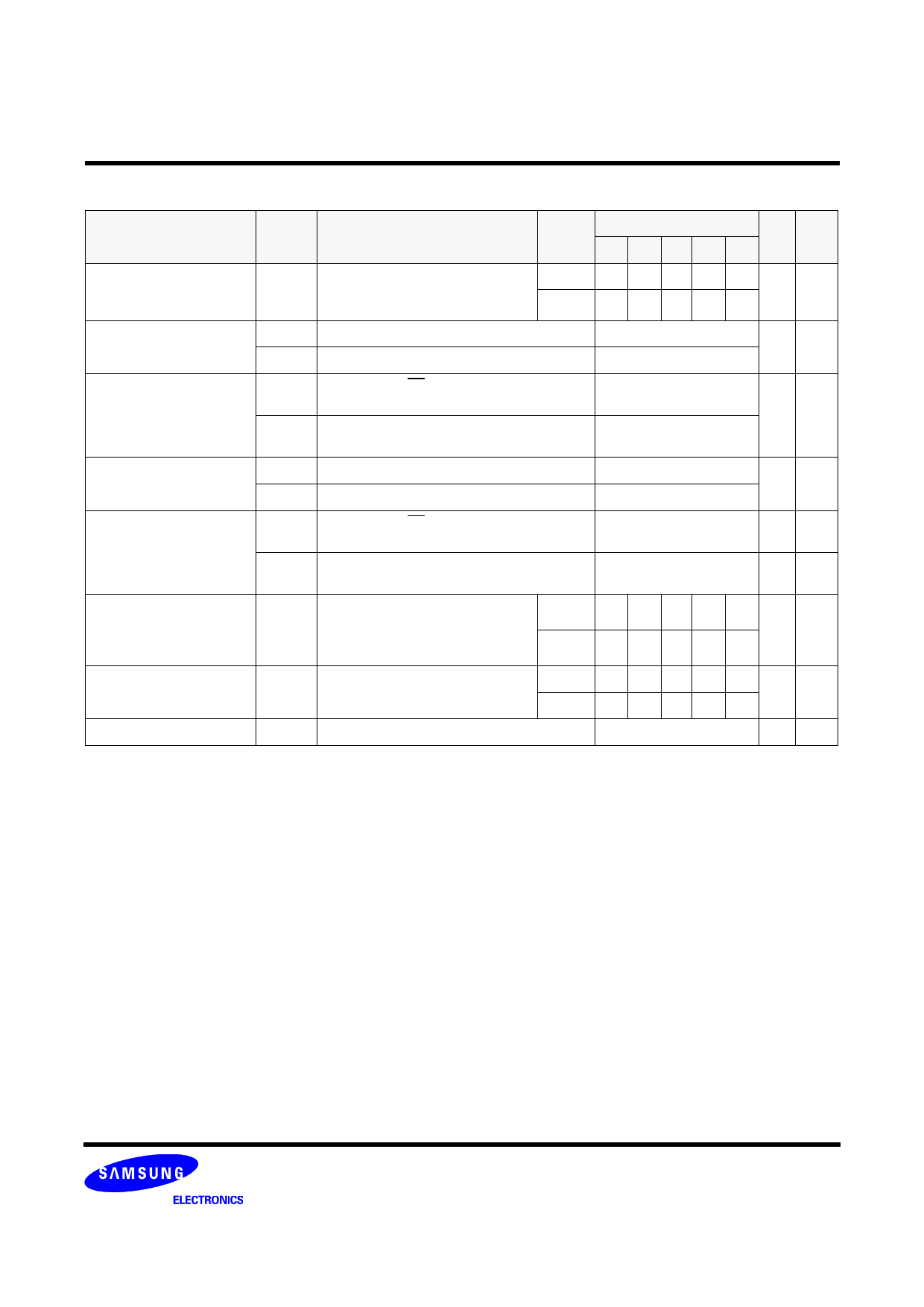

DC CHARACTERISTICS

(Recommended operating condition unless otherwise noted, TA = 0 to 70°C)

Parameter

Symbol

Test Condition

CAS

Latency -55

Version

-60 -70 -80

-10

Unit

Note

Operating Current

(One Bank Active)

Burst Length =1

ICC1

tRC≥tRC(min)

Io = 0 mA

3 120 115 105 95 85

mA 2

2 - - 95 95 80

Precharge Standby Current

in power-down mode

ICC2P

ICC2PS

CKE≤VIL(max), tCC = 15ns

CKE & CLK≤VIL(max), tCC = ∞

2

mA

2

Precharge Standby Current

in non power-down mode

ICC2N

ICC2NS

CKE≥VIH(min), CS≥VIH(min), tCC = 15ns

Input signals are changed one time during 30ns

CKE≥VIH(min), CLK≤VIL(max), tCC = ∞

Input signals are stable

15

5

mA

Active Standby Current

in power-down mode

ICC3P

ICC3PS

CKE≤VIL(max), tCC = 15ns

CKE & CLK≤VIL(max), tCC = ∞

3

mA

3

Active Standby Current

ICC3N

CKE≥VIH(min), CS≥VIH(min), tCC = 15ns

Input signals are changed one time during 30ns

25

mA

in non power-down mode

(One Bank Active)

ICC3NS

CKE≥VIH(min), CLK≤VIL(max), tCC = ∞

Input signals are stable

15 mA

Operating Current

(Burst Mode)

Io = 0 mA

3 155 150 140 130 115

ICC4 Page Burst 2Banks Activated

mA 2

tCCD = 2CLKs

2 - - 115 115 100

Refresh Current

Self Refresh Current

ICC5

ICC6

tRC≥tRC(min)

CKE≤0.2V

3 105 100 90 90 80

mA 3

2 - - 90 90 80

1 mA 4

Note : 1. Unless otherwise notes, Input level is CMOS(VIH/VIL=VDDQ/VSSQ) in LVTTL.

2. Measured with outputs open. Addresses are changed only one time during tcc(min).

3. Refresh period is 32ms. Addresses are changed only one time during tcc(min).

4. K4S161622E-TC**

Rev 1.1 Jan '03

5 Page

K4S161622E

CMOS SDRAM

DEVICE OPERATIONS

CLOCK (CLK)

The clock input is used as the reference for all SDRAM opera-

tions. All operations are synchronized to the positive going edge

of the clock. The clock transitions must be monotonic between

VIL and VIH. During operation with CKE high all inputs are

assumed to be in a valid state (low or high) for the duration of

set-up and hold time around positive edge of the clock in order

to function well Q perform and ICC specifications.

CLOCK ENABLE (CKE)

The clock enable(CKE) gates the clock onto SDRAM. If CKE

goes low synchronously with clock (set-up and hold time are the

same as other inputs), the internal clock is suspended from the

next clock cycle and the state of output and burst address is fro-

zen as long as the CKE remains low. All other inputs are ignored

from the next clock cycle after CKE goes low. When all banks

are in the idle state and CKE goes low synchronously with clock,

the SDRAM enters the power down mode from the next clock

cycle. The SDRAM remains in the power down mode ignoring

the other inputs as long as CKE remains low. The power down

exit is synchronous as the internal clock is suspended. When

CKE goes high at least "1CLK + tSS" before the high going edge

of the clock, then the SDRAM becomes active from the same

clock edge accepting all the input commands.

BANK ADDRESS (BA)

: In case x 4

This SDRAM is organized as two independent banks of

2,097,152 words x 4 bits memory arrays. The BA input is latched

at the time of assertion of RAS and CAS to select the bank to be

used for the operation. The bank select BA is latched at bank

active, read, write, mode register set and precharge operations.

: In case x 8

This SDRAM is organized as two independent banks of

1,048,576 words x 8 bits memory arrays. The BA input is latched

at the time of assertion of RAS and CAS to select the bank to be

used for the operation. The bank select BA is latched at bank

active, read, write, mode register set and precharge operations.

: In case x 16

This SDRAM is organized as two independent banks of 524,288

words x 16 bits memory arrays. The BA input is latched at the

time of assertion of RAS and CAS to select the bank to be used

for the operation. The bank select BA is latched at bank active,

read, write, mode register set and precharge operations.

ADDRESS INPUTS (A0 ~ A10/AP)

: In case x 4

The 21 address bits are required to decode the 2,097,152 word

locations are multiplexed into 11 address input pins (A0 ~ A10/

AP). The 11 bit row addresses are latched along with RAS and

BA during bank activate command. The 10 bit column

addresses are latched along with CAS, WE and BA during read

or write command.

: In case x 8

The 20 address bits are required to decode the 1,048,576 word

locations are multiplexed into 11 address input pins (A0 ~ A10/

AP). The 11 bit row addresses are latched along with RAS and

BA during bank activate command. The 9 bit column addresses

are latched along with CAS, WE and BA during read or write

command.

: In case x 16

The 19 address bits are required to decode the 524,288 word

locations are multiplexed into 11 address input pins (A0 ~ A10/

AP). The 11 bit row addresses are latched along with RAS and

BA during bank activate command. The 8 bit column addresses

are latched along with CAS, WE and BA during read or write

command.

NOP and DEVICE DESELECT

When RAS, CAS and WE are high, the SDRAM performs no

operation (NOP). NOP does not initiate any new operation, but

is needed to complete operations which require more than sin-

gle clock cycle like bank activate, burst read, auto refresh, etc.

The device deselect is also a NOP and is entered by asserting

CS high. CS high disables the command decoder so that RAS,

CAS, WE and all the address inputs are ignored.

POWER-UP

SDRAMs must be powered up and initialized in a pre-

defined manner to prevent undefined operations.

1. Apply power and start clock. Must maintain CKE= "H", DQM=

"H" and the other pins are NOP condition at the inputs.

2. Maintain stable power, stable clock and NOP input condition

for a minimum of 200us.

3. Issue precharge commands for both banks of the devices.

4. Issue 2 or more auto-refresh commands.

5. Issue a mode register set command to initialize the mode reg-

ister.

cf.) Sequence of 4 & 5 is regardless of the order.

The device is now ready for normal operation.

Rev 1.1 Jan '03

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet K4S161622E-TC60.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4S161622E-TC60 | 1M x 16 SDRAM | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |