|

|

PDF K4R441869A Data sheet ( Hoja de datos )

| Número de pieza | K4R441869A | |

| Descripción | 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K4R441869A (archivo pdf) en la parte inferior de esta página. Total 64 Páginas | ||

|

No Preview Available !

K4R271669A/K4R441869A

Direct RDRAM™

128/144Mbit RDRAM

256K x 16/18 bit x 2*16 Dependent Banks

Direct RDRAMTM

Revision 1.02

January 2000

Page -1

Rev. 1.02 Jan. 2000

1 page

K4R271669A/K4R441869A

Direct RDRAM™

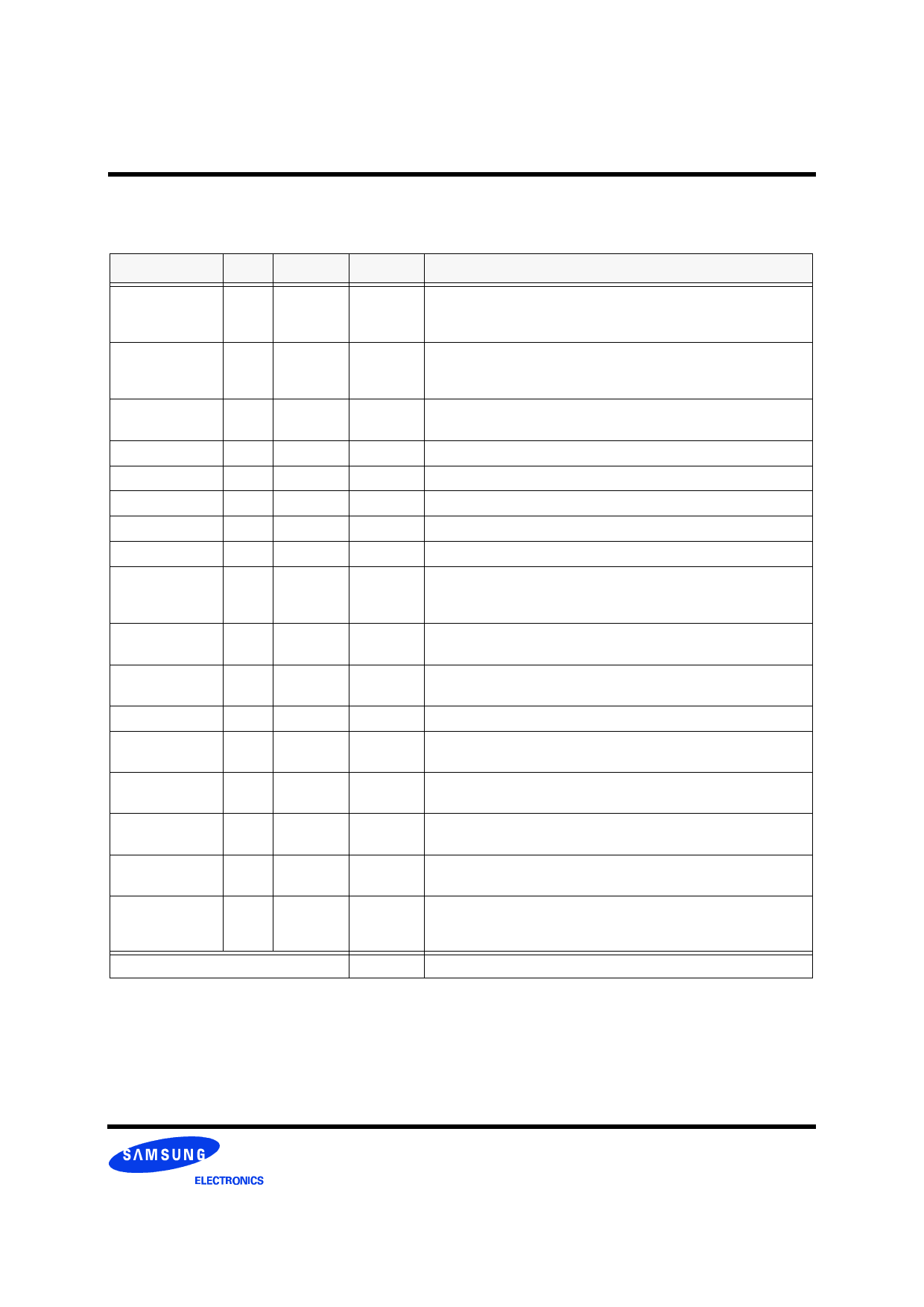

Table 3: Pin Description

Signal

SIO1,SIO0

I/O Type

I/O CMOSa

CMD

I CMOSa

SCK

VDD

VDDa

VCMOS

GND

GNDa

DQA8..DQA0

I CMOSa

I/O RSLb

CFM

CFMN

I RSLb

I RSLb

VREF

CTMN

I

CTM

I

RQ7..RQ5 or

ROW2..ROW0

RQ4..RQ0 or

COL4..COL0

DQB8..

DQB0

I

I

I/O

RSLb

RSLb

RSLb

RSLb

RSLb

Total pin count per package

# of Pins

2

1

1

10

1

2

13

1

9

1

1

1

1

1

3

5

9

62

Description

Serial input/output. Pins for reading from and writing to the control

registers using a serial access protocol. Also used for power man-

agement.

Command input. Pins used in conjunction with SIO0 and SIO1 for

reading from and writing to the control registers. Also used for

power management.

Serial clock input. Clock source used for reading from and writing to

the control registers

Supply voltage for the RDRAM core and interface logic.

Supply voltage for the RDRAM analog circuitry.

Supply voltage for CMOS input/output pins.

Ground reference for RDRAM core and interface.

Ground reference for RDRAM analog circuitry.

Data byte A. Nine pins which carry a byte of read or write data

between the Channel and the RDRAM. DQA8 is not used by

RDRAMs with a x16 organization.

Clock from master. Interface clock used for receiving RSL signals

from the Channel. Positive polarity.

Clock from master. Interface clock used for receiving RSL signals

from the Channel. Negative polarity

Logic threshold reference voltage for RSL signals

Clock to master. Interface clock used for transmitting RSL signals

to the Channel. Negative polarity.

Clock to master. Interface clock used for transmitting RSL signals

to the Channel. Positive polarity.

Row access control. Three pins containing control and address

information for row accesses.

Column access control. Five pins containing control and address

information for column accesses.

Data byte B. Nine pins which carry a byte of read or write data

between the Channel and the RDRAM. DQB8 is not used by

RDRAMs with a x16 organization.

a. All CMOS signals are high-true; a high voltage is a logic one and a low voltage is logic zero.

b. All RSL signals are low-true; a low voltage is a logic one and a high voltage is logic zero.

Page 3 Rev. 1.02 Jan. 2000

5 Page

K4R271669A/K4R441869A

Direct RDRAM™

Table 8 shows the COP field encoding. The device must be

in the ATTN power state in order to receive COLC packets.

The COLC packet is used primarily to specify RD (read) and

WR (write) commands. Retire operations (moving data from

the write buffer to a sense amp) happen automatically. See

Figure 17 for a more detailed description.

The COLC packet can also specify a PREC command,

which precharges a bank and its associated sense amps. The

RDA/WRA commands are equivalent to combining RD/WR

with a PREC. RLXC (relax) performs a power mode transi-

tion. See “ Power State Management “ on page 38.

Table 8: COLC Packet Field Encodings

S DC4.. DC0

(select device)a

0 ----

1 /= (DEVID4 ..0)

1 == (DEVID4 ..0)

1 == (DEVID4 ..0)

1 == (DEVID4 ..0)

1 == (DEVID4 ..0)

1 == (DEVID4 ..0)

1 == (DEVID4 ..0)

1 == (DEVID4 ..0)

1 == (DEVID4 ..0)

1 == (DEVID4 ..0)

COP3..0 Name Command Description

-----

-----

x000b

x001

x010

x011

x100

x101

x110

x111

1xxx

- No operation.

- Retire write buffer of this device.

NOCOP Retire write buffer of this device.

WR Retire write buffer of this device, then write column C5..C0 of bank BC4..BC0 to write buffer.

RSRV Reserved, no operation.

RD Read column C5..C0 of bank BC4..BC0 of this device.

PREC Retire write buffer of this device, then precharge bank BC4..BC0 (see Figure 14).

WRA Same as WR, but precharge bank BC4..BC0 after write buffer (with new data) is retired.

RSRV Reserved, no operation.

RDA Same as RD, but precharge bank BC4..BC0 afterward.

RLXC Move this device into the standby (STBY) power state (see Figure 46).

a. “ /= “ means not equal, “ == “ means equal.

b. An “ x“ entry indicates which commands may be combined. For instance, the two commands WR/RLXC may be specified in one COP value(1001).

Table 9 shows the COLM and COLX field encodings. The

M bit is asserted to specify a COLM packet with two 8 bit

bytemask fields MA and MB. If the M bit is not asserted, an

COLX is specified. It has device and bank address fields,

and an opcode field. The primary use of the COLX packet is

to permit an independent PREX (precharge) command to be

specified without consuming control bandwidth on the ROW

pins. It is also used for the CAL(calibrate) and SAM

(sample) current control commands (see “Current and

Temperature Control“ on page 43), and for the RLXX power

mode command (see “Power State Management“ on page

38).

Table 9: COLM Packet and COLX Packet Field Encodings

M

DX4 .. DX0

(selects device)

1 ----

0 /= (DEVID4 ..0)

0 == (DEVID4 ..0)

0 == (DEVID4 ..0)

0 == (DEVID4 ..0)

0 == (DEVID4 ..0)

0 == (DEVID4 ..0)

0 == (DEVID4 ..0)

XOP4..0

-

-

00000

1xxx0a

x10x0

x11x0

xxx10

xxxx1

Name

MSK

-

NOXOP

PREX

CAL

CAL/SAM

RLXX

RSRV

Command Description

MB/MA bytemasks used by WR/WRA.

No operation.

No operation.

Precharge bank BX4..BX0 of this device (see Figure 14).

Calibrate (drive) IOL current for this device (see Figure 51).

Calibrate (drive) and Sample ( update) IOL current for this device (see Figure 51).

Move this device into the standby (STBY) power state (see Figure 46).

Reserved, no operation.

a. An “x“ entry indicates which commands may be combined. For instance, the two commands PREX/RLXX may be specified in one XOP value (10010).

Page 9 Rev. 1.02 Jan. 2000

11 Page | ||

| Páginas | Total 64 Páginas | |

| PDF Descargar | [ Datasheet K4R441869A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4R441869A | 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM | Samsung semiconductor |

| K4R441869A-NMCG6 | 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM | Samsung semiconductor |

| K4R441869A-NMCK7 | 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM | Samsung semiconductor |

| K4R441869A-NMCK8 | 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |