|

|

PDF IMIZ9972 Data sheet ( Hoja de datos )

| Número de pieza | IMIZ9972 | |

| Descripción | 3.3V/ 125-MHz/ Multi-Output Zero Delay Buffer | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de IMIZ9972 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

Z9972

3.3V, 125-MHz, Multi-Output Zero Delay Buffer

Features

• Output frequency up to 125 MHz

• 12 clock outputs: frequency configurable

• 350 ps max output-to-output skew

• Configurable output disable

• Two reference clock inputs for dynamic toggling

• Oscillator or crystal reference input

• Spread Spectrum-compatible

• Glitch-free output clocks transitioning

• 3.3V power supply

• Pin-compatible with MPC972

• Industrial temperature range: –40°C to +85°C

• 52-pin TQFP package

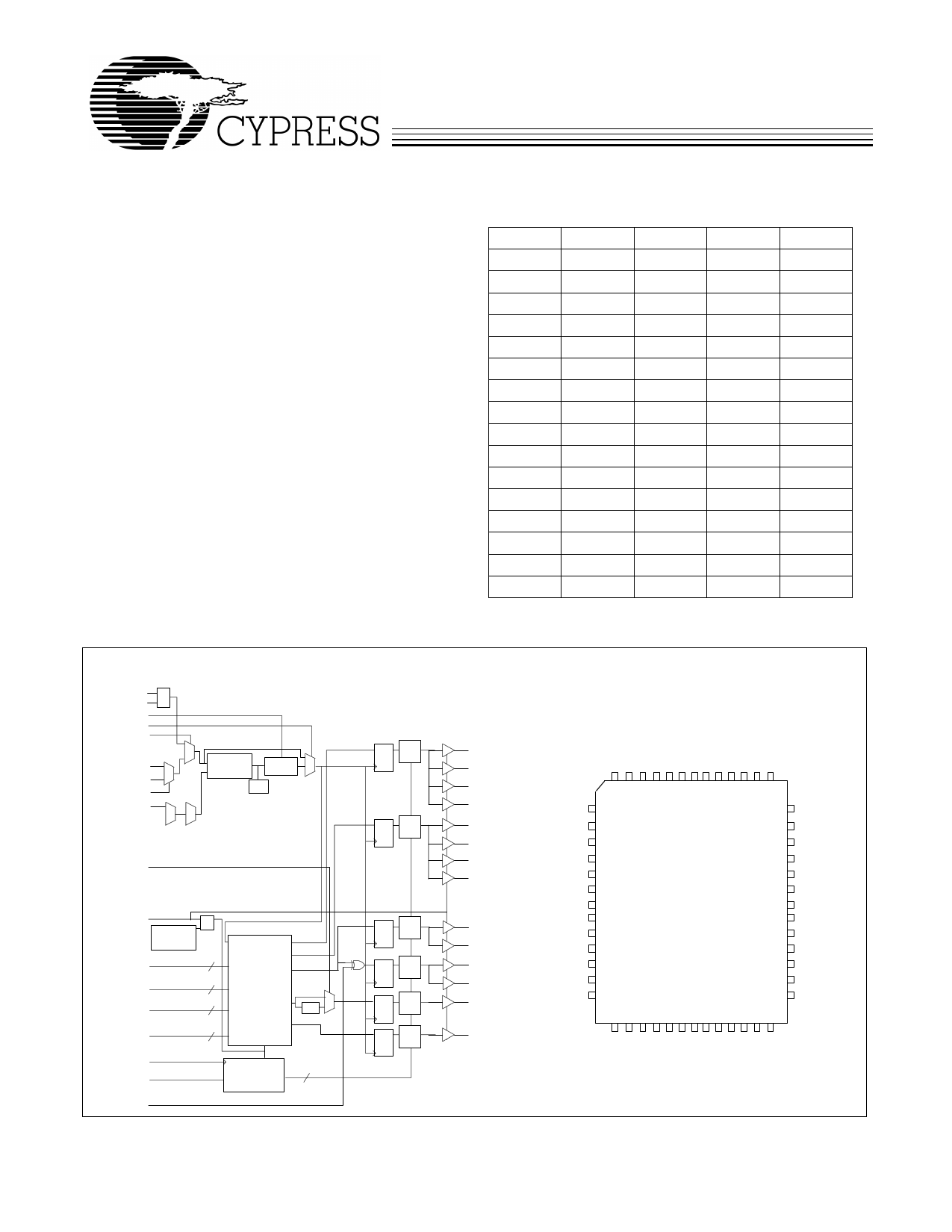

Table 1. Frequency Table[1]

VCO_SEL FB_SEL2 FB_SEL1 FB_SEL0

0000

0001

FVCO

8x

12x

0 0 1 0 16x

0 0 1 1 20x

0 1 0 0 16x

0 1 0 1 24x

0 1 1 0 32x

0 1 1 1 40x

1 0 0 0 4x

1 0 0 1 6x

1 0 1 0 8x

1 0 1 1 10x

1 1 0 0 8x

1 1 0 1 12x

1 1 1 0 16x

1 1 1 1 20x

Note:

1. x = the reference input frequency, 200 MHz < FVCO < 480 MHz.

Block Diagram

XIN

XOUT

VCO_SEL

PLL_EN

REF_SEL

TCLK0

TCLK1

TCLK_SEL

FB_IN

0

1

Phase

Detector

VCO

LPF

0

1

FB_SEL2

DQ

Sync

Frz

DQ

Sync

Frz

MR#/OE

Power-On

Reset

SELA(0,1)

2

SELB(0,1)

SELC(0,1)

2

2

FB_SEL(0,1)

2

/4, /6, /8, /12

/4, /6, /8, /10

/2, /4, /6, /8

/4, /6, /8, /10

Sync Pulse

Data Generator

0

/2 1

SCLK

SDATA

Output Disable

Circuitry

12

INV_CLK

DQ

Sync

Frz

DQ

Sync

Frz

DQ

Sync

Frz

DQ

Sync

Frz

Pin Configuration

QA0

QA1

QA2

QA3

QB0

QB1

QB2

QB3

QC0

QC1

QC2

QC3

FB_OUT

SYNC

VSS

MR#/OE

SCLK

SDATA

FB_SEL2

PLL_EN

REF_SEL

TCLK_SEL

TCLK0

TCLK1

XIN

XOUT

VDD

52 51 50 49 48 47 46 45 44 43 42 41 40

1 39

2 38

3 37

4 36

5 35

6 34

7 Z9972 33

8 32

9 31

10 30

11 29

12 28

13 27

14 15 16 17 18 19 20 21 22 23 24 25 26

VSS

QB0

VDDC

QB1

VSS

QB2

VDDC

QB3

FB_IN

VSS

FB_OUT

VDDC

FB_SEL0

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Document #: 38-07088 Rev. *D

Revised December 21, 2002

1 page

Z9972

Power Management

The individual output enable/freeze control of the Z9972

allows the user to implement unique power management

schemes into the design. The outputs are stopped in the logic

“0” state when the freeze control bits are activated. The serial

input register contains one programmable freeze enable bit for

12 of the 14 output clocks. The QC0 and FB_OUT outputs can

not be frozen with the serial port, this avoids any potential lock

up situation should an error occur in the loading of the serial

data. An output is frozen when a logic “0” is programmed and

enabled when a logic “1” is written. The enabling and freezing

of individual outputs is done in such a manner as to eliminate

the possibility of partial “runt” clocks.

The serial input register is programmed through the SDATA

input by writing a logic “0” start bit followed by 12 NRZ freeze

enable bits. The period of each SDATA bit equals the period of

the free running SCLK signal. The SDATA is sampled on the

rising edge of SCLK.

Start

Bit

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11

D0-D3 are the control bits for QA0-QA3, respectively

D4-D7 are the control bits for QB0-QB3, respectively

D8-D10 are the control bits for QC1-QC3, respectively

D11 is the control bit for SYNC

Figure 2. SDATA Input Register

Document #: 38-07088 Rev. *D

Page 5 of 9

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet IMIZ9972.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IMIZ9972 | 3.3V/ 125-MHz/ Multi-Output Zero Delay Buffer | Cypress Semiconductor |

| IMIZ9972BA | 3.3V/ 125-MHz/ Multi-Output Zero Delay Buffer | Cypress Semiconductor |

| IMIZ9972BAT | 3.3V/ 125-MHz/ Multi-Output Zero Delay Buffer | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |