|

|

PDF KT8554 Data sheet ( Hoja de datos )

| Número de pieza | KT8554 | |

| Descripción | 1 CHIP CODECS | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de KT8554 (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

KT8554B/7B

1 CHIP CODECS

INTRODUCTION

The KT8554B/7B are single-chip PCM encoders and decoders

(PCM CODECs) and PCM line filters. These devices provide

all the functions required to interface a full-duplex voice

telephone circuit with a time-division-multiplex (TDM)

system.

These devices are designed to perform the transmit encoding

and receive decoding as well as the transmit and receive filter-

ing functions in PCM system. They are intended to be used

at the analog termination of a PCM line or trunk.

These devices provide the bandpass filtering of the analog

signals prior to encoding and after decoding. These combina-

tion devices perform the encoding and decoding of voice and

call progress tones as well as the signalling and supervision

information.

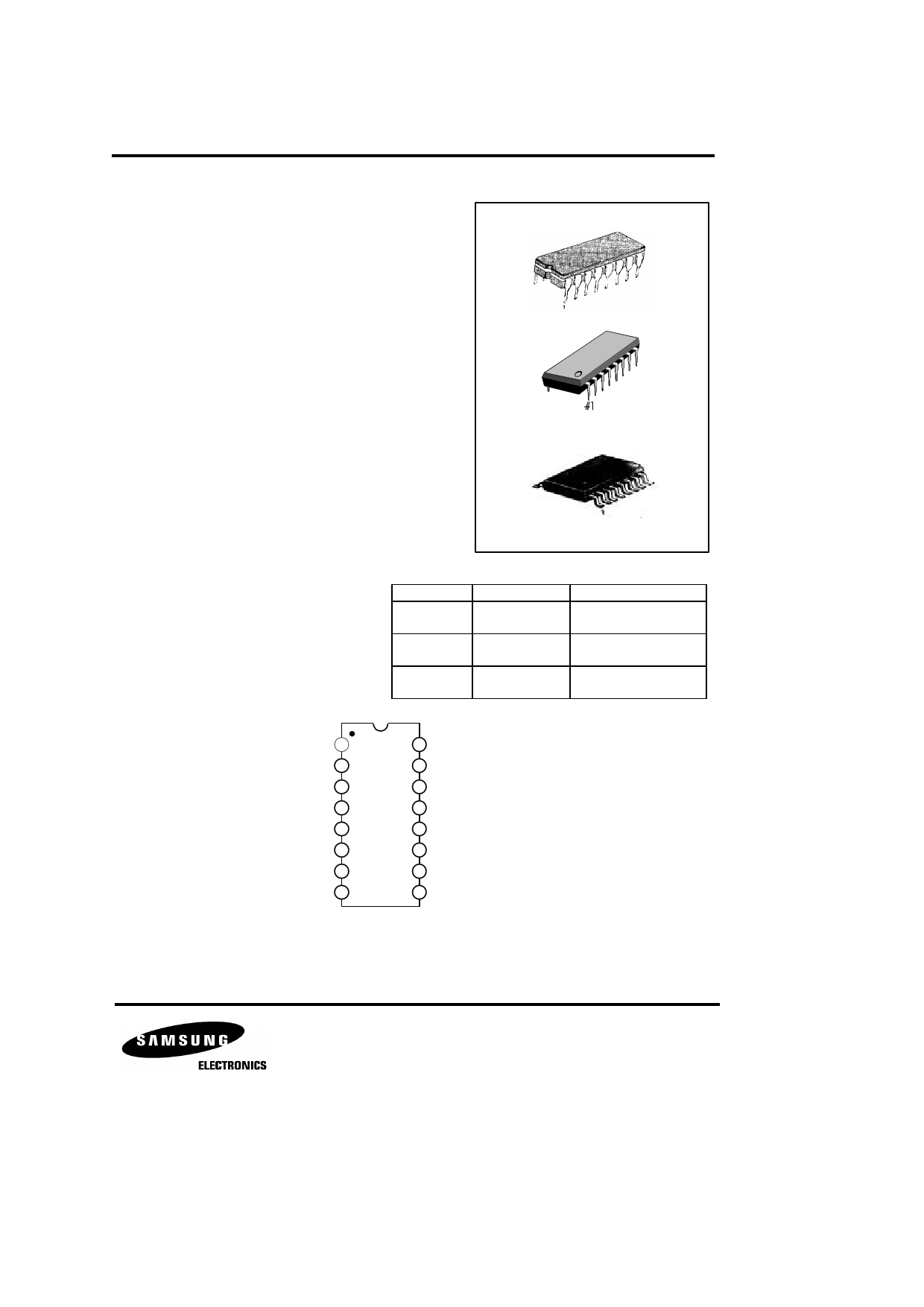

16-CERDIP

16-DIP-

300A

FEATURES

• Complete CODEC and filtering system

• Meets or exceeds AT&T D3/D4 and CCITT

specifications

µ-Law : KT8554B, A-Law : KT8557B

• On-chip auto zero, sample and hold, and precision

voltage references

• Low power dissipation : 60mW (operating)

3mW (standby)

• ± 5V operation

• TTL or CMOS compatible

• Automatic power down

PIN CONFIGURATION

16-SOP-BD300

-SG

ORDERING INFORMATION

Device

Package

Operating Temperature

KT8554BJ

KT8557BJ

16-CERDIP

- 25 ~ 125°C

KT8557BN

KT8554BN

16-DIP-300A

- 25 ~ 70°C

KT8554BD

KT8557BD

16-SOP-BD300

-SG

- 25 ~ 70°C

V BB 1

GNDA 2

VF RO 3

VCC 4

FS R 5

DR 6

BCLK R/CLKSEL 7

MCLK R/PDN 8

16 VF XI+

15 VF XI-

14 GS X

KT8554B/7B 13 TS X

12 FS XS

11 D X

10 BCLK X

9 MCLK X

Fig. 1

1 page

KT8554B/7B

1 CHIP CODECS

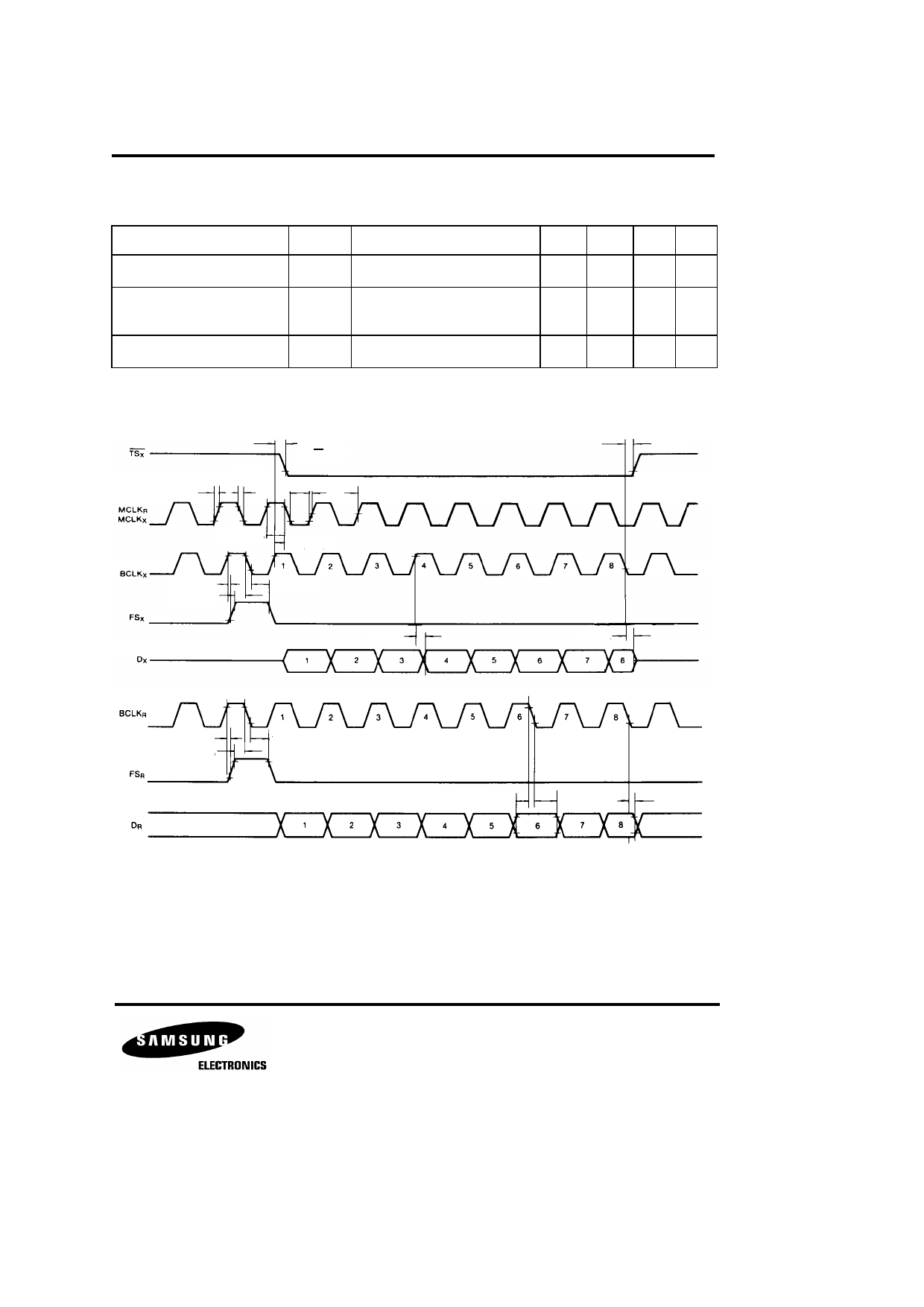

TIMING CHARACTERISTICS (Continued)

Characteristic

Symbol

Test Conditions

Min Typ

Hold Time from BCLKX/R Low

to FSX/R Low

Hold Time from 3rd Period of

Bit Clock Low to Frame Sync

(FSX or FSR)

Minimum Width of the Frame

Sync Pulse (Low Level)

tH (BLFL)

tH (3rd )

tWFL

Short frame sync pulse (1 or 2 bit

clock periods long) (Note 1)

Long frame sync pulse (from 3 to

8 bit clock periods long)

64K bit/s operating mode

100

100

160

Note 1 : For short frame sync timing, FSX and FSR must go high while their respective bit clocks are high.

TIMING DIAGRAM

Max Unit

ns

ns

ns

tR (MCK)

tF (MCK)

tD (TS X L)

tW (MCKL)

tCK

tD (LDD)

tW (MCKH)

tSU (BHMF)

tH (HFS)

tSU (FBLS)

tH (BLFL)

tD (HDV)

tD (LDD)

tH (HFS)

tSU (FBCL)

tH (BLFL)

tSU (DR BL)

Fig. 2. Short Frame Sync Timing

tH (BLDR)

tH (BLDR)

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet KT8554.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KT8554 | 1 CHIP CODECS | Samsung semiconductor |

| KT8554B | 1 CHIP CODECS | Samsung semiconductor |

| KT8555 | TIME SLOT ASSIGNMENT CIRCUIT | Samsung semiconductor |

| KT8555J | TIME SLOT ASSIGNMENT CIRCUIT | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |