|

|

PDF 73K324L-28IH Data sheet ( Hoja de datos )

| Número de pieza | 73K324L-28IH | |

| Descripción | CCITT V.22bis/ V.22/ V.21/ V.23/ Bell 212A Single-Chip Modem | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 73K324L-28IH (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

73K324L

CCITT V.22bis, V.22, V.21, V.23, Bell 212A

Single-Chip Modem

DESCRIPTION

The 73K324L is a highly integrated single-chip

modem IC which provides the functions needed to

design a Quad-mode CCITT and Bell 212A

compatible modem capable of operation over dial-up

lines. The 73K324L adds V.23 capability to the

CCITT modes of TDK Semiconductor Corporation's

73K224 one-chip modem, allowing a one-chip

implementation in designs intended for European

markets which require this added Modulation mode.

The 73K324L offers excellent performance and a

high level of functional integration in a single IC. The

device supports V.22bis, V.22, Bell 212A, V.21, and

V.23 operating modes, allowing both synchronous

and asynchronous operation as defined by the

appropriate standard.

The 73K324L is designed to appear to the Systems

Engineer as a microprocessor peripheral, and will

easily interface with popular one-chip

microcontrollers (80C51 typical) for control of

modem functions through its 8-bit multiplexed

address/data bus. A serial control bus is available

for applications not requiring a parallel interface. An

optional package with only the serial control bus is

also available. Data communications occurs through

a separate serial port.

(continued)

FEATURES

April 2000

• One chip Multi-mode CCITT V.22bis, V.22, V.21,

V.23 and Bell 212A compatible modem data pump

• FSK (75, 300, 1200 bit/s), DPSK (600, 1200 bit/s),

or QAM (2400 bit/s) encoding

• Pin and software compatible with other

TDK Semiconductor Corporation K-Series family

one-chip modems

• Interfaces directly with standard

microprocessors (8048, 80C51 typical)

• Serial and parallel microprocessor bus for

control

• Selectable asynch/synch with internal

buffer/debuffer and scrambler/descrambler

functions

• All synchronous (internal, external, slave) and

Asynchronous Operating modes

• Adaptive equalization for optimum performance

over all lines

• Programmable transmit attenuation (16 dB, 1 dB

steps), and selectable receive boost (+18 dB)

• Call progress, carrier, answer tone, unscrambled

mark, S1, and signal quality monitors

• DTMF, answer, calling, SCT and guard tone

generators

• Test modes available: ALB, DL, RDL; Mark, Space

and Alternating bit pattern generators

• CMOS technology for low power consumption

(100 MW @ 5 V) with power-down mode

(15 mW @ 5V)

• 4-wire full duplex operation in all modes

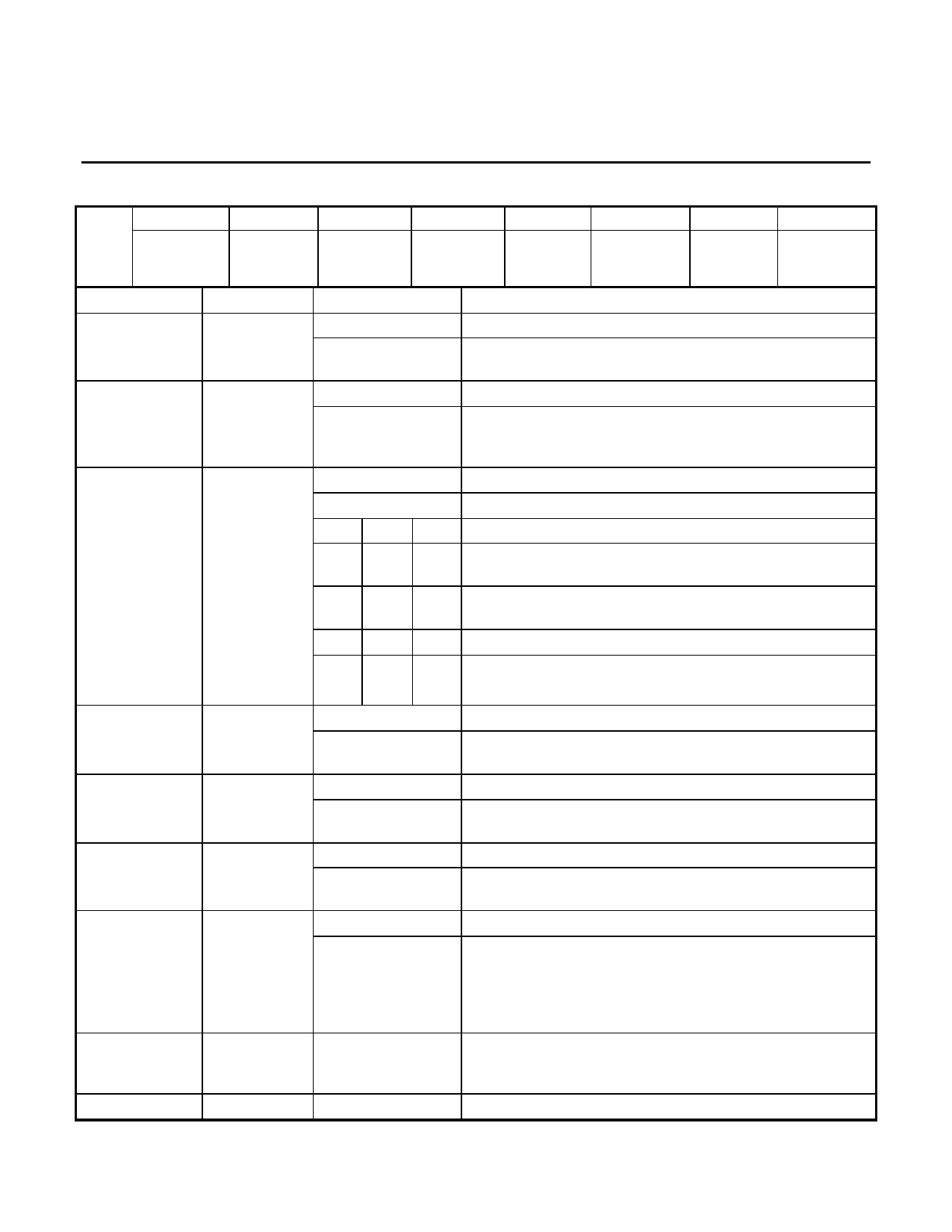

BLOCK DIAGRAM

8 - BIT

mP

BUS

I/F

TXD

RXD

SERIAL

I/F

BUFFER

FSK

MODULATOR

DTMF,

ANSWER,

GUARD &

CALLING

TONE

GENERATOR

SCRAMBLER

DIBIT/

QUADBIT

ENCODER

FIR

PULSE

SHAPER

QAM/

DPSK

MODULATOR

+

EQUALIZER

FILTER

+

ATTEN

FILTER

TXA

DEBUFFER

DE-

SCRAMBLER

DIBIT/

QUADBIT

DECODER

DIGITAL

SIGNAL

PROCESSOR

RECEIVE

FUNCTIONS

FILTER

A/D

AGC

EQUALIZER

FIXED

DEMOD

6 dB

GAIN

BOOST

FILTER

6 dB

GAIN BOOST

FILTER

RXA

TONE DETECTION

1 page

73K324L

CCITT V.22bis, V.22, V.21, V.23, Bell 212A

Single-Chip Modem

RS-232 INTERFACE

NAME

EXCLK

RXCLK

RXD

TXCLK

TXD

TYPE DESCRIPTION

I

O/Tristate

External Clock. This signal is used in synchronous transmission when the external

timing option has been selected. In the External Timing mode the rising edge of

EXCLK is used to strobe synchronous transmit data available on the TXD pin. Also

used for serial control interface.

Receive Clock Tri-statable. The falling edge of this clock output is coincident with

the transitions in the serial received DPSK/QAM data output. The rising edge of

RXCLK can be used to latch the valid output data. RXCLK will be valid as long as

a carrier is present. In V.23 or V.21 mode a clock which is 16 x 1200/75 or 16 x

300 Hz data rate is output, respectively.

O/ Received Data Output. Serial receive data is available on this pin. The data is

Weak always valid on the rising edge of RXCLK when in Synchronous mode. RXD will

Pull-up output constant marks if no carrier is detected.

O/Tristate

Transmit Clock Tri-statable. This signal is used in synchronous DPSK/QAM

transmission to latch serial input data on the TXD pin. Data must be provided so

that valid data is available on the rising edge of the TXCLK. The transmit clock is

derived from different sources depending upon the Synchronization mode

selection. In Internal Mode the clock is generated internally (2400 Hz for QAM,

1200 Hz for DPSK or 600 Hz for half-speed DPSK). In External Mode TXCLK is

phase locked to the EXCLK pin. In Slave Mode TXCLK is phase locked to the

RXCLK pin. TXCLK is always active. In V.23 or V.21 mode the output is a 16 x

1200/75 or 16 x 300 Hz clock, respectively.

I Transmit Data Input. Serial data for transmission is input on this pin. In

Synchronous modes, the data must be valid on the rising edge of the TXCLK

clock. In Asynchronous modes (2400/1200/600 bit/s, or 75/300 baud) no clocking

is necessary. DPSK/QAM data must be +1%, -2.5% or +2.3%, -2.5 % in Extended

Overspeed mode.

ANALOG INTERFACE

RXA

TXA

XTL1

XTL2

I

O

I

I/O

Received modulated analog signal input from the phone line.

Transmit analog output to the phone line.

These pins are for the internal crystal oscillator requiring a 11.0592 MHz Parallel

mode crystal. Two capacitors from these pins to ground are also required for

proper crystal operation. Consult crystal manufacturer for proper values. XTL2 can

also be driven from an external clock.

5

5 Page

73K324L

CCITT V.22bis, V.22, V.21, V.23, Bell 212A

Single-Chip Modem

DETECT REGISTER

DR D7

D6 D5

010 RECEIVE

S1 RECEIVE

LEVEL

PATTERN

DATA

INDICATOR DETECT

D4

UNSCR.

MARK

DETECT

D3

CARRIER

DETECT

D2

SPECIAL

TONE

DETECT

D1

CALL

PROG.

DETECT

D0

SIGNAL

QUALITY

INDICATOR

BIT NO.

D0

D1

D2

NAME

CONDITION

DESCRIPTION

Signal

Quality

Indicator

0 Indicates normal received signal.

1 Indicates low received signal quality (above average error

rate). Interacts with Special Register SQ bits D2, D1.

Call Progress 0 No call progress tone detected.

Detect

1 Indicates presence of call progress tones. The call

progress detection circuitry is activated by energy in the

normal 350 to 620 Hz call progress band.

Special Tone 0 Condition not detected

Detect

1 Condition detected

CR0 D0 TR D0 CR2 D5

1 0 1 2225 Hz ±10 Hz answer tone detected in V.22bis, V.22

modes.

1 1 1 2100 Hz ±21 Hz answer tone detected in V.22bis, V.22

modes.

0 X 0 900 Hz SCT tone detected in V.23 mode.

1 X 0 2100 Hz or 2225 Hz answer tone detected in QAM,

DPSK mode.

D3 Carrier

Detect

0 No carrier detected in the receive channel.

1 Indicated carrier has been detected in the received

channel. Should be time qualified by software.

D4 Unscr. Mark 0 No unscrambled mark being received.

Detect

1 Indicates detection of unscrambled marks in the received

data. Should be time qualified by software.

D5 Receive Data

Continuously outputs the received data stream.

This data is the same as that output on the RXD pin, but

it is not disabled when RXD is tri-stated.

D6 S1 Pattern 0 No S1 pattern being received.

Detect

1 S1 pattern detected. Should be time qualified by

software. S1 is an unscrambled double dibit

(11001100...) sent in DPSK 1200 bit/s mode. Generated

pattern must be properly aligned to transmitter baud clock

to be detected.

D7 Receive

Level

Indicator

0 Received signal level below threshold, (≈ -25 dBm0);can

use receive gain boost (+18 dB)

1 Received signal above threshold.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 73K324L-28IH.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 73K324L-28IH | CCITT V.22bis/ V.22/ V.21/ V.23/ Bell 212A Single-Chip Modem | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |