|

|

PDF IDT7008 Data sheet ( Hoja de datos )

| Número de pieza | IDT7008 | |

| Descripción | HIGH-SPEED 64K x 8 DUAL-PORT STATIC RAM | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT7008 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

HIGH-SPEED

64K x 8 DUAL-PORT

STATIC RAM

IDT7008S/L

Features

x True Dual-Ported memory cells which allow simultaneous

reads of the same memory location

x High-speed access

– Military: 25/35/55ns (max.)

– Industrial: 55ns (max.)

– Commercial: 20/25/35/55ns (max.)

x Low-power operation

– IDT7008S

Active: 750mW (typ.)

Standby: 5mW (typ.)

– IDT7008L

Active: 750mW (typ.)

Standby: 1mW (typ.)

x Dual chip enables allow for depth expansion without

external logic

x IDT7008 easily expands data bus width to 16 bits or

more using the Master/Slave select when cascading more

than one device

x M/S = VIH for BUSY output flag on Master,

M/S = VIL for BUSY input on Slave

x Interrupt Flag

x On-chip port arbitration logic

x Full on-chip hardware support of semaphore signaling

between ports

x Fully asynchronous operation from either port

x TTL-compatible, single 5V (±10%) power supply

x Available in 84-pin PGA, 84-pin PLCC, and a 100-pin TQFP

x Industrial temperature range (–40°C to +85°C) is available

for selected speeds

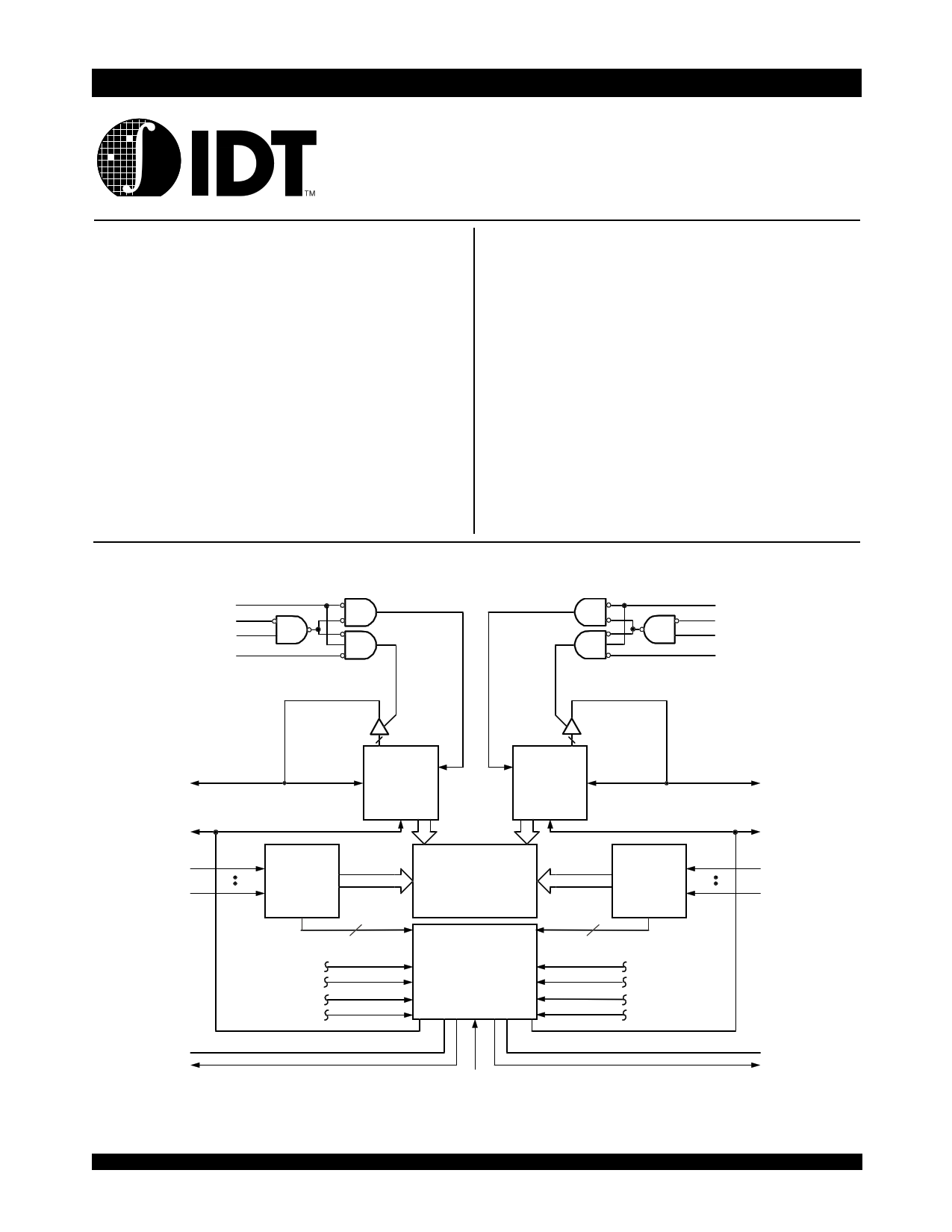

Functional Block Diagram

R/WL

CE0L

CE1L

OEL

R/WR

CE0R

CE1R

OE R

I/O0-7L

I/O

Control

I/O

Control

BUSYL(1,2)

A15L

A0L

Address

Decoder

16

CE0L

CE1L

OEL

R/W L

64Kx8

MEMORY

ARRAY

7008

ARBITRATION

INTERRUPT

SEMAPHORE

LOGIC

16

SEML

INTL(2)

M/S(1)

NOTES:

1. BUSY is an input as a Slave (M/S = VIL) and an output when it is a Master (M/S = VIH).

2. BUSY and INT are non-tri-state totem-pole outputs (push-pull).

©2000 Integrated Device Technology, Inc.

1

Address

Decoder

CE0R

CE1R

OER

R/WR

I/O0-7R

BUSY R(1,2)

A15R

A0R

SEMR

INT

(2)

R

3198 drw 01

MAY 2000

DSC 3198/6

1 page

IDT7008S/L

High-Speed 64K x 8 Dual-Port Static RAM

Truth Table I: Chip Enable(1)

CE CE0

CE1

Military, Industrial and Commercial Temperature Ranges

Mode

VIL VIH Port Selected (TTL Active)

L

< 0.2V

>VCC -0.2V Port Selected (CMOS Active)

VIH X Port Deselected (TTL Inactive)

X

H >VCC -0.2V

VIL Port Deselected (TTL Inactive)

X Port Deselected (CMOS Inactive)

X

<0.2V

Port Deselected (CMOS Inactive)

NOTES:

1. Chip Enable references are shown above with the actual CE0 and CE1 levels, CE is a reference only.

3198 tbl 02

Truth Table II: Non-Contention Read/Write Control

Inputs(1)

Outputs

CE(2) R/W OE SEM

I/O0-7

Mode

H X X H High-Z Deselected: Power-Down

L L X H DATAIN Write to memory

L H L H DATAOUT Read memory

X X H X High-Z Outputs Disabled

NOTES:

1. A0L – A15L ≠ A0R – A15R.

2. Refer to Chip Enable Truth Table.

3198 tbl 03

Truth Table III: Semaphore Read/Write Control(1)

Inputs

Outputs

CE(2) R/W OE SEM

I/O0-7

Mode

H H L L DATAOUT Read Semaphore Flag Data Out

H ↑ X L DATAIN Write I/O0 into Semaphore Flag

LXXL

______ Not Allowed

NOTES:

1. There are eight semaphore flags written to via I/O0 and read from all the I/Os (I/O0-I/O7). These eight semaphore flags are addressed by A0-A2.

2. Refer to Chip Enable Truth Table.

3198 tbl 04

6.542

5 Page

IDT7008S/L

High-Speed 64K x 8 Dual-Port Static RAM

Military, Industrial and Commercial Temperature Ranges

Timing Waveform of Semaphore Read after Write Timing, Either Side(1)

A0-A2

SEM

DATA0

R/W

VALID ADDRESS

tAW

tEW

tWR

tSAA

VALID ADDRESS

tACE

tDW tSOP

DATAIN VALID

tAS tWP

tDH

DATAOUT

VALID(2)

tOH

tSWRD

tAOE

OE tSOP

Write Cycle

Read Cycle

NOTES:

1. CE = VIH for the duration of the above timing (both write and read cycle) (Refer to Chip Enable Truth Table).

2. "DATAOUT VALID" represents all I/O's (I/O0 - I/O15) equal to the semaphore value.

3198 drw 11

Timing Waveform of Semaphore Write Contention(1,3,4)

A0"A"-A2"A"

MATCH

SIDE(2) "A"

R/W"A"

SEM"A"

A0"B"-A2"B"

MATCH

tSPS

SIDE(2) "B"

R/W"B"

SEM"B"

3198 drw 12

NOTES:

1. DOR = DOL = VIL, CEL = CER = VIH (Refer to Chip Enable Truth Table).

2. All timing is the same for left and right ports. Port "A" may be either left or right port. "B" is the opposite from port "A".

3. This parameter is measured from R/W"A" or SEM"A" going HIGH to R/W"B" or SEM"B" going HIGH.

4. If tSPS is not satisfied, the semaphore will fall positively to one side or the other, but there is no guarantee which side will obtain the flag.

61.412

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet IDT7008.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT7005 | HIGH-SPEED 8K x 8 DUAL-PORT STATIC RAM | Integrated Device Technology |

| IDT7006 | HIGH-SPEED 16K x 8 DUAL-PORT STATIC RAM | Integrated Device Technology |

| IDT7007 | HIGH-SPEED 32K x 8 DUAL-PORT STATIC RAM | Integrated Device Technology |

| IDT7008 | HIGH-SPEED 64K x 8 DUAL-PORT STATIC RAM | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |