|

|

PDF TC94A09F Data sheet ( Hoja de datos )

| Número de pieza | TC94A09F | |

| Descripción | Single-Chip CD Processor with Built-it Controller | |

| Fabricantes | Toshiba | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TC94A09F (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC94A09F

Single-Chip CD Processor with Built-in Controller

TC94A09F

The TC94A09F is a single-chip CD processor for digital servo.

The IC has a built-in 4-bit microcontroller.

The controller features an LCD/LED driver, 4-channel 6-bit AD

converter, 2/3-line serial interface, buzzer, interrupt function, and

8-bit timer/counter. The CPU can select one of three crystal

oscillator operating clocks (16.9344 MHz, 4.5 MHz, and 75 kHz),

facilitating interface with the CD processor.

The CD processor incorporates sync separation protection and

interpolation, EFM decoder, error correction, digital equalizer for

servo, and servo controller. The CD processor also incorporates a

1-bit DA converter. In combination with a RF amp TA2153FN

Weight: 1.6 g (typ.)

and TA2109F, the TC94A09F can very simply configure an adjustment-free CD player.

Thus, the IC is suitable for CD systems for automobiles and radio-cassette players.

Features

· Single-chip CD processor with built-in CMOS LCD/LED driver and 4-bit microcontroller

· Operating voltage

At CD on: VDD = 4.5 to 5.5 V (typ. 5.0 V)

At CD off: VDD = 3.0 to 5.5 V (only CPU on)

· Current dissipation

At CD on: IDD = 50 mA (typ.)

At CD off: IDD = 2 mA (with 4.5 MHz crystal oscillator, only CPU on)

At CD off: IDD = 0.3 mA (with 75 kHz crystal oscillator, only CPU on)

· Operating temperature range Ta = -40 to 85°C

· Package

QFP100-P-1420-0.65A (0.65 mm pitch, 2.7 mm thick)

· One-time PROM version

TC94AP09F

1 2001-10-15

1 page

TC94A09F

Pin Descriptions

Pin

Number

Symbol

Pin Name

Function and Operation

Remarks

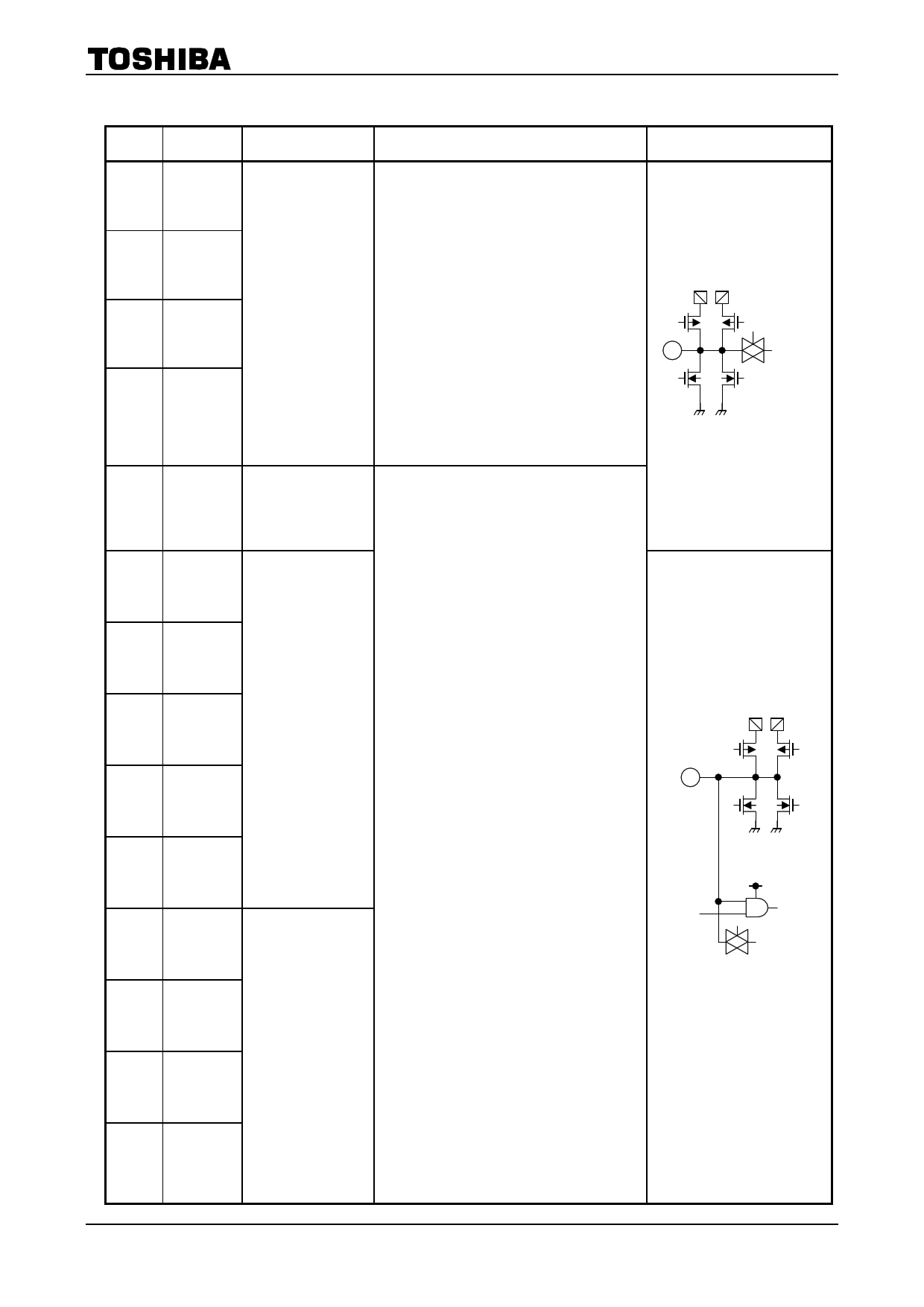

97 COM1/OT1

Common signal output pins for the LCD panel.

Those pins configure matrix with S1 to S18 and

display up to 72 segments.

The LCD can be driven by the 1/2 or 1/3 bias

method. When the 1/2 bias method is set three

98 COM2/OT2

levels, MVDD, 1/2MVDD, and GND, are output

at 2-ms intervals. When the 1/3 bias method is

set four levels, MVDD, 1/3MVDD, 2/3MVDD, and

LCD common output

GND, are output at a 62.5 Hz cycle (when

either the 4.5 MHz or 75 kHz crystal oscillator is

MVDD

/output port

used).

99 COM3/OT3

After system reset or clock stop execution is

released, the non-selected waveform (bias

voltage) is output. The DISP OFF bit is set to 0

and the common signal is output.

MVDD

Bias

voltage

100 COM4/OT4

These pins can be switched to an output port

(Note1) or LED driver pins by program. They

are usually used for digit output to drive the

LEDs.

Segment signal output pins for the LCD panel.

1~9

S1/OT4

~

S9/OT13

Those pins configure a matrix with COM1 to

LCD segment output COM4 and display up to 72 segments.

/output port

When the 1/2 bias method is set two levels,

10

S10/OT14

/ZDET

MVDD and GND, are output. When the 1/3 bias

method is set four levels, MVDD, 1/3MVDD,

2/3MVDD, and GND, are output.

The S1 to S14 pins can be switched to an

output port (Note1) by program. Port 8 and S15

to S18 pins can be switched pin by pin to an I/O

port and segment output pins. When the pins

11

S11/OT15

/CLCK

are set to an I/O port, output is N-channel open

drain.

The S10 to S14 and P8-0 to P8-3 pins can be

switched to CD signal input/output pins by

12

S12/OT16

/DATA

LCD segment output program. Setting the CD10 bit to 1 switches the

/output port

pins to the LRCK, BCK, and AOUT pins as the

/CD signal

CD pins in batches. The other pins can be

individually switched according to the

S14/S15/S16 segment data.

MVDD

MVDD

13

S13/OT17

/SFSY

・CLCK Inputs/outputs sub code P to W data

reading clock.

・DATA Outputs sub code P to W data.

・SFSY Outputs frame sync signal for

playback.

14

S14/OT18

/LRCK

・LRCK Outputs channel clock (44.1 kHz).

When L channel, outputs Low. When

MVDD

R channel, outputs High. The polarity

can be inverted by command.

Input

15

P8-0/S15

/BCK

・BCK Outputs bit clock (1.4112 MHz).

・AOUT Outputs audio data.

・MBOV Outputs buffer-memory-overflow

signal. When buffer memory

instruction

Bias

potential

overflows, outputs H.

・IPF Outputs interpolation pointing flag. If

16

P8-1/S16

/AOUT

AOUT output is C2 error

detection/correction, outputs High to

indicate correction is impossible.

I/O port

・ZDET Outputs 1-bit DAC zero detection flag.

/LCD segment output

17

P8-2/S17

/MBOV

/CD signal

Pins set as an output port are used for segment

output for the LED driver. The output port can

increment OT1 to OT18 by instruction,

facilitating access to data in external RAM and

ROM.

18

P8-3/S18

/IPF

(Note1) After a system reset, pins also used as

output ports are set to LCD output;

pins also used as I/O ports are set to

I/O port input.

5 2001-10-15

5 Page

Pin

Number

Symbol

91 HOLD

92 INTR

Pin Name

Function and Operation

Hold mode control

input

External interrupt

input

Input pin used to request or release hold state.

Normally, the pin is used for inputting the CD

mode selection signal or battery detection

signal.

Halt states are Clock Stop mode (crystal

oscillator stops oscillation) and Wait mode

(CPU stops). The modes are entered using the

CKSTP and WAIT instructions.

By program, Clock Stop mode can be entered

by detection of Low level on the HOLD pin or

by forced execution. Clock Stop mode can be

released by detection of High level on the

HOLD pin or change in the HOLD pin input.

Executing the CKSTP instruction stops the

clock generator and the CPU, entering memory

backup state. During memory backup state,

current dissipation becomes low (1 mA or

below). The display output and CMOS output

port automatically become Low level. The

N-channel open drain output becomes off.

Regardless of the HOLD pin input state, Wait

mode is executed and current dissipation

becomes low. Crystal oscillator only on or CPU

operation suspended can be programmed.

When the crystal oscillator only is on, all

displays are at Low level. The other pins are in

hold state. When CPU operation is suspended,

all states are held except that the CPU is

suspended. Wait mode is released by a change

of the HOLD pin input.

(Note) For Backup mode, use the oscillator

connected to the MXO and MXI pins.

Turn off the VDD pin (power supply for

CD), and enter Backup mode.

External interrupt input pin.

When interrupts are enabled and a pulse of

1.11 to 3.33 ms or more (13.3 to 40 ms when the

75 kHz clock is used) is input to this pin, an

interrupt is generated and the program jumps to

address 1. Input logic and rising/falling edge

can be individually selected for interrupt inputs.

The internal 8-bit timer clock can be selected

for interrupt inputs. Interrupts can be generated

(address 3) by pulse count or the count value.

Interrupt inputs are Schmidt inputs. The pin can

be used as an input port for inputs such as

remote control signals.

TC94A09F

Remarks

MVDD

11 2001-10-15

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet TC94A09F.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TC94A09F | Single-Chip CD Processor with Built-it Controller | Toshiba |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |