|

|

PDF DS2405 Data sheet ( Hoja de datos )

| Número de pieza | DS2405 | |

| Descripción | Addressable Switch | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS2405 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

www.maxim-ic.com

FEATURES

Open-drain PIO pin is controlled by

matching 64-bit, laser-engraved registration

number associated with each device

Logic level of open drain output can be

determined over 1-Wire® bus for closed-loop

control

PIO pin sink capability is greater than 4mA

at 0.4V

Multiple DS2405s can be identified on a

common 1-Wire bus and be turned on or off

independent of other devices on the bus

Unique, factory-lasered and tested 64-bit

registration number (8-bit family code +48-

bit serial number +8-bit CRC tester) assures

absolute identity because no two parts are

alike

Built-in multidrop controller ensures

compatibility with other MicroLAN products

Reduces control, address, data, and power to

a single data pin

Directly connects to a single port pin of a

microprocessor and communicates at up to

16.3kbits/s

8-bit family code specifies DS2405

communications requirements to reader

8-bit cyclic redundancy check ensures error-

free selection

Zero standby power required

Low cost TO-92, SOT-223, or 6-pin TSOC

surface mount package

1-Wire communication operates over a wide

voltage range of 2.8V to 6.0V from -40°C to

+85°C

DS2405

Addressable Switch

PIN ASSIGNMENT

TO-92

DS2405

TSOC PACKAGE

GND

DATA

PIO

NC

NC

NC

TOP VIEW

3.7 X 4.0 X 1.5

123

123

BOTTOM VIEW

See Mech.

Drawings Section

TOP VIEW

NOTE: The leads of TO-92 packages on tape-and-reel are

formed to approximately 100 mils (2.54 mm) spacing. For

details refer to drawing 56-G0006-003.

PIN DESCRIPTION TSOC

Pin 1 - Ground

Pin 1 - Ground

Pin 2 - Data

Pin 2 - Data

Pin 3 - PIO

Pin 3 - PIO

Pin 4 - Ground

Pin 4-6 -No Connect

1-Wire is a registered trademark of Dallas Semiconductor.

1 of 15

071107

1 page

DS2405

ROM FUNCTION COMMANDS

Once the bus master has detected a presence, it can issue one of five ROM function commands. All ROM

function commands are 8 bits long. A list of these commands follows (refer to flowchart in Figure 4).

Read ROM [33h]

This command allows the bus master to read the DS2405’s 8-bit family code, unique 48-bit serial

number, and 8-bit CRC. This command can be used only if there is a single DS2405 on the bus. If more

than one slave is present on the bus, a data collision will occur when all slaves try to transmit at the same

time (open drain will produce a wired-AND result).

Match ROM [55h]

The Match ROM command, followed by a 64-bit ROM sequence, allows the bus master to address a

specific device on a multidrop bus. All devices that do not match the 64-bit ROM sequence will wait for a

Reset Pulse. The DS2405 that exactly matches the 64-bit ROM sequence will toggle the state of its PIO

pin after the 64th bit of the match is entered. If the open drain N-channel device was off, it will be turned

on and vice versa. After the last bit of the ROM sequence is received from the bus master and the PIO pin

of the selected DS2405 has toggled, additional read time slots issued by the bus master will cause the

DS2405 to output the logic state of its PIO pin onto the 1-Wire bus. If the pulldown is on and the PIO pin

is a logical 0, the DS2405 will respond with read-0 time slots. If the pulldown is off and the PIO pin is a

logical 1 (external pullup is required), the DS2405 will respond with read-1 time slot. Each additional

read time slot issued by the bus master will continue to indicate the state of the PIO pin until a Reset

Pulse is received from the bus master.

Search ROM [F0h]

When a system is initially interrogated, the bus master may not know the number of devices on the 1-

Wire bus or their 64-bit ROM codes. The Search ROM command allows the bus master to use a process

of elimination to identify the 64-bit ROM codes of all slave devices on the bus. This process of

elimination involves repeated application of a simple three-step procedure where the bus master starts by

reading a bit position in the 64-bit ROM, followed by reading the complement of that bit position, and

finally writing to all the devices still involved in the search the desired logic value for that bit position. An

example is shown below and a flowchart for the search algorithm can be found in the “Book of DS19xx

iButton Standards.”

Four devices are connected to the 1-Wire bus. Their binary ROM contents are listed below:

device 1: xxxxxx10101100

device 2: xxxxxx01010101

device 3: xxxxxx10101111

device 4: xxxxxx10001000

The x’s represent the higher remaining bits. Shown are the lowest 8 bits of the ROM contents. The least

significant bit is to the right in this representation. The search process runs as follows:

1. The master begins the initialization sequence by issuing a Reset Pulse. The devices respond by issuing

Presence Pulses.

2. The master will then issue the Search ROM command on the 1-Wire bus.

5 of 15

5 Page

DS2405

Skip ROM [CCh]

The complete 1-Wire protocol for all Dallas Semiconductor iButtons contains a Skip ROM command.

Since the DS2405 contains only the 64-bit ROM with no additional data fields, the Skip ROM is not

applicable and will cause no further activity on the 1-Wire bus if executed. The DS2405 does not interfere

with other 1-Wire parts on a multidrop bus that do respond to a Skip ROM (for example, a DS2405 and

DS1994 on the same bus).

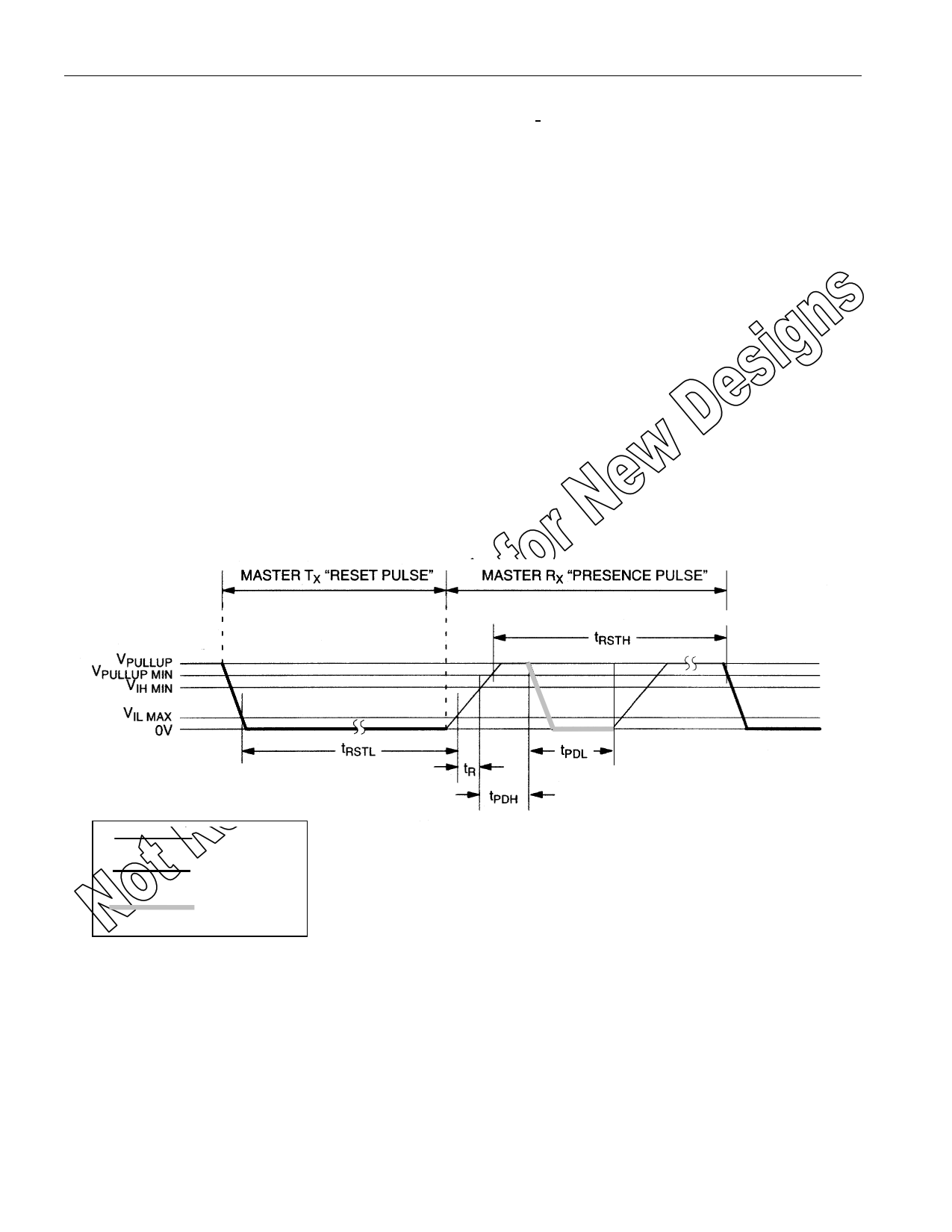

1-WIRE SIGNALING

The DS2405 requires strict protocols to ensure data integrity. The protocol consists of four types of

signaling on one line: reset sequence with Reset Pulse and Presence Pulse, write 0, write 1 and read data.

All these signals except Presence Pulse are initiated by the bus master.

The initialization sequence required to begin any communication with the DS2405 is shown in Figure 5.

A Reset Pulse followed by a Presence Pulse indicates the DS2405 is ready to send or receive data given

the correct ROM command.

The bus master transmits (TX) a Reset Pulse (tRSTL, minimum 480μs). The bus master then releases the

line and goes into receive mode (RX). The 1-Wire bus is pulled to a high state via the 5kΩ pullup resistor.

After detecting the rising edge on the data pin, the DS2405 waits (tPDH, 15-60μs) and then transmits the

Presence Pulse (tPDL, 60-240μs).

INITIALIZATION PROCEDURE “RESET AND PRESENCE PULSES” Figure 5

RESISTOR

MASTER

DS2405

480μs ≤ tRSTL < ∞*

480μs ≤ tRSTH < ∞ (includes recovery time)

15μs ≤ tPDH < 60μs

60μs ≤ tPDL < 240μs

∗ In order not to mask interrupt signaling by other devices on the 1-Wire bus, tRSTL + tR should always

be less than 960μs.

11 of 15

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet DS2405.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS2401 | Silicon Serial Number | Dallas Semiconducotr |

| DS2401 | Silicon Serial Number | Maxim Integrated |

| DS2404 | EconoRAM Time Chip | Dallas Semiconducotr |

| DS2404S-C01 | Dual Port Memory Plus Time | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |