|

|

PDF DS2176N Data sheet ( Hoja de datos )

| Número de pieza | DS2176N | |

| Descripción | T1 Receive Buffer | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS2176N (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

www.dalsemi.com

FEATURES

§ Synchronizes loop–timed and system–timed

T1 data streams

§ Two–frame buffer depth; slips occur on frame

boundaries

§ Output indicates when slip occurs

§ Buffer may be recentered externally

§ Ideal for 1.544 to 2.048 MHz rate conversion

§ Interfaces to parallel or serial backplanes

§ Extracts and buffers robbed–bit signaling

§ Inhibits signaling updates during alarm or slip

conditions

§ Integration feature “debounces” signaling

§ Slip–compensated output indicates when

signaling updates occur

§ Compatible with DS2180A T1 Transceiver

§ Surface mount package available, designated

DS2176Q

§ Industrial temperature range of –40°C to

+85°C available, designated DS2176N

DS2176

T1 Receive Buffer

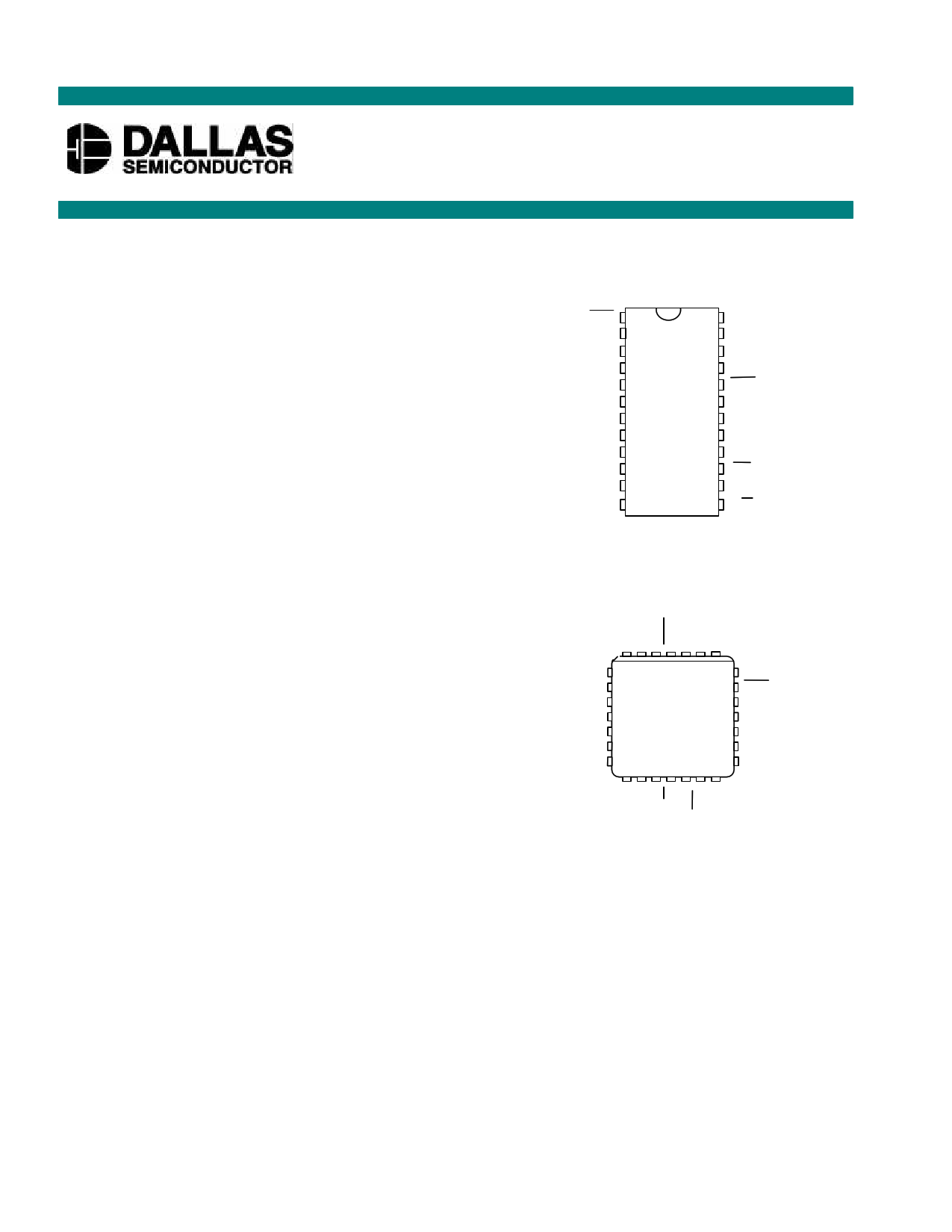

PIN ASSIGNMENT

SIGH

RMSYN

RCLK

RSER

A

B

C

D

SCHCLK

SM0

SM1

VSS

1

2

3

4

5

6

7

8

9

10

11

12

24 VDD

23 SCKLSEL

22 SYCLK

21 SSER

20 SLIP

19 SBIT8

18 SMSYNC

17 SIGFRZ

16 SFSYNC

15 ALN

14 FMS

13 S/P

24-PIN 300 MIL DIP

A

B

NC

NC

C

D

SCHCLK

4 3 2 1 28 27 26

5

6

7

8

9

10

11

12 13 14 15 16 17 18

25

24

23

22

21

20

19

SSER

SLIP

SBIT8

NC

NC

SMSYNC

SIGFRZ

28-PIN PLCC

DESCRIPTION

The DS2176 is a low–power CMOS device specifically designed for synchronizing receive side loop–

timed T–carrier data streams with system side timing. The device has several flexible operating modes

which simplify interfacing incoming data to parallel and serial TDM backplanes. The device extracts,

buffers and integrates ABCD signaling; signaling updates are prohibited during alarm or slip conditions.

The buffer replaces extensive hardware in existing applications with one “skinny” 24–lead package.

Application areas include digital trunks, drop and insert equipment, transcoders, digital cross–connects

(DACS), private network equipment and PABX–to–computer interfaces such as DMI and CPI.

1 of 15

091599

1 page

DS2176

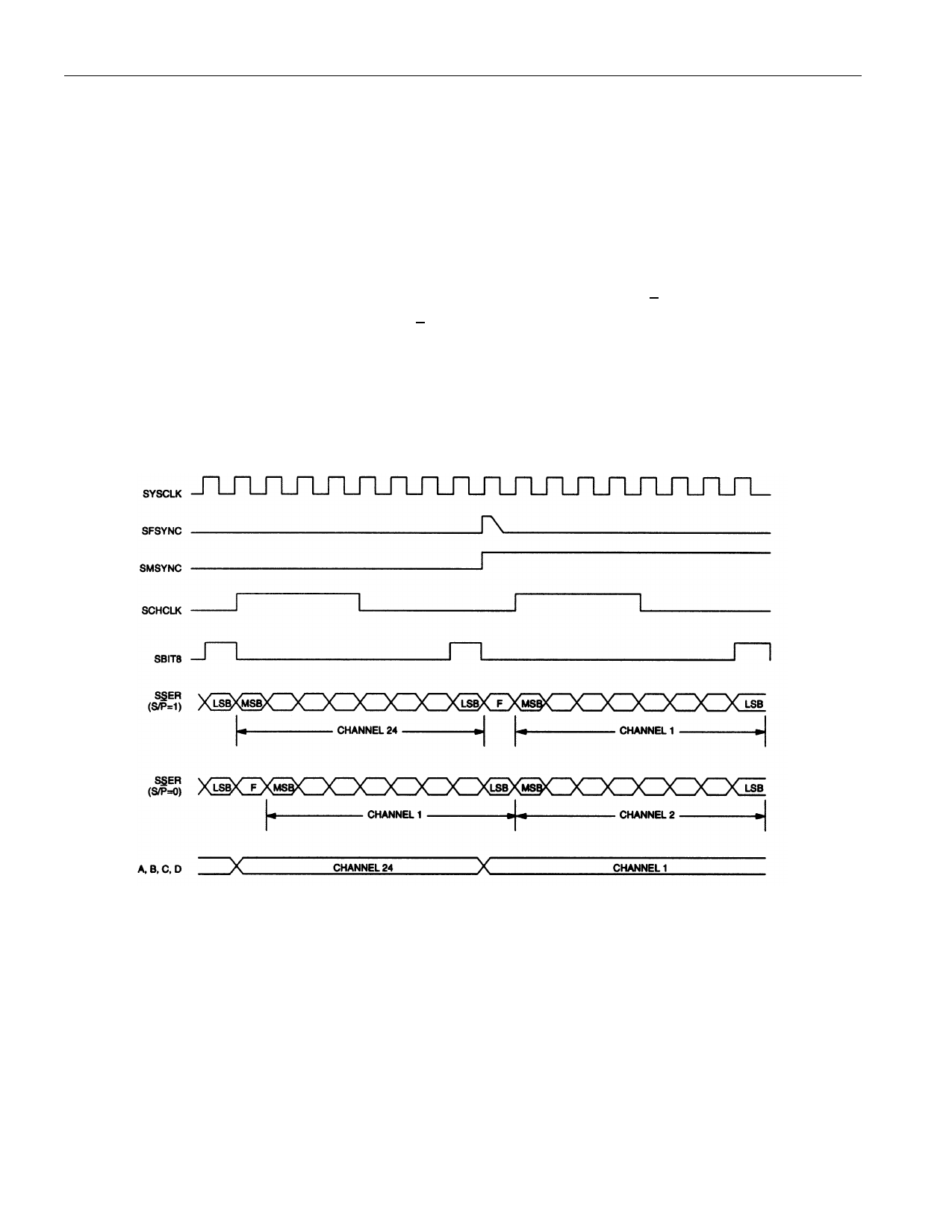

passed through the receive buffer and presented at SSER immediately after the rising edge of the system

side frame sync. The F–bit is dropped in 2.048 MHz applications and the MSB of channel 1 appears at

SSER one bit period after a rising edge at SFSYNC. SSER is forced to 1 in all channels greater than 24.

See Figures 3 and 4.

In 2.048 MHz applications (SCLKSEL=1), the PCM buffer control logic establishes slip criteria different

from that used in 1.544 MHz applications to compensate for the faster system-side read frequency.

PARALLEL COMPATIBILITY

The DS2176 is compatible with parallel and serial back-planes. Channel 1 data appears at SSER after a

rising edge at SFSYNC as shown in Figures 3 and 4 (serial applications, S/ P =1). The device utilizes a

look–ahead circuit in parallel applications (S/ P =0). Data is output 8 clocks earlier, allowing the user to

convert parallel data eternally.

SYSTEM MULTIFRAME BOUNDARY TIMING (SYSCLK = 1.544 MHz) Figure 3

5 of 15

5 Page

DS2176

AC ELECTRICAL CHARACTERISTICS

(0°C to 70°C; VDD =5V ± 10%)

PARAMETERS

RCLK Period

SYMBOL

tRCLK

MIN

250

TYP

648

MAX

UNITS

ns

NOTES

RCLK, SYSCLK Rise

and Fall Times

RCLK Pulse Width

SYSCLK Pulse Width

SYSCLK Period

tR,tF

tRWH,

tRWL

tSWH,

tSWL

tSYSCLK

125

100

200

324

244

488

20

ns

ns

ns

ns

RMSYNC Setup to

RCLK Falling

tSC 20

tRWH-5

ns

SFSYNC Setup to

SYSCLK Falling

tSC 20

tSWH-5

ns

RMSYNC, SFSYNC,

SIGH , ALN Pulse Width

tPW

50

ns ns

RSER Setup to RCLK

Falling

tSD

50

ns

RSER Hold from RCLK

Falling

tHD

50

ns

Propagation Delay

SYSCLK to SSER,

tPVD

100 ns

A,B,C,D

Propagation Delay

SYSCLK to SMSYNC

tPSS

75 ns

High

Propagation Delay

SYSCLK or RCLK to

tPS

100 ns

SLIP Low

Propagation Delay

SYSCLK to SIGFRZ

tPSF

75 ns

Low/High

ALN , SIGH Setup to

SFSYNC Rising

tSR 500

ns

NOTES:

1. Measured at VIH =2.0V, VIL =0.8V, and 10 ns maximum rise and fall times.

2. Output load capacitance = 100 pF.

11 of 15

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet DS2176N.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS2176 | T1 Receive Buffer | Dallas Semiconducotr |

| DS2176N | T1 Receive Buffer | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |