|

|

PDF ACS20MS Data sheet ( Hoja de datos )

| Número de pieza | ACS20MS | |

| Descripción | Radiation Hardened Dual 4-Input NAND Gate | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ACS20MS (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

ACS20MS

April 1995

Radiation Hardened

Dual 4-Input NAND Gate

Features

• 1.25 Micron Radiation Hardened SOS CMOS

• Total Dose 300K RAD (Si)

Pinouts

14 LEAD CERAMIC DUAL-IN-LINE

MIL-STD-1835 DESIGNATOR, CDIP2-T14, LEAD FINISH C

TOP VIEW

• Single Event Upset (SEU) Immunity

<1 x 10-10 Errors/Bit-Day (Typ)

• SEU LET Threshold >80 MEV-cm2/mg

• Dose Rate Upset >1011 RAD (Si)/s, 20ns Pulse

• Latch-Up Free Under Any Conditions

• Military Temperature Range: -55oC to +125oC

• Significant Power Reduction Compared to ALSTTL Logic

• DC Operating Voltage Range: 4.5V to 5.5V

A1 1

B1 2

NC 3

C1 4

D1 5

Y1 6

GND 7

14 VCC

13 D2

12 C2

11 NC

10 B2

9 A2

8 Y2

• Input Logic Levels

- VIL = 30% of VCC Max

- VIH = 70% of VCC Min

• Input Current ≤1µA at VOL, VOH

Description

The Intersil ACS20MS is a radiation hardened dual 4-input

NAND gate. A low on any input forces the output to a high logic

state.

The ACS20MS utilizes advanced CMOS/SOS technology to

achieve high-speed operation. This device is a member of the

radiation hardened, high-speed, CMOS/SOS Logic Family.

14 LEAD CERAMIC FLATPACK

MIL-STD-1835 DESIGNATOR, CDFP3-F14, LEAD FINISH C

TOP VIEW

A1

B1

NC

C1

D1

Y1

GND

1 14

2 13

3 12

4 11

5 10

69

78

VCC

D2

C2

NC

B2

A2

Y2

Ordering Information

PART NUMBER

ACS20DMSR

ACS20KMSR

ACS20D/Sample

ACS20K/Sample

ACS20HMSR

TEMPERATURE RANGE

-55oC to +125oC

-55oC to +125oC

+25oC

+25oC

+25oC

SCREENING LEVEL

Intersil Class S Equivalent

Intersil Class S Equivalent

Sample

Sample

Die

PACKAGE

14 Lead SBDIP

14 Lead Ceramic Flatpack

14 Lead SBDIP

14 Lead Ceramic Flatpack

Die

Truth Table

INPUTS

OUTPUT

An Bn Cn Dn

Yn

LXXX

H

XLXX

H

XXLX

H

XXXL

H

HHHH

L

NOTE: L = Logic Level Low, H = Logic level High, X = Don’t Care

Functional Diagram

(1, 9)

An

Bn

(2, 10)

(4, 12)

Cn

Dn

(5, 13)

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

1

(6, 8)

Yn

Spec Number 518815

File Number 3616

1 page

Specifications ACS20MS

Intersil - Space Products MS Screening

Wafer Lot Acceptance (All Lots) Method 5007 (Includes SEM)

Radiation Verification (Each Wafer) Method 1019,

4 Samples/Wafer, 0 Rejects

100% Nondestructive Bond Pull Method 2023

100% Internal Visual Inspection Method 2010

100% Temperature Cycling Method 1010 Condition C

(-65o to +150oC)

100% Constant Acceleration

100% PIND Testing

100% External Visual Inspection

100% Serialization

100% Initial Electrical Test

100% Static Burn-In 1 Method 1015, 24 Hours at +125oC Min

100% Interim Electrical Test 1 (Note 1)

100% Static Burn-In 2 Method 1015, 24 Hours at +125oC Min

100% Interim Electrical Test 2 (Note 1)

100% Dynamic Burn-In Method 1015, 240 Hours at +125oC

or 180 Hours at +135oC

100% Interim Electrical Test 3 (Note 1)

100% Final Electrical Test

100% Fine and Gross Seal Method 1014

100% Radiographics Method 2012 (2 Views)

100% External Visual Method 2009

Group A (All Tests) Method 5005 (Class S)

Group B (Optional) Method 5005 (Class S) (Note 2)

Group D (Optional) Method 5005 (Class S) (Note 2)

CSI and/or GSI (Optional) (Note 2)

Data Package Generation (Note 3)

NOTES:

1. Failures from interim electrical tests 1 and 2 are combined for determining PDA (PDA = 5% for subgroups 1, 7, 9 and delta failures com-

bined, PDA = 3% for subgroup 7 failures). Interim electrical tests 3 PDA (PDA = 5% for subgroups 1, 7, 9 and delta failures combined,

PDA = 3% for subgroup 7 failures).

2. These steps are optional, and should be listed on the purchase order if required.

3. Data Package Contents:

Cover Sheet (P.O. Number, Customer Number, Lot Date Code, Intersil Number, Lot Number, Quantity).

Certificate of Conformance (as found on shipper).

Lot Serial Number Sheet (Good Unit(s) Serial Number and Lot Number).

Variables Data (All Read, Record, and delta operations).

Group A Attributes Data Summary.

Wafer Lot Acceptance Report (Method 5007) to include reproductions of SEM photos. NOTE: SEM photos to include percent of step coverage.

X-Ray Report and Film, including penetrometer measurements.

GAMMA Radiation Report with initial shipment of devices from the same wafer lot; containing a Cover Page, Disposition, RAD Dose,

Lot Number, Test Package, Spec Number(s), Test Equipment, etc. Irradiation Read and Record data will be on file at Intersil.

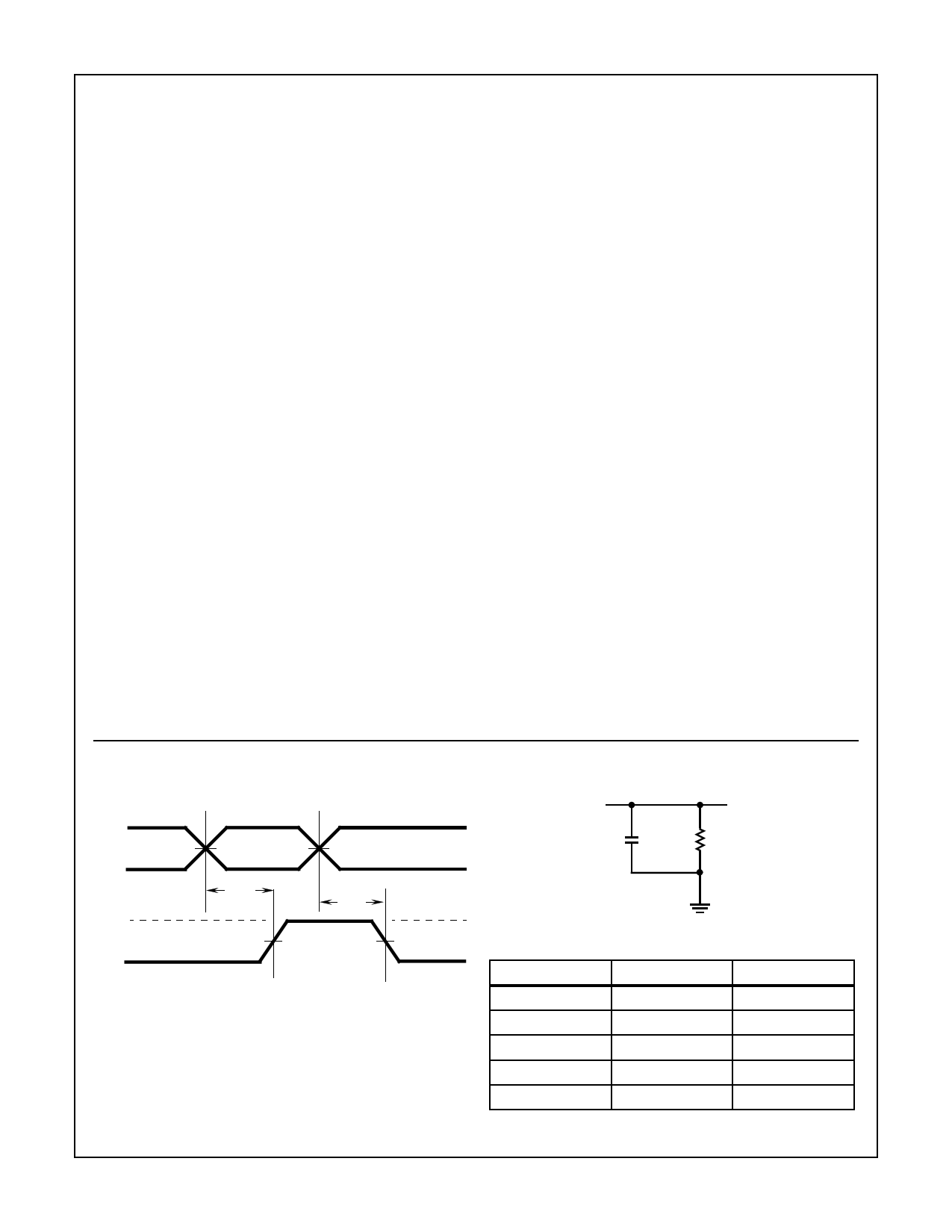

Propagation Delay Timing Diagram and Load Circuit

VIH

VSS

VOH

VOL

VS INPUT

TPLH

VS

TPHL

OUTPUT

DUT

CL

50pF

TEST

POINT

RL

500Ω

AC VOLTAGE LEVELS

PARAMETER

ACS

VCC

4.50

VIH 4.50

VS 2.25

VIL 0

GND

0

UNITS

V

V

V

V

V

Spec Number 518815

5

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet ACS20MS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ACS20MS | Radiation Hardened Dual 4-Input NAND Gate | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |