|

|

PDF CAT93C66 Data sheet ( Hoja de datos )

| Número de pieza | CAT93C66 | |

| Descripción | 1K/2K/2K/4K/16K-Bit Microwire Serial E2PROM | |

| Fabricantes | Catalyst Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CAT93C66 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

CAT93C46/56/57/66/86

1K/2K/2K/4K/16K-Bit Microwire Serial E2PROM

FEATURES

s High Speed Operation:

– 93C46/56/57/66: 1MHz

– 93C86: 3MHz

s Low Power CMOS Technology

s 1.8 to 6.0 Volt Operation

s Selectable x8 or x16 Memory Organization

s Self-Timed Write Cycle with Auto-Clear

s Hardware and Software Write Protection

s Power-Up Inadvertant Write Protection

s 1,000,000 Program/Erase Cycles

s 100 Year Data Retention

s Commercial, Industrial and Automotive

Temperature Ranges

s Sequential Read (except 93C46)

s Program Enable (PE) Pin (93C86 only)

DESCRIPTION

The CAT93C46/56/57/66/86 are 1K/2K/2K/4K/16K-bit

Serial E2PROM memory devices which are configured

as either registers of 16 bits (ORG pin at VCC) or 8 bits

(ORG pin at GND). Each register can be written (or read)

serially by using the DI (or DO) pin. The CAT93C46/56/

57/66/86 are manufactured using Catalyst’s advanced

CMOS E2PROM floating gate technology. The devices

are designed to endure 1,000,000 program/erase cycles

and have a data retention of 100 years. The devices are

available in 8-pin DIP, 8-pin SOIC or 8-pin TSSOP

packages.

PIN CONFIGURATION

DIP Package (P)

SOIC Package (J)

CS 1

SK 2

DI 3

DO 4

8 VCC

NC (PE*) 1

7 NC (PE*)

VCC

2

6 ORG

CS 3

5 GND

SK 4

8 ORG

7 GND

6 DO

5 DI

SOIC Package (S) SOIC Package (K)

CS 1

SK 2

DI 3

DO 4

8 VCC

CS 1

7 NC (PE*) SK 2

6 ORG

DI 3

5 GND

DO 4

8 VCC

7 NC (PE*)

6 ORG

5 GND

TSSOP Package (U)

CS 1

SK 2

DI 3

DO 4

8

7

6

5

VCC

NC (PE*)

ORG

GND

*Only For 93C86

PIN FUNCTIONS

Pin Name

Function

CS Chip Select

SK Clock Input

DI Serial Data Input

DO Serial Data Output

VCC

GND

+1.8 to 6.0V Power Supply

Ground

ORG

Memory Organization

NC No Connection

PE* Program Enable

Note: When the ORG pin is connected to VCC, the X16 organiza

tion is selected. When it is connected to ground, the X8 pin

is selected. If the ORG pin is left unconnected, then an

internal pullup device will select the X16 organization.

BLOCK DIAGRAM

VCC

GND

ORG

MEMORY ARRAY

ORGANIZATION

DATA

REGISTER

DI

MODE DECODE

CS LOGIC

PE*

CLOCK

SK GENERATOR

93C46/56/57/66/86

F01

ADDRESS

DECODER

OUTPUT

BUFFER

DO

93C46/56/57/66/86 F02

© 1998 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

1

Doc. No. 25056-00 2/98 M-1

1 page

93C46/56/57/66/86

DEVICE OPERATION

The CAT93C46/56(57)66/86 is a 1024/2048/4096/

16,384-bit nonvolatile memory intended for use with

industry standard microprocessors. The CAT93C46/56/

57/66/86 can be organized as either registers of 16 bits

or 8 bits. When organized as X16, seven 9-bit instruc-

tions for 93C46; seven 10-bit instructions for 93C57;

seven 11-bit instructions for 93C56 and 93C66; seven

13-bit instructions for 93C86; control the reading, writing

and erase operations of the device. When organized as

X8, seven 10-bit instructions for 93C46; seven 11-bit

instructions for 93C57; seven 12-bit instructions for

93C56 and 93C66: seven 14-bit instructions for 93C86;

control the reading, writing and erase operations of the

device. The CAT93C46/56/57/66/86 operates on a single

power supply and will generate on chip, the high voltage

required during any write operation.

Instructions, addresses, and write data are clocked into

the DI pin on the rising edge of the clock (SK). The DO

pin is normally in a high impedance state except when

reading data from the device, or when checking the

ready/busy status after a write operation.

The ready/busy status can be determined after the start

of a write operation by selecting the device (CS high) and

polling the DO pin; DO low indicates that the write

operation is not completed, while DO high indicates that

the device is ready for the next instruction. If necessary,

the DO pin may be placed back into a high impedance

state during chip select by shifting a dummy “1” into the

DI pin. The DO pin will enter the high impedance state on

the falling edge of the clock (SK). Placing the DO pin into

the high impedance state is recommended in applica-

tions where the DI pin and the DO pin are to be tied

together to form a common DI/O pin.

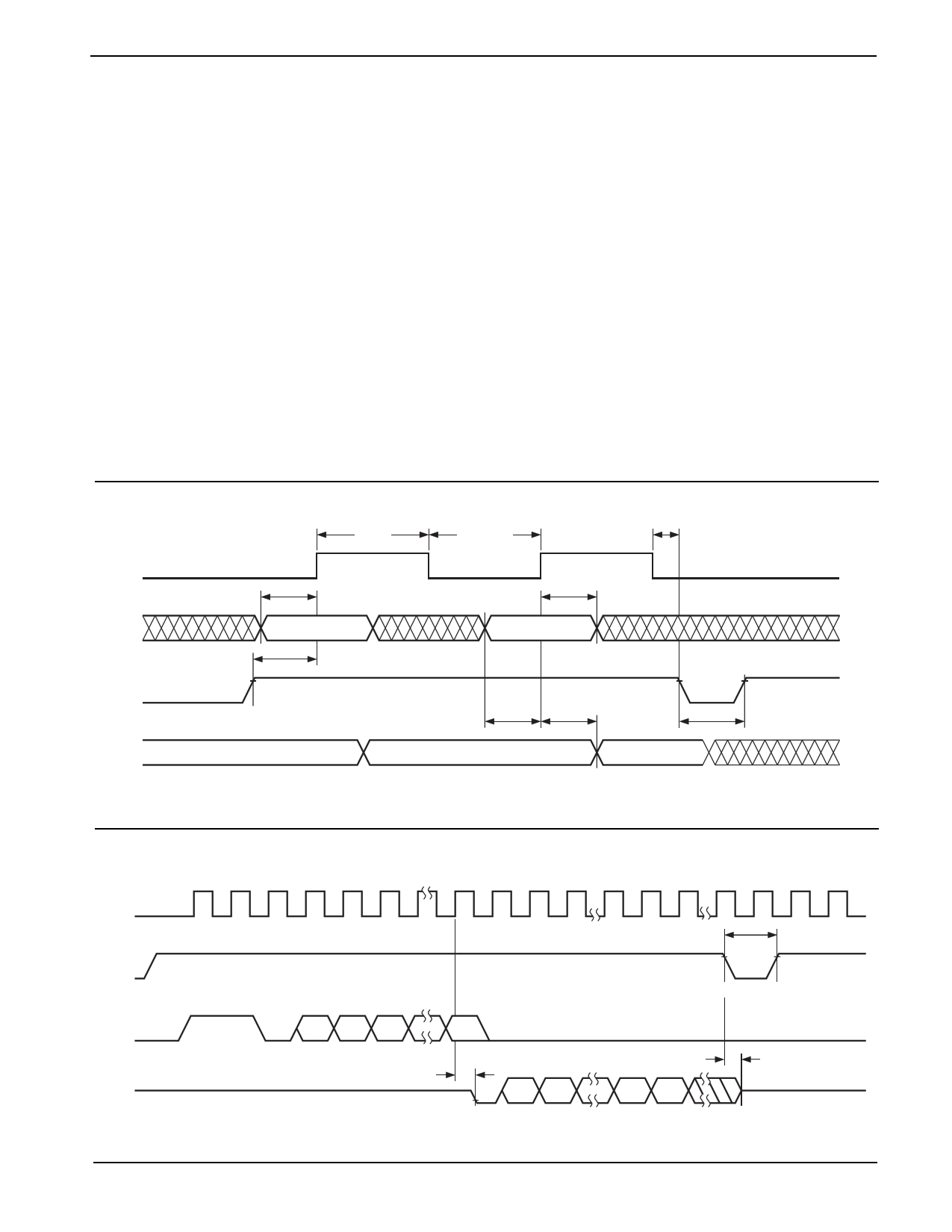

Figure 1. Sychronous Data Timing

tSKHI

SK

tDIS

DI VALID

tCSS

CS

DO

tSKLOW

VALID

tDIH

tCSH

tDIS

tPD0,tPD1

DATA VALID

tCSMIN

93C46/56/57/66/86 F03

Figure 2a. Read Instruction Timing (93C46)

SK

CS

AN AN–1

DI

11

0

A0

HIGH-Z

tPD0

DO 0

DN DN–1

5

tCS

STANDBY

tHZ

D1 D0

HIGH-Z

93C46/56/57/66/86 F04

Doc. No. 25056-00 2/98 M-1

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet CAT93C66.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CAT93C66 | 1K/2K/2K/4K/16K-Bit Microwire Serial E2PROM | Catalyst Semiconductor |

| CAT93C66 | 4 kb Microwire Serial CMOSEEPROM | ON Semiconductor |

| CAT93C6611 | Supervisory Circuits with Microwire Serial CMOS E2PROM/ Precision Reset Controller and Watchdog Timer | Catalyst Semiconductor |

| CAT93C6612 | Supervisory Circuits with Microwire Serial CMOS E2PROM/ Precision Reset Controller and Watchdog Timer | Catalyst Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |