|

|

PDF ISL8702 Data sheet ( Hoja de datos )

| Número de pieza | ISL8702 | |

| Descripción | Adjustable Quad Sequencer | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL8702 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

®

Data Sheet

ISL8700, ISL8701, ISL8702

March 21, 2008

FN9250.2

Adjustable Quad Sequencer

The ISL8700, ISL8701, ISL8702 family of ICs provide four

delay adjustable sequenced outputs while monitoring an

input voltage all with a minimum of external components.

High performance DSP, FPGA, µP and various subsystems

require input power sequencing for proper functionality at

initial power-up and the ISL870x provides this function while

monitoring the distributed voltage for over and undervoltage

compliance.

The ISL8700 and ISL8701 operate over the +2.5V to +24V

nominal voltage range, whereas the ISL8702 operates over

the +2.5V to +12V nominal voltage range. All three have a

user adjustable time from UV and OV voltage compliance to

sequencing start via an external capacitor when in auto start

mode and adjustable time delay to subsequent ENABLE

output signal via external resistors.

Additionally, the ISL8702 provides an input for sequencing

on and off operation (SEQ_EN) and for voltage window

compliance reporting (FAULT) over the +2.5V to +12V

voltage range.

Easily daisy chained for more than 4 sequenced signals.

Altogether, the ISL870x provides these adjustable features

with a minimum of external BOM. See Figure 1 for typical

implementation.

Ordering Information

PART NUMBER PART

TEMP. PACKAGE PKG.

(Note)

MARKING RANGE (°C) (Pb-free) DWG. #

ISL8700IBZ* ISL 8700IBZ -40 to +85 14 Ld SOIC M14.15

ISL8701IBZ* ISL 8701IBZ -40 to +85 14 Ld SOIC M14.15

ISL8702IBZ* ISL 8702IBZ -40 to +85 14 Ld SOIC M14.15

ISL870xEVAL1 Evaluation Platform

*Add “-T” suffix for tape and reel. Please refer to TB347 for details

on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ

special Pb-free material sets; molding compounds/die attach

materials and 100% matte tin plate PLUS ANNEAL - e3 termination

finish, which is RoHS compliant and compatible with both SnPb and

Pb-free soldering operations. Intersil Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed

the Pb-free requirements of IPC/JEDEC J STD-020.

Features

• Adjustable Delay to Subsequent Enable Signal

• Adjustable Delay to Sequence Auto Start

• Adjustable Distributed Voltage Monitoring

• Undervoltage and Overvoltage Adjustable Delay to Auto

Start Sequence

• I/O Options

ENABLE (ISL8700, ISL8702) and ENABLE# (ISL8701)

SEQ_EN (ISL8702)

• Voltage Compliance Fault Output

• Pb-Free (RoHS Compliant)

Applications

• Power Supply Sequencing

• System Timing Function

2.5V TO 24V (2.5V TO 12V FOR ISL8702)

Ru VIN ENABLE_A

SEQ_EN*

ENABLE_B

ENABLE_C

UV ENABLE_D

Rm

OV

FAULT*

GND TB TC TD TIME

Rl

EN

DC/DC

Vo1

EN

DC/DC

Vo2

EN

DC/DC

Vo3

EN

DC/DC

Vo4

* SEQ_EN and FAULT are not available on ISL8700 and ISL8701

FIGURE 1. ISL870x IMPLEMENTATION

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2006, 2008. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

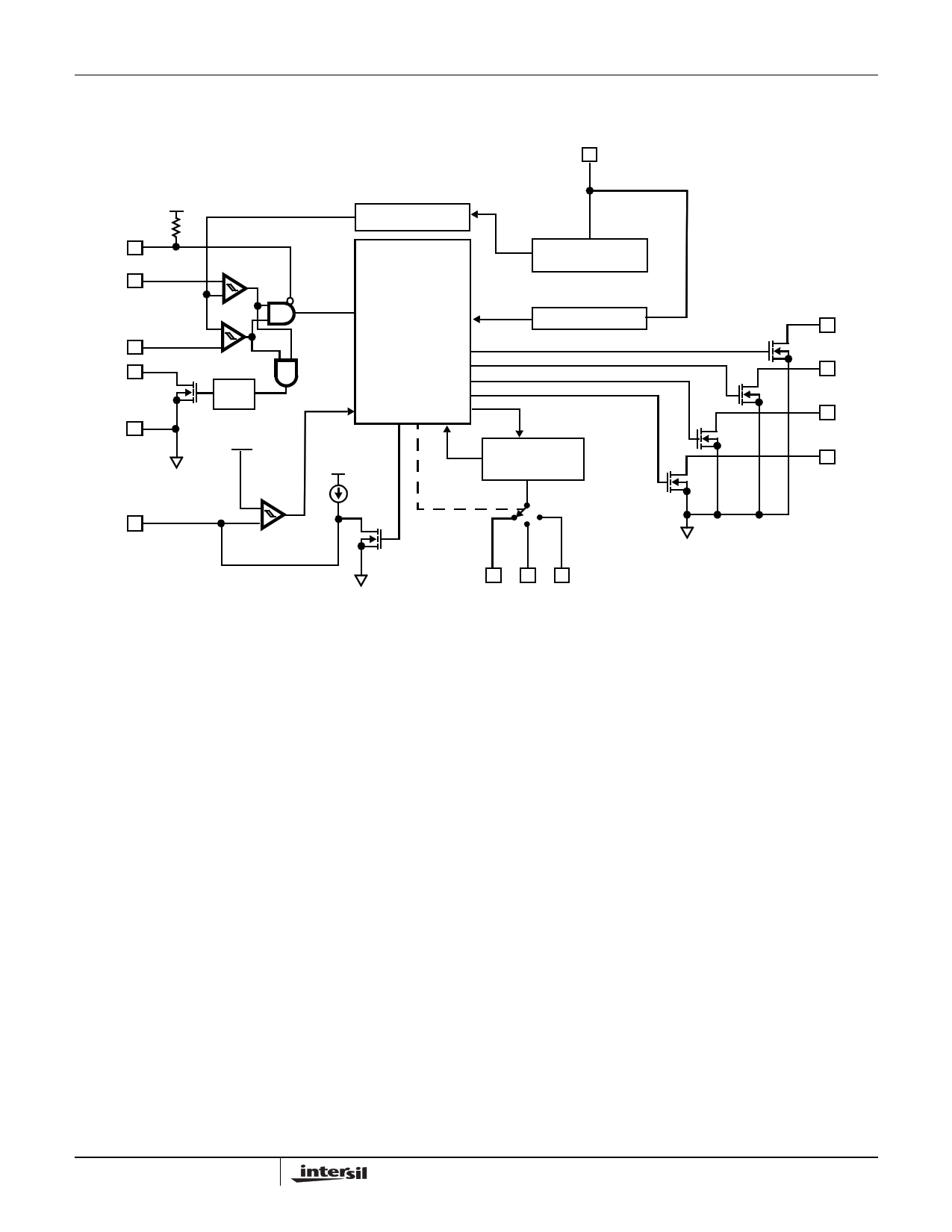

Functional Block Diagram

ISL8700, ISL8701, ISL8702

VIN (2.2V MIN TO 27V MAX, 2.5V TO 12V FOR ISL8702)

SEQ_EN

UV

OV

FAULT

GND

TIME

VIN

VREF

VOLTAGE

1.17V

REFERENCE

+

- eo

+

-

30µs

VTIME_VTH

LOGIC

VIN

2.6µA

VREG INTERNAL VOLTAGE

3.5V

REGULATOR

2.0V VIN POR

PROGRAMMABLE

DELAY TIMER

ENABLE_A

ENABLE_B

ENABLE_C

ENABLE_D

TB TC TD

Functional Description

The ISL870x family of ICs provides four delay adjustable

sequenced outputs while monitoring a single distributed voltage

in the nominal range of 2.5V to 24V for both under and

overvoltage. Only when the voltage is in compliance will the

ISL870x initiate the pre-programmed A-B-C-D sequence of the

ENABLE (ISL8700, ISL8702) or ENABLE# (ISL8701) outputs.

Although this IC has a bias range of 2.5V to 24V (12V for

ISL8702) it can monitor any voltage >1.22V via the external

divider if a suitable bias voltage is otherwise provided.

During initial bias voltage (VIN) application, the ISL8700,

ISL8702 ENABLE outputs are held low once VIN = 1V whereas

the ISL8701 ENABLE# outputs follow the rising VIN. Once

VIN > the VBIAS power-on reset threshold (POR) of 2.0V, VIN

is constantly monitored for compliance via the input voltage

resistor divider and the voltages on the UV and OV pins and

reported by the FAULT output. Internally, voltage regulators

generate 3.5V and 1.17V ±5% voltage rails for internal usage

once VIN > POR. Once UV > 1.22V and with the SEQ_EN pin

high or open, the auto sequence of the four ENABLE

(ENABLE#) outputs begins as the TIME pin charges its external

capacitor with a 2.6µA current source. The voltage on TIME is

compared to the internal reference (VTIME_VTH) comparator

input and when greater than VTIME_VTH the ISL8700, ISL8702

ENABLE_A is released to go high via an external pull-up

5

resistor or a pull-up in a DC/DC convertor enable input, for

example. Conversely, ENABLE#_A output will be pulled low at

this time on an ISL8701. The time delay generated by the

external capacitor is to assure continued voltage compliance

within the programmed limits, as during this time any OV or UV

condition will halt the start-up process. TIME capacitor is

discharged once VTIME_VTH is met.

Once ENABLE_A is active (either released high on the

ISL8700, ISL8702 or pulled low on the ISL8701), a counter is

started and using the resistor on TB as a timing component, a

delay is generated before ENABLE_B is activated. At this time,

the counter is restarted using the resistor on TC as its timing

component for a separate timed delay until ENABLE_C is

activated. This process is repeated for the resistor on TD to

complete the A-B-C-D sequencing order of the ENABLE or

ENABLE# outputs. At any time during sequencing if an OV or

UV event is registered, all four ENABLE outputs will

immediately return to their reset state; low for ISL8700,

ISL8702 and high for ISL8701. CTIME is immediately

discharged after initial ramp-up thus waiting for subsequent

voltage compliance to restart. Once sequencing is complete,

any subsequently registered UV or OV event will trigger an

immediate and simultaneous reset of all ENABLE or ENABLE#

outputs.

FN9250.2

March 21, 2008

5 Page

ISL8700, ISL8701, ISL8702

Application Concerns and Recommendations

When designing the ISL8700 family of products into

applications with low supply voltages such as 3.3V,

additional filtering to help reduce system noise on the

voltage supply input is necessary to ensure proper voltage

sequencing operation. It is important that the

user-programmed UV threshold is set sufficiently above (i.e.

>200mV) the ISL8700 IC’s internal POR level, VIN_POR,

over the entire operating temperature range. Best design

practices include proper decoupling on the supply input (i.e.

at least 1µF) as well as an RC filter that can adequately

suppress noise on the supply in the user’s application,

whereby the resistor should be kept < 13Ω to reduce voltage

loss to the already low biased VIN pin.

Coupling from the ENABLE_X pins to the sensitive UV and

OV pins can cause false OV/UV events to be detected. This

is most relevant for ISL8700, ISL8702 parts due to the

ENABLE_A and OV pins being adjacent. This coupling can

be reduced by adding a ground trace between UV and the

ENABLE/FAULT signals, as shown in Figure 14. The PCB

traces on OV and UV should be kept as small as practical

and the ENABLE_X and FAULT traces should ideally not be

routed under/over the OV/UV traces on different PCB layers

unless there is a ground or power plane in between. Other

methods that can be used to eliminate this issue are by

reducing the value of the resistors in the network connected

to UV and OV (R2, R3, R5 in Figure 15) or by adding small

decoupling capacitors to OV and UV (C2 and C7 in

Figure 15). Both these methods act to reduce the AC

impedance at the nodes, although the latter method acts to

filter the signals, which will also cause an increase in the

time that a UV/OV fault takes to be detected.

When the ISL870x is implemented on a hot swappable card

that is plugged into an always powered passive back plane,

an RC filter is required on the VIN pin to prevent a high dv/dt

transient. With the already existing 1µF decoupling capacitor,

the addition of a small series R (<13Ω) to provide a time

constant >50µs is all that is necessary.

Only the ISL8702 has a VIN limitation of 14V maximum.

GNGDND

PIN 4

PIN 5

FIGURE 14. LAYOUT DETAIL OF GND BETWEEN PINS 4 AND 5

11 FN9250.2

March 21, 2008

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet ISL8702.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL8700 | Adjustable Quad Sequencer | Intersil |

| ISL8700A | (ISL8700A - ISL8705A) Adjustable Quad Sequencer | Intersil Corporation |

| ISL8701 | Adjustable Quad Sequencer | Intersil |

| ISL8701A | (ISL8700A - ISL8705A) Adjustable Quad Sequencer | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |