|

|

PDF IDT709099L Data sheet ( Hoja de datos )

| Número de pieza | IDT709099L | |

| Descripción | HIGH-SPEED 128K x 8 SYNCHRONOUS PIPELINED DUAL-PORT STATIC RAM | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT709099L (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

HIGH-SPEED 128K x 8

SYNCHRONOUS PIPELINED

DUAL-PORT STATIC RAM

IDT709099L

Features

◆ True Dual-Ported memory cells which allow simultaneous

access of the same memory location

◆ High-speed clock to data access

– Commercial: 9/12ns (max.)

– Industrial: 9ns (max.)

◆ Low-power operation

– IDT709099L

Active: 1.2W (typ.)

Standby: 2.5mW (typ.)

◆ Flow-Through or Pipelined output mode on either Port via

the FT/PIPE pins

◆ Counter enable and reset features

◆ Dual chip enables allow for depth expansion without

additional logic

◆ Full synchronous operation on both ports

– 4ns setup to clock and 0ns hold on all control, data, and

address inputs

– Data input, address, and control registers

– Fast 9ns clock to data out in the Pipelined output mode

– Self-timed write allows fast cycle time

– 15ns cycle time, 66.7MHz operation in Pipelined output mode

◆ TTL- compatible, single 5V (±10%) power supply

◆ Industrial temperature range (–40°C to +85°C) is

available for selected speeds

◆ Available in a 100-pin Thin Quad Flatpack (TQFP) package

◆ Green parts available, see ordering information

Functional Block Diagram

R/WL

OEL

CE0L

CE1L

1

0

0/1

R/WR

OER

CE0R

1 CE1R

0

0/1

FT/PIPEL

I/O0L - I/O7L

A16L

A0L

CLKL

ADSL

CNTENL

CNTRSTL

0/1 1

0

I/O

Control

I/O

Control

0 1 0/1

Counter/

Address

Reg.

MEMORY

ARRAY

Counter/

Address

Reg.

FT/PIPER

I/O0R - I/O7R

A16R

A0R

CLKR

ADSR

CNTENR

CNTRSTR

4846 drw 01

©2015 Integrated Device Technology, Inc.

1

APRIL 2015

DSC-4846/8

1 page

IDT709099L

High-Speed 128K x 8 Synchronous Pipelined Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

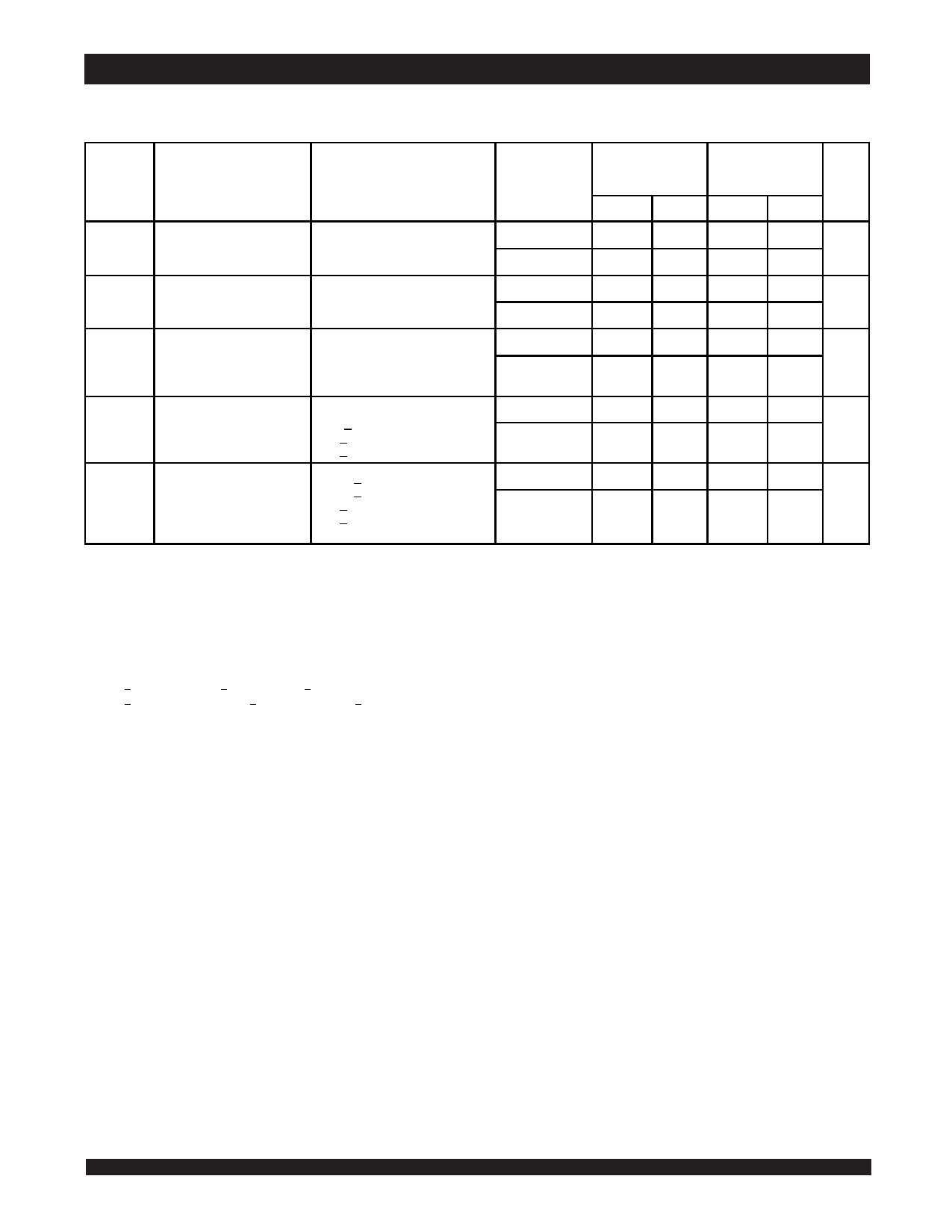

DC Electrical Characteristics Over the Operating

Temperature and Supply Voltage Range(3) (VCC = 5V ± 10%)

709099L9

Com'l

& Ind

709099L12

Com'l Only

Symbol

Parameter

Test Condition

Version

Typ.(4) Max. Typ.(4) Max. Unit

ICC Dynamic Operating

Current

(Both Ports Active)

CEL and CER= VIL

Outputs Disabled

f = fMAX(1)

COM'L L

250

400

230

355 mA

IND

L 300 430 ____

____

ISB1 Standby Current

(Both Ports - TTL

Level Inputs)

CEL = CER = VIH

f = fMAX(1)

COM'L L

80

135

70

110 mA

IND

L 95

160

____

____

ISB2 Standby Current

(One Port - TTL

Level Inputs)

CE"A" = VIL and

CE"B" = VIH(3)

Active Port Outputs

Disabled, f=fMAX(1)

COM'L L

175

275

150

240 mA

IND

L 195 295

____

____

ISB3 Full Standby Current

(Both Ports -

CMOS Level Inputs)

Both Ports CER and

CEL > VCC - 0.2V

VIN > VCC - 0.2V or

VIN < 0.2V, f = 0(2)

COM'L L

0.5

3.0

0.5

3.0 mA

IND

L 0.5 6.0 ____ ____

ISB4 Full Standby Current

(One Port -

CMOS Level Inputs)

CE"A" < 0.2V and

COM'L L 170 270

CE"B" > VCC - 0.2V(5)

VIN > VCC - 0.2V or

IND L

VIN < 0.2V, Active Port

190 290

Outputs Disabled, f = fMAX(1)

140

____

225

____

mA

NOTES:

4846 tbl 09

1. At f = fMAX, address and control lines (except Output Enable) are cycling at the maximum frequency clock cycle of 1/tCYC, using "AC TEST CONDITIONS" at input levels of

GND to 3V.

2. f = 0 means no address, clock, or control lines change. Applies only to input at CMOS level standby.

3. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

4. Vcc = 5V, TA = 25°C for Typ, and are not production tested. ICC DC(f=0) = 150mA (Typ).

5. CEX = VIL means CE0X = VIL and CE1X = VIH

CEX = VIH means CE0X = VIH or CE1X = VIL

CEX < 0.2V means CE0X < 0.2V and CE1X > VCC - 0.2V

CEX > VCC - 0.2V means CE0X > VCC - 0.2V or CE1X < 0.2V

"X" represents "L" for left port or "R" for right port.

6.542

5 Page

IDT709099L

High-Speed 128K x 8 Synchronous Pipelined Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

Timing Waveform of Flow-Through Read-to-Write-to-Read (OE = VIL)(3)

tCYC1

tCH1

tCL1

CLK

CE0

CE1

R/W

tSC tHC

tSW tHW

tSW tHW

(4)

ADDRESS

An

tSA tHA

An +1

DATAIN

DATAOUT

(2)

tCD1

tCD1

Qn

READ

tDC

An + 2

An + 2

An + 3

An + 4

tSD tHD

Dn + 2

Qn + 1

tCKHZ(1)

NOP(5)

WRITE

tCD1

tCD1

Qn + 3

tCKLZ(1)

tDC

READ

4846 drw 13 .

Timing Waveform of Flow-Through Read-to-Write-to-Read (OE Controlled)(3)

tCYC1

tCH1

tCL1

CLK

CE0

CE1

R/W

tSC tHC

tSW tHW

tSW tHW

ADDRESS(4)

DATAIN

DATAOUT

An

tSA tHA

tCD1

(2)

An +1

An + 2

tSD tHD

Dn + 2

tDC

Qn

tOHZ(1)

An + 3

Dn + 3

An + 4

An + 5

tOE

tCD1

(1)

tCKLZ

tCD1

Qn + 4

tDC

OE

READ

WRITE

READ

4846 drw 14

NOTES:

1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

2. Output state (High, Low, or High-impedance is determined by the previous cycle control signals.

3. CE0 and ADS = VIL; CE1 and CNTRST = VIH. "NOP" is "No Operation".

4. Addresses do not have to be accessed sequentially since ADS = VIL constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

5. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

61.412

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet IDT709099L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT709099L | HIGH-SPEED 128K x 8 SYNCHRONOUS PIPELINED DUAL-PORT STATIC RAM | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |