|

|

PDF CA3318CD Data sheet ( Hoja de datos )

| Número de pieza | CA3318CD | |

| Descripción | CMOS Video Speed/ 8-Bit/ Flash A/D Converter | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CA3318CD (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

CA3318

August 1997

CMOS Video Speed,

8-Bit, Flash A/D Converter

Features

• CMOS Low Power with SOS Speed (Typ). . . . . . . . 150mW

• Parallel Conversion Technique

• 15MHz Sampling Rate (Conversion Time) . . . . . . . 67ns

• 8-Bit Latched Three-State Output with Overflow Bit

• Accuracy (Typ) . . . . . . . . . . . . . . . . . . . . . . . . . . ±1 LSB

• Single Supply Voltage . . . . . . . . . . . . . . . . . . 4V to 7.5V

• 2 Units in Series Allow 9-Bit Output

• 2 Units in Parallel Allow 30MHz Sampling Rate

Applications

• TV Video Digitizing (Industrial/Security/Broadcast)

• High Speed A/D Conversion

• Ultrasound Signature Analysis

• Transient Signal Analysis

• High Energy Physics Research

• General-Purpose Hybrid ADCs

• Optical Character Recognition

• Radar Pulse Analysis

• Motion Signature Analysis

• µP Data Acquisition Systems

Description

The CA3318 is a CMOS parallel (FLASH) analog-to-digital

converter designed for applications demanding both low

power consumption and high speed digitization.

The CA3318 operates over a wide full scale input voltage

range of 4V up to 7.5V with maximum power consumption

depending upon the clock frequency selected. When

operated from a 5V supply at a clock frequency of 15MHz,

the typical power consumption of the CA3318 is 150mW.

The intrinsic high conversion rate makes the CA3318 ideally

suited for digitizing high speed signals. The overflow bit

makes possible the connection of two or more CA3318s in

series to increase the resolution of the conversion system. A

series connection of two CA3318s may be used to produce a

9-bit high speed converter. Operation of two CA3318s in

parallel doubles the conversion speed (i.e., increases the

sampling rate from 15MHz to 30MHz).

256 paralleled auto balanced voltage comparators measure

the input voltage with respect to a known reference to

produce the parallel bit outputs in the CA3318.

255 comparators are required to quantize all input voltage

levels in this 8-bit converter, and the additional comparator is

required for the overflow bit.

Ordering Information

PART NUMBER LINEARITY (INL, DNL)

CA3318CE

±1.5 LSB

CA3318CM

±1.5 LSB

CA3318CD

±1.5 LSB

Pinout

SAMPLING RATE

15MHz (67ns)

15MHz (67ns)

15MHz (67ns)

TEMP. RANGE (oC)

-40 to 85

-40 to 85

-40 to 85

PACKAGE

24 Ld PDIP

24 Ld SOIC

24 Ld SBDIP

CA3318

(PDIP, SBDIP, SOIC)

TOP VIEW

(LSB) B1 1

B2 2

B3 3

B4 4

B5 5

B6 6

B7 7

(MSB) B8 8

OVERFLOW 9

1/4R 10

(DIG. GND) VSS 11

(DIG. SUP.) VDD 12

24 VAA+ (ANA. SUP.)

23 3/4R

22 VREF+

21 VIN

20 p

19 PHASE

18 CLK

17 VAA- (ANA. GND)

16 VIN

15 VREF -

14 CE1

13 CE2

PKG. NO.

E24.6

M24.3

D24.6

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

4-9

File Number 3103.1

1 page

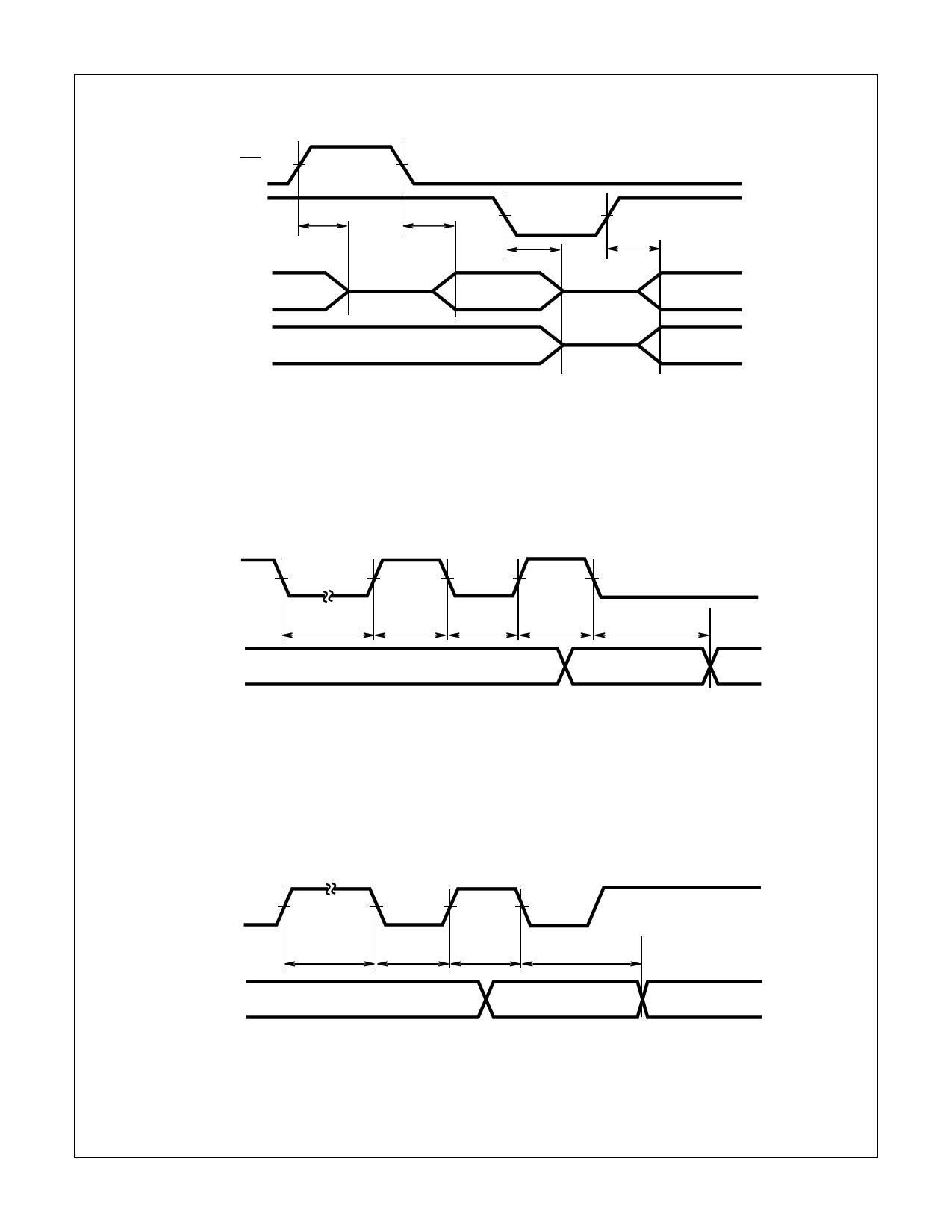

Timing Waveforms (Continued)

CA3318

CE1

CE2

tDIS

tEN

BITS 1 - 8 DATA

OF

HIGH

IMPEDANCE

DATA

tDIS

DATA

tEN

HIGH

IMPEDANCE

HIGH

IMPEDANCE

FIGURE 2. OUTPUT ENABLE TIMING DIAGRAM

DATA

CLOCK

DATA

AUTO

BALANCE

NO MAX

LIMIT

SAMPLE

N

25ns

MIN

AUTO

BALANCE

33ns

MIN

SAMPLE

N+1

25ns

MIN

50ns

MIN

FIGURE 3A. STANDBY IN INDEFINITE AUTO BALANCE (SHOWN WITH PHASE = LOW)

CLOCK

DATA

SAMPLE

N

500ns

MAX

AUTO

BALANCE

33ns

MIN

SAMPLE

N+1

25ns

MIN

AUTO

BALANCE

50ns

TYP

DATA

N-1

SAMPLE

N+2

DATA

N

FIGURE 3B. STANDBY IN SAMPLE (SHOWN WITH PHASE = LOW)

FIGURE 3. PULSE MODE OPERATION

4-13

5 Page

CA3318

+4V TO +6.5V

REFERENCE

4.7µF/10V TANTALUM +

A

CLOCK

SOURCE

OPTIONAL CAP

(SEE TEXT)

0.01µF

INPUT SIGNAL

AMPLIFIER/BUFFER

(SEE TEXT)

A

D

+5V (ANALOG SUPPLY)

VAA+

3/4 REF

BIT 1

BIT 2

VREF+

VIN

1/2 REF

PHASE

BIT 3

BIT 4

BIT 5

BIT 6

CLK

BIT 7

VAA-

VIN

VREF-

CE1

BIT 8

OVF

1/4 REF

VSS

CE2

VDD

CA3318

DIGITAL

OUTPUT

D

+

4.7µF

TANTALUM/10V

A

+5V (DIGITAL SUPPLY)

FIGURE 14. TYPICAL CIRCUIT CONFIGURATION FOR THE CA3318 WITH NO LINEARITY ADJUST

SIGNAL

SOURCE

SIGNAL

GROUND

AMP

REF

VIN

VIN

OUTPUT

DRIVERS

VREF+

TO

DIGITAL

SYSTEM

REFERENCE

TAPS

VAA+

VDD

VREF -

VAA-

VSS

- ANALOG +

SUPPLIES

VAA

SUPPLY

VDD

SUPPLY

FIGURE 15. TYPICAL SYSTEM GROUNDING/BYPASSING

SYSTEM

DIGITAL

GROUND

75Ω

1VP-P

VIDEO

INPUT

75Ω

+8V

10Ω

14 7

11 8

5pF 9 CA3450

3 13

12

45

6

0.001µF

0.001µF

10Ω

390

16

A/D FLASH

INPUT

21

10Ω 750

110

NOTE: Ground-planing and tight layout

are extremely important.

-4V

0.1

0V TO -10V

OFFSET SOURCE

RS < 10Ω

FIGURE 16. TYPICAL HIGH BANDWIDTH AMPLIFIER FOR DRIVING THE CA3318

4-19

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet CA3318CD.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CA3318CD | CMOS Video Speed/ 8-Bit/ Flash A/D Converter | Intersil Corporation |

| CA3318CE | CMOS Video Speed/ 8-Bit/ Flash A/D Converter | Intersil Corporation |

| CA3318CM | CMOS Video Speed/ 8-Bit/ Flash A/D Converter | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |